Principes de base des FPGA : présentation et rôle des FPGA

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-11-14

Les solutions de traitement optimales reposent généralement sur la combinaison de processeurs RISC, de microprocesseurs CISC, de processeurs graphiques et de FPGA, sur des FPGA seuls ou sur des FPGA intégrant des cœurs de processeurs matériels dans leur structure. Cependant, beaucoup de concepteurs ne connaissent ni les capacités des FPGA, ni leur évolution, ni leur utilisation. Cet article, première partie d'une série en cinq parties, traite des principes de base des FPGA et présente des solutions d'exemple des principaux fournisseurs. Les 2e partie, 3e partie, 4e partie et 5e partie porteront sur les gammes de dispositifs FPGA et les outils de conception proposés par Lattice Semiconductor, Microchip, Altera et Xilinx.

Les concepteurs sont constamment à la recherche de moyens leur permettant de structurer leurs systèmes pour offrir une solution informatique optimale répondant à toutes les exigences de leur application. Dans beaucoup de situations, cette solution optimale nécessite généralement l'utilisation de réseaux de portes programmables par l'utilisateur (FPGA), mais de nombreux concepteurs ne connaissent pas assez les capacités de ces dispositifs ni comment les intégrer.

Cet article décrit brièvement des scénarios de conception dans lesquels il peut être utile d'utiliser des FPGA. Il étudie ensuite les principes de base de leur fonctionnement avant de présenter quelques solutions et kits de développements FPGA intéressants.

Pourquoi utiliser des FPGA ?

Il existe un large éventail d'applications informatiques, chacune pouvant être mieux servie par une approche différente, y compris des microprocesseurs (MPU), des microcontrôleurs (MCU) et des processeurs graphiques prêts à l'emploi, des FPGA et des systèmes sur puce (SoC) personnalisés. Le choix de l'une de ces options requiert l'étude minutieuse des exigences et des considérations relatives à l'application.

Par exemple, si des concepteurs travaillent sur des équipements à la pointe de la technologie, comme les stations de base 5G, ils doivent garder à l'esprit que les normes et les protocoles sous-jacents ne cessent d'évoluer. Cela signifie que les concepteurs doivent réagir rapidement et efficacement à toute modification relative aux spécifications qu'ils ne maîtrisent pas forcément.

Ils ont aussi besoin de flexibilité pour faire face à toute modification future des normes et des protocoles qui surviennent une fois que les systèmes ont été déployés sur site. Il est aussi nécessaire d'être capable de résoudre tout bogue inattendu dans les fonctionnalités système ou les failles dans le système de sécurité, de modifier les fonctionnalités existantes ou d'ajouter de nouvelles fonctionnalités afin d'étendre la durée de vie du système.

Alors que de meilleures performances sont généralement atteintes grâce à un SoC, emprunter cette voie coûte cher et prend du temps. De plus, tout algorithme implémenté dans la structure de la puce ne peut fondamentalement pas être modifié. Ce manque de flexibilité devient problématique au vu des éléments à prendre en considération soulignés ci-dessus. Afin de trouver le juste milieu entre performances et flexibilité optimales, il est nécessaire d'emprunter une autre voie. Cette autre voie est souvent fournie par des FPGA, par la combinaison de microcontrôleurs/microprocesseurs et de FPGA, ou par des FPGA intégrant des cœurs de processeur matériels dans leur structure.

Présentation des FPGA

Il s'agit d'une question complexe, car les FPGA signifient des choses différentes selon les personnes. De plus, il existe de nombreux types de FPGA différents, chacun intégrant différentes combinaisons de capacités et de fonctions.

Au cœur de tout FPGA, la représentation du « domaine des FPGA », se trouve une structure programmable, qui est présentée sous forme d'un réseau de blocs logiques programmables (Figure 1a). Chacun de ces blocs logiques contient une collection d'éléments, y compris une table de correspondance (LUT), un multiplexeur et un registre, pouvant tous être configurés (programmés) pour s'adapter aux besoins (Figure 2).

Figure 1 : Les FPGA les plus simples contiennent uniquement une structure programmable et des E/S à usage général configurables (a), des architectures différentes qui étendent cette structure principale avec des blocs SRAM, des PLL, des gestionnaires d'horloges (b), des blocs DSP et des interfaces SERDES (c), ainsi que des cœurs de processeurs matériels et des périphériques (d). (Source de l'image : Max Maxfield)

Figure 1 : Les FPGA les plus simples contiennent uniquement une structure programmable et des E/S à usage général configurables (a), des architectures différentes qui étendent cette structure principale avec des blocs SRAM, des PLL, des gestionnaires d'horloges (b), des blocs DSP et des interfaces SERDES (c), ainsi que des cœurs de processeurs matériels et des périphériques (d). (Source de l'image : Max Maxfield)

Figure 2 : Chaque bloc logique programmable contient un ensemble d'éléments, y compris une table de correspondance, un multiplexeur et un registre, pouvant tous être configurés (programmés) pour s'adapter aux besoins. (Source de l'image : Max Maxfield)

Figure 2 : Chaque bloc logique programmable contient un ensemble d'éléments, y compris une table de correspondance, un multiplexeur et un registre, pouvant tous être configurés (programmés) pour s'adapter aux besoins. (Source de l'image : Max Maxfield)

Beaucoup de FPGA utilisent des tables de correspondance à quatre entrées pouvant être configurées pour implémenter une fonction logique à quatre entrées. Afin de mieux prendre en charge les vastes chemins de données employés dans certaines applications, certains FPGA offrent des tables de correspondance à 6, 7 ou 8 entrées. La sortie de la table de correspondance est directement connectée à l'une des sorties du bloc logique et à l'une des sorties du multiplexeur. L'autre entrée du multiplexeur est directement connectée à une entrée du bloc logique (e). Le multiplexeur peut être configuré pour choisir l'une ou l'autre de ces entrées.

La sortie du multiplexeur alimente l'entrée du registre. Chaque registre peut être configuré pour fonctionner en tant que bascule déclenchée par front ou verrou sensible au niveau (cela étant dit, l'utilisation d'une logique asynchrone sous forme de verrou dans les FPGA n'est pas recommandée). Chaque horloge (ou activation) du registre peut être configurée pour générer une sortie active haute ou active basse. Le niveau actif des entrées de définition/réinitialisation peut également être configuré.

Ces blocs logiques peuvent être pensés en tant qu'« îlots de logique programmable » flottant dans « une mer d'interconnexion programmable ». L'interconnexion peut être configurée pour connecter une sortie de tout bloc logique à une entrée d'un ou de plusieurs autres blocs logiques. De même, les entrées primaires vers le FPGA peuvent être connectées aux entrées de n'importe quel bloc logique, et les sorties de n'importe quel bloc logique peuvent être utilisées pour activer les sorties primaires du dispositif.

Concernant les entrées/sorties à usage général (GPIO) primaires, elles sont présentées dans des batteries (groupes), où chaque batterie peut être configurée pour prendre en charge une norme d'interface différente, comme LVCMOS, LVDS, LVTTL, HSTL ou SSTL. De plus, l'impédance des entrées peut être configurée, tout comme la vitesse de balayage des sorties.

L'étape suivante de la conception d'un FPGA inclut des composants, comme des blocs SRAM, appelés RAM bloc (BRAM), des boucles à verrouillage de phase (PLL) et des gestionnaires d'horloge (Figure 1b). Des blocs de traitement numérique des signaux (DSP) (tranches DSP) peuvent également être ajoutés. Ils contiennent des multiplicateurs configurables et un additionneur configurable qui leur permettent d'effectuer des opérations multiplication-accumulation (MAC) (Figure 1c).

Les blocs SERDES haute vitesse constituent une autre fonctionnalité FPGA courante et peuvent prendre en charge des interfaces série gigabit. Il est important de noter que tous les FPGA ne prennent pas en charge l'ensemble des fonctionnalités mentionnées ci-dessus. D'autres FPGA offrent différents ensembles de fonctionnalités adaptés à différents marchés et applications.

La structure programmable d'un FPGA peut être utilisée pour implémenter toute fonction logique ou tout ensemble de fonctions souhaité, jusqu'à un cœur de processeur ou même plusieurs cœurs. Si ces cœurs sont implémentés dans une structure programmable, ils sont appelés « cœurs logiciels ». En comparaison, certains FPGA, généralement appelés FPGA SoC, contiennent un ou plusieurs processeurs à « cœur matériel », implémentés directement dans la puce (Figure 1d). Ces cœurs de processeur matériels peuvent inclure des unités en virgule flottante (FPU) et un cache L1/L2.

De même, les fonctions d'interfaces périphériques comme CAN, I2C, SPI, UART et USB peuvent être implémentées sous forme de cœurs logiciels dans la structure programmable, mais beaucoup de FPGA les intègrent sous forme de cœurs matériels dans la puce. Les communications entre les cœurs de processeur, les fonctions d'interface et la structure programmable sont généralement organisées grâce à des bus haute vitesse comme AMBA et AXI.

Les premiers FPGA, qui ont été présentés sur le marché par Xilinx en 1985, contenaient uniquement un réseau de 8 × 8 blocs logiques programmables (aucun bloc RAM, aucun bloc DSP, etc.). En comparaison, les FPGA haut de gamme d'aujourd'hui contiennent des centaines de milliers de blocs logiques, des milliers de blocs DSP et des mégabits de RAM. Au total, ils peuvent contenir des milliards de transistors, ce qui représente des dizaines de millions de portes équivalentes (par exemple, des portes NAND à deux entrées).

Technologies de configuration alternatives

Pour déterminer les fonctions des blocs logiques et le routage de l'interconnexion, des cellules de configuration sont utilisées. Elles sont visibles sous forme de commutateurs 0/1 (off/on). Ces cellules sont également utilisées pour configurer la norme d'interface GPIO, l'impédance d'entrée, la vitesse de balayage de sortie, etc. Selon le FPGA, ces cellules de configuration peuvent être implémentées à l'aide de l'une de ces trois technologies :

- Anti-fusible : Ces cellules de configuration sont programmables une seule fois (OTP), ce qui signifie qu'une fois que le dispositif a été programmé, il n'est pas possible de revenir en arrière. Ces dispositifs se limitent généralement aux applications spatiales et haute sécurité. Comme ils sont vendus en petite quantité, leur prix est élevé et ils représentent une option de conception coûteuse.

- Flash : Tout comme les cellules de configuration anti-fusibles, les cellules Flash ne sont pas volatiles. Contrairement aux cellules anti-fusibles, les cellules Flash peuvent être reprogrammées au besoin. Les cellules de configuration Flash sont tolérantes aux radiations, elles conviennent ainsi aux applications spatiales (avec quelques modifications tout de même apportées à leurs couches de métallisation supérieures et à leur boîtier).

- SRAM : Dans ce cas, les données de configuration sont stockées dans une mémoire externe d'où elles sont chargées chaque fois que le FPGA est mis sous tension (ou lorsque cela est recommandé dans le cas de scénarios de configuration dynamique).

Les FPGA aux cellules de configuration anti-fusibles ou Flash présentent les avantages suivants : ils sont instantanés et consomment peu d'énergie. Cependant, ces technologies présentent l'inconvénient de nécessiter des étapes de traitement supplémentaires en plus du processus CMOS sous-jacent utilisé pour créer le reste de la puce.

Les FPGA aux cellules de configuration SRAM présentent les avantages suivants : ils sont fabriqués à l'aide du même processus CMOS que le reste de la puce et offrent de hautes performances, car ces composants ont généralement une ou deux générations d'avance par rapport aux technologies anti-fusible et Flash. Le principal inconvénient est que les cellules de configuration SRAM consomment plus d'énergie que leurs équivalents anti-fusible et Flash (pour le même nœud technologique) et sont sensibles aux perturbations par une particule isolée (SEU) causées par des radiations.

Pendant longtemps, en raison de ce dernier point, les FPGA SRAM étaient considérés comme des composants ne pouvant pas convenir aux applications aérospatiales et spatiales. Plus récemment, des stratégies d'atténuation spéciales ont été employées, ce qui a permis d'utiliser les FPGA SRAM sur des systèmes tels que le rover Curiosty envoyé sur Mars, en complément de leurs homologues Flash.

L'utilisation des FPGA offre de la flexibilité

Les FPGA sont utilisés dans de nombreuses applications. Ils sont particulièrement utiles pour implémenter des fonctions d'interfaçage intelligent, de commande moteur, d'accélération algorithmique et de calcul haute performance (HPC), de traitement d'images et de vidéos, de vision artificielle, d'intelligence artificielle (IA), d'apprentissage automatique (ML), d'apprentissage profond (DL) de radar, de formation de faisceau, de stations de base et de communications.

Un exemple simple est de fournir une interface intelligente entre d'autres dispositifs utilisant différentes normes d'interfaces ou différents protocoles de communication. Pensez à un système existant contenant un processeur d'application connecté à un capteur de caméra et à un dispositif d'affichage utilisant des interfaces héritées (Figure 3a).

Figure 3 : Un FPGA peut être utilisé pour fournir une interface intelligente entre d'autres dispositifs qui utilisent différentes normes d'interface ou différents protocoles de communication, étendant ainsi la durée de vie des conceptions existantes utilisant des dispositifs hérités. (Source de l'image : Max Maxfield)

Figure 3 : Un FPGA peut être utilisé pour fournir une interface intelligente entre d'autres dispositifs qui utilisent différentes normes d'interface ou différents protocoles de communication, étendant ainsi la durée de vie des conceptions existantes utilisant des dispositifs hérités. (Source de l'image : Max Maxfield)

Maintenant, imaginez que les créateurs du système souhaitent mettre à niveau le capteur de caméra et le dispositif d'affichage en les remplaçant par des composants plus modernes qui seraient plus légers, moins coûteux et qui consommeraient moins d'énergie. Le seul problème est que l'un ou l'ensemble de ces nouveaux périphériques pourraient utiliser une norme d'interface moderne qui n'est pas prise en charge par le processeur d'application (AP) d'origine. Ou bien, ils pourraient prendre en charge un protocole de communication complètement différent, comme l'interface MIPI (Mobile Industry Processor Interface). Dans ce cas, l'utilisation d'un FPGA avec sa capacité à prendre en charge plusieurs normes E/S, associée à quelques cœurs IP MIPI logiciels, fournirait une solution de mise à niveau rapide, peu coûteuse et sans risque (Figure 3b).

Comme autre exemple d'application, pensez à certaines tâches à calcul intensif comme le traitement des signaux nécessaire à l'implémentation d'un système radar ou à la formation de faisceau dans une station de base de communications. Les processeurs traditionnels et leurs architectures von Neumann ou Harvard conviennent très bien pour certaines tâches, mais moins pour d'autres qui nécessitent de répéter la même séquence d'opérations. Cela est dû au fait qu'un cœur de processeur unique exécutant un seul thread ne peut exécuter qu'une seule instruction à la fois (Figure 4a).

Figure 4 : Contrairement aux microprocesseurs dans lesquels une seule instruction peut être exécutée à la fois (séquentiellement), plusieurs blocs fonctionnels dans un FPGA peuvent fonctionner en même temps (simultanément). Les FPGA peuvent également implémenter des algorithmes appropriés de façon massivement parallèle. (Source de l'image : Max Maxfield)

Figure 4 : Contrairement aux microprocesseurs dans lesquels une seule instruction peut être exécutée à la fois (séquentiellement), plusieurs blocs fonctionnels dans un FPGA peuvent fonctionner en même temps (simultanément). Les FPGA peuvent également implémenter des algorithmes appropriés de façon massivement parallèle. (Source de l'image : Max Maxfield)

En comparaison, plusieurs fonctions peuvent être exécutées simultanément dans le FPGA, ce qui permet ainsi le chevauchement d'une série d'opérations pour offrir en retour un rendement bien plus important. De même, plutôt que d'effectuer la même opération, disons encore 1000 fois sur 1000 paires de valeurs de données avec le processeur, les mêmes calculs peuvent être effectués de façon massivement parallèle en un seul cycle d'horloge dans le FPGA en instanciant 1000 additionneurs dans une structure programmable (Figure 4b).

Qui sont les fabricants de FPGA ?

Il s'agit d'un domaine en constante évolution. Les deux principaux fabricants de véritables dispositifs haut de gamme offrant les meilleures capacités et performances sont Intel (qui a fait l'acquisition d'Altera) et Xilinx.

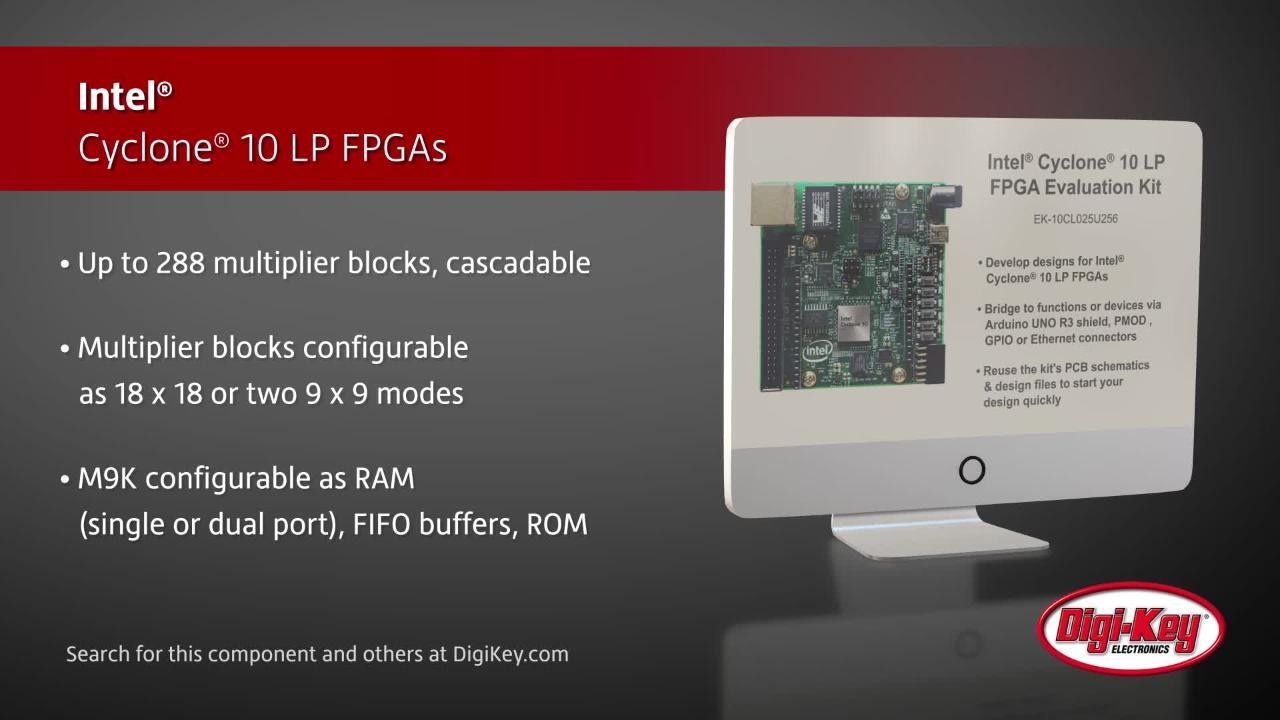

Les offres d'Intel et de Xilinx s'étendent des FPGA bas de gamme aux FPGA SoC haut de gamme. Un autre fournisseur qui cible presque exclusivement les FPGA est Lattice Semiconductor, avec l'accent sur les applications bas de gamme et milieu de gamme. Enfin, Microchip Technology (grâce à ses acquisitions d'Actel, d'Atmel et de Microsemi) fournit désormais plusieurs gammes de FPGA de petite à moyenne taille et des composants bas de gamme de la catégorie des FPGA SoC.

Le choix du meilleur dispositif pour une tâche donnée peut s'avérer difficile, car il existe beaucoup de types de composants, chacun offrant des ressources, des performances, des capacités et des styles de boîtier différents. En voici quelques parfaits exemples : dispositifs Intel, dispositifs Lattice Semiconductor et dispositifs Xilinx.

Conception avec des FPGA

Pour les ingénieurs, la méthode traditionnelle de conception FPGA consiste à utiliser un langage de description matériel comme Verilog ou VHDL pour capturer l'objectif de la conception. Ces descriptions peuvent tout d'abord être simulées pour vérifier qu'elles répondent aux besoins, puis être traitées dans un outil de synthèse qui génère le fichier de configuration utilisé pour configurer (programmer) le FPGA.

Chaque fournisseur de FPGA propose soit sa propre chaîne d'outils développée en interne, soit une version personnalisée d'un outil provenant d'un fournisseur spécialisé. Dans tous les cas, les outils sont accessibles à partir des sites Web des fournisseurs de FPGA. De plus, il peut exister des versions gratuites ou peu coûteuses de suites d'outils complètes.

Afin de rendre les FPGA plus accessibles aux développeurs logiciels, certains fournisseurs de FPGA proposent désormais des outils HLS (High-Level Synthesis). Ces outils interprètent une description algorithmique du comportement souhaité, capturé à un haut niveau d'abstraction en C, C++ ou OpenCL, et génèrent l'entrée pour alimenter le moteur de synthèse de niveau inférieur.

Pour les concepteurs qui cherchent à se lancer, de nombreuses cartes d'évaluation et de développement sont disponibles, chacune offrant différentes capacités et fonctionnalités. Voici trois exemples : le kit de développement DFR0600 de DFRobot, intégrant un FPGA SoC Zynq-7000 de Xilinx, le DE10 Nano de Terasic Inc, intégrant un FPGA SoC Cyclone V d'Intel et la carte d'évaluation ICE40HX1K-STICK-EVN, intégrant un FPGA iCE40 basse consommation de Lattice Semiconductor.

Les concepteurs prévoyant d'utiliser une carte fille PCIe FPGA pour accélérer les applications s'exécutant sur une carte mère X86 pourront être intéressés par les cartes filles PCIe Alveo, également proposées par Xilinx.

Conclusion

Les solutions de conception optimales reposent généralement sur des FPGA, sur la combinaison de processeurs et de FPGA, et sur des FPGA intégrant des cœurs de processeurs matériels dans leur structure.

Les FPGA ont évolué rapidement au fil des années et sont capables de répondre à de nombreuses exigences de conception en matière de flexibilité, de vitesse de traitement et d'alimentation, ce qui les rend utiles pour une vaste gamme d'applications.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.