Principes de base des FPGA – 4e partie : premiers pas avec les FPGA de Xilinx

Avec la contribution de Rédacteurs nord-américains de DigiKey

2020-04-01

Note de l'éditeur : Les solutions de traitement optimales reposent généralement sur la combinaison de processeurs RISC, de microprocesseurs CISC, de processeurs graphiques et de FPGA, sur des FPGA seuls ou sur des FPGA intégrant des cœurs de processeurs matériels dans leur structure. Cependant, beaucoup de concepteurs ne connaissent ni les capacités des FPGA, ni leur évolution, ni leur utilisation. La 1re partie de cette série en plusieurs parties a fourni une présentation détaillée des FPGA. La 2e partie était axée sur les solutions FPGA de Lattice Semiconductor, et la 3e partie sur les gammes de dispositifs FPGA et les outils de conception de Microchip Technology (plus précisément de sa filiale Microsemi Corporation). Ici, la 4e partie aborde les composants et les outils de Xilinx. La 5e partie examinera les solutions d'Altera.

Comme indiqué dans la 1re partie, les réseaux de portes programmables par l'utilisateur (FPGA) offrent de nombreuses caractéristiques qui en font une ressource informatique inestimable, autonome ou intégrée dans une architecture hétérogène. Cependant, de nombreux concepteurs ne connaissent pas bien les FPGA et ne savent pas comment les intégrer à leurs conceptions.

Pour surmonter cet obstacle, il est possible d'examiner plus en détail les architectures FPGA et les outils associés proposés par les principaux fournisseurs. Cet article étudie les offres de Xilinx.

Présentation détaillée des options FPGA

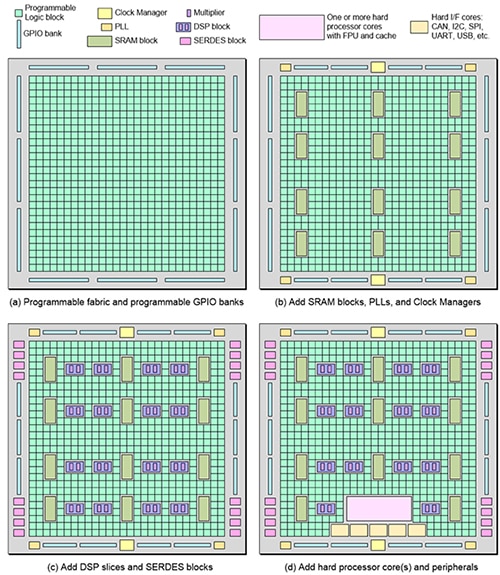

Il existe de nombreux types de FPGA différents sur le marché, chacun intégrant différentes combinaisons de capacités et de fonctions. Au cœur de tout FPGA se trouve une structure programmable. Elle se présente sous forme d'un réseau de blocs logiques programmables, ou éléments logiques (LE) (Figure 1a). L'étape suivante de la conception de la structure FPGA consiste à inclure des composants, comme des blocs SRAM, appelés RAM bloc (BRAM), des boucles à verrouillage de phase (PLL) et des gestionnaires d'horloge (Figure 1b). Des blocs de traitement des signaux numériques (DSP) (appelés « tranches DSP ») et des blocs de sérialiseur/désérialiseur (SERDES) haute vitesse peuvent également être ajoutés (Figure 1c).

Figure 1 : Les FPGA les plus simples contiennent uniquement une structure programmable et des E/S à usage général (GPIO) configurables (a) ; différentes architectures étendent cette structure principale avec des blocs SRAM, des PLL, des gestionnaires d'horloges (b), des blocs DSP et des interfaces SERDES (c), ainsi que des cœurs de processeurs matériels et des périphériques (d). (Source de l'image : Max Maxfield)

Figure 1 : Les FPGA les plus simples contiennent uniquement une structure programmable et des E/S à usage général (GPIO) configurables (a) ; différentes architectures étendent cette structure principale avec des blocs SRAM, des PLL, des gestionnaires d'horloges (b), des blocs DSP et des interfaces SERDES (c), ainsi que des cœurs de processeurs matériels et des périphériques (d). (Source de l'image : Max Maxfield)

Les fonctions d'interfaces périphériques comme CAN, I2C, SPI, UART et USB peuvent être implémentées sous forme de cœurs logiciels dans la structure programmable, mais beaucoup de FPGA les incluent sous forme de cœurs matériels dans la puce. De même, les microprocesseurs peuvent être implémentés sous forme de cœurs logiciels dans la structure programmable ou de cœurs matériels dans la puce (Figure 1d). Les FPGA dotés de cœurs de processeur matériels sont appelés des FPGA de type système sur puce (SoC). D'autres FPGA offrent différents ensembles de fonctions, fonctionnalités, possibilités et capacités adaptés à différents marchés et applications.

Il existe un certain nombre de fournisseurs de FPGA, notamment Altera (qui a été racheté par Intel), Atmel (qui a été racheté par Microchip Technology), Efinix, Lattice Semiconductor, Microsemi (qui a également été racheté par Microchip Technology) et Xilinx.

Tous ces fournisseurs proposent plusieurs gammes de FPGA. Certains proposent des FPGA SoC, d'autres proposent des dispositifs destinés aux applications d'intelligence artificielle (IA) et d'apprentissage automatique (ML), et d'autres encore proposent des dispositifs qui tolèrent les rayonnements et sont destinés à des environnements à rayonnement élevé comme l'espace. Le choix du meilleur dispositif pour une tâche donnée peut s'avérer difficile, car il existe beaucoup de types de composants, chacun offrant des ressources différentes.

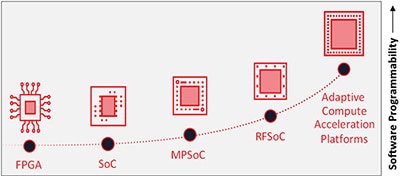

Présentation des FPGA, SoC, MPSoC, RFSoC et ACAP de Xilinx

Les performances et les capacités des dispositifs programmables de Xilinx couvrent des niveaux modestes à extrêmement élevés. Il existe ainsi des FPGA traditionnels, des SoC (structure programmable FPGA avec un seul processeur matériel), des MPSoC (structure programmable FPGA avec plusieurs processeurs matériels), des RFSoC (MPSoC avec capacité RF) et des ACAP (plateformes d'accélération de calcul adaptatives) (Figure 2).

Figure 2 : Au fil du temps, le portefeuille architectural de Xilinx a évolué des simples FPGA contenant uniquement une structure programmable à des dispositifs SoC dans lesquels la structure programmable est renforcée avec un processeur matériel, à des MPSoC dotés de plusieurs processeurs, à des RFSoC dotés de capacités RF, et à la dernière génération d'ACAP qui cible les applications comme l'IA. (Source de l'image : Max Maxfield)

Figure 2 : Au fil du temps, le portefeuille architectural de Xilinx a évolué des simples FPGA contenant uniquement une structure programmable à des dispositifs SoC dans lesquels la structure programmable est renforcée avec un processeur matériel, à des MPSoC dotés de plusieurs processeurs, à des RFSoC dotés de capacités RF, et à la dernière génération d'ACAP qui cible les applications comme l'IA. (Source de l'image : Max Maxfield)

Avec ce portefeuille étendu de produits de Xilinx, les nombreux segments de marché ciblés et la vaste gamme de méthodes de déploiement disponible, il peut s'avérer difficile pour les novices d'avoir une compréhension globale des FPGA.

En ce qui concerne les marchés, Xilinx cible notamment les data centers (calcul, réseau, stockage), les communications (filaires, sans fil), l'aérospatiale et la défense, les applications industrielles, scientifiques et médicales (ISM), les solutions de test, de mesure et d'émulation (TME), et les solutions automobiles, de radiodiffusion et grand public (liste non exhaustive).

Les méthodes de déploiement incluent quant à elles ce que Xilinx appelle les dispositifs à adaptation matérielle (puces, cartes d'évaluation et kits de développement), les systèmes d'extrémité déployables (systèmes sur module [SoM] et cartes d'accélération PCIe), et les FPGA en tant que service (FAAS), qui incluent des technologies d'évaluation et d'exploitation de Xilinx via les principaux fournisseurs cloud, notamment Amazon Web Services (AWS), Alibaba.com et Nimbix.net.

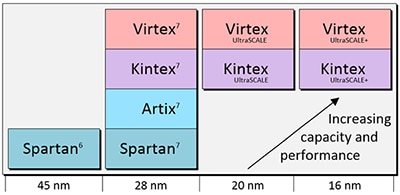

Pour ce qui est des solutions FPGA de Xilinx, il est possible de les classer selon le nœud utilisé pour la technologique de fabrication (Figure 3).

Figure 3 : Les solutions FPGA de Xilinx offrent un portefeuille complet à plusieurs nœuds pour répondre aux exigences de nombreuses applications. (Source de l'image : Max Maxfield)

Figure 3 : Les solutions FPGA de Xilinx offrent un portefeuille complet à plusieurs nœuds pour répondre aux exigences de nombreuses applications. (Source de l'image : Max Maxfield)

Selon l'application cible, les concepteurs peuvent choisir un FPGA bon marché à faible empreinte implémenté avec un ancien nœud technologique, ou choisir un dispositif hautes performances à capacités et à largeur de bande élevées, implémenté avec un nœud technologique plus récent (dans le cas d'une application de mise en réseau de pointe, par exemple).

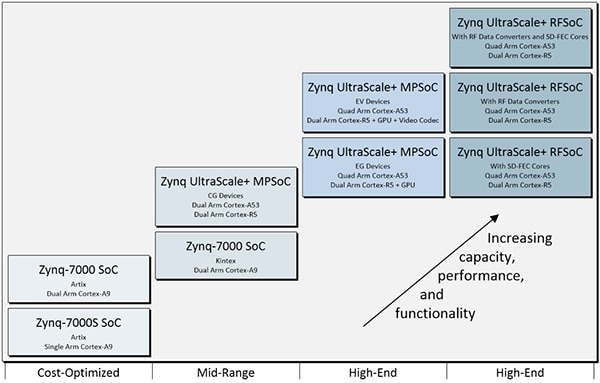

Pour les conceptions qui nécessitent un ou plusieurs cœurs de processeur matériels (et d'autres fonctions renforcées comme des GPU, des codecs et des cœurs de décision pondérée avec correction d'erreur directe [SD-FEC]), Xilinx propose un portefeuille de dispositifs sous le nom générique « Zynq ». Un résumé des solutions SoC, MPSoC et RFSoC Zynq est présenté à la Figure 4. Cette suite de solutions fournit aux concepteurs un large éventail de capacités permettant de simplifier l'optimisation de la puissance, des performances, des coûts et des délais de commercialisation.

Figure 4 : Les solutions SoC, MPSoC et RFSoC de Xilinx intègrent la programmabilité logicielle d'un processeur à la programmabilité matérielle d'un FPGA, ce qui offre aux concepteurs des avantages en termes de performances, de flexibilité et d'évolutivité du système. (Source de l'image : Max Maxfield)

Figure 4 : Les solutions SoC, MPSoC et RFSoC de Xilinx intègrent la programmabilité logicielle d'un processeur à la programmabilité matérielle d'un FPGA, ce qui offre aux concepteurs des avantages en termes de performances, de flexibilité et d'évolutivité du système. (Source de l'image : Max Maxfield)

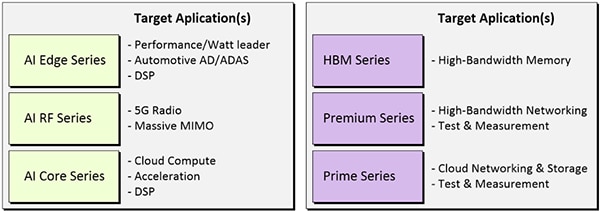

Les solutions les plus récentes de Xilinx sont les dispositifs ACAP de la série Versal, qui sont tous implémentés grâce au nœud technologique de 7 nanomètres (nm). Les ACAP sont des plateformes de calcul hautement intégrées à plusieurs cœurs, capables de s'adapter à des algorithmes évolutifs et variés. Ces plateformes sont personnalisables de manière dynamique au niveau matériel et au niveau logiciel pour s'adapter à de nombreux types d'applications et de charges de travail. Conçues autour d'un réseau sur puce (NoC) programmable, les ACAP sont facilement programmables tant par les concepteurs matériels que par les concepteurs logiciels.

Les nouvelles fonctionnalités des dispositifs Versal incluent des moteurs intelligents (un réseau massif de processeurs vectoriels pour les charges de travail ML et DSP), un NoC programmable basse consommation à largeur de bande élevée et à faible latence qui peut transférer plusieurs téraoctets de données, ainsi qu'un boîtier intégré permettant d'améliorer les performances, l'utilisation et la productivité grâce à une infrastructure de cœur préconçue et à une connectivité système.

Une présentation du portefeuille d'ACAP Versal est fournie à la Figure 5.

Figure 5 : Les ACAP Versal de Xilinx sont des plateformes de calcul hautement intégrées à plusieurs cœurs, capables de s'adapter à des algorithmes évolutifs et variés. Les ACAP sont personnalisables de manière dynamique au niveau matériel et au niveau logiciel pour s'adapter à de nombreux types d'application et de charges de travail. (Source de l'image : Max Maxfield)

Figure 5 : Les ACAP Versal de Xilinx sont des plateformes de calcul hautement intégrées à plusieurs cœurs, capables de s'adapter à des algorithmes évolutifs et variés. Les ACAP sont personnalisables de manière dynamique au niveau matériel et au niveau logiciel pour s'adapter à de nombreux types d'application et de charges de travail. (Source de l'image : Max Maxfield)

Traitée plus en détail dans la section sur les outils de conception, la nouvelle pile logicielle est un différenciateur clé des dispositifs Versal. Elle est destinée aux analystes de données, aux ingénieurs logiciels et aux ingénieurs en conception matérielle traditionnelle.

D'innombrables dispositifs de Xilinx sont désormais disponibles. Citons par exemple le FPGA Artix-7, le FPGA Kintex UltraScale, le FPGA Kintex UltraScale+, le module SoC Zynq-7000 de Trenz Electronic GmbH et le MPSoC Zynq UltraScale+.

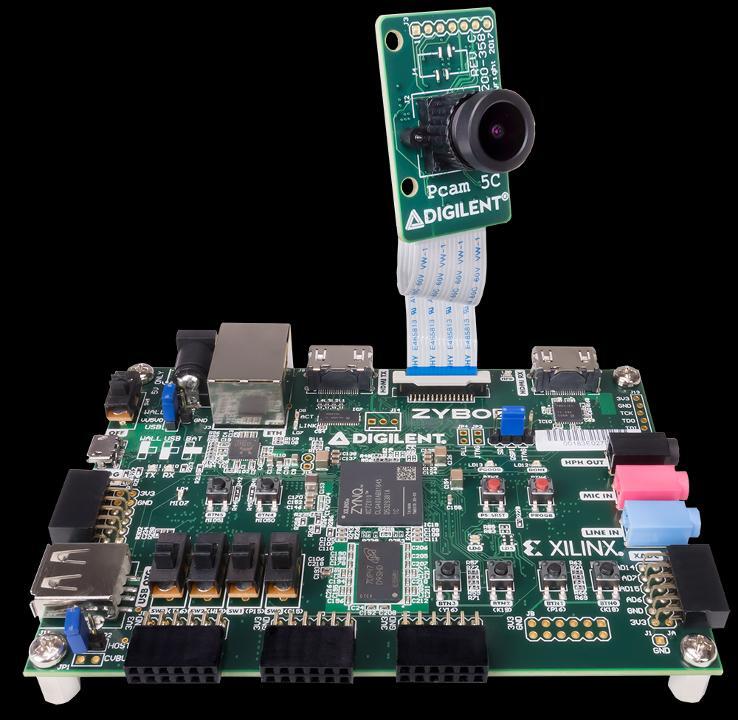

De même, il existe de nombreuses cartes d'évaluation et de développement. Citons par exemple la carte d'évaluation de FPGA Artix-7 de Digilent, la carte d'évaluation de FPGA Kintex UltraScale d'Analog Devices, la carte d'évaluation de FPGA Kintex UltraScale+ de Xilinx, la carte d'évaluation de FPGA SoC Zynq-7000 de Digilent et la carte d'évaluation de FPGA MPSoC Zynq UltraScale+ de Xilinx.

Conception et développement avec des FPGA, SoC et ACAP de Xilinx

Xilinx se démarque vraiment de la concurrence grâce à l'étendue de ses outils et de ses flux de conception, et à leurs capacités.

Dans la 1re partie de cette série sur les FPGA, nous avons expliqué que pour concevoir de manière traditionnelle ces dispositifs, les ingénieurs devaient utiliser un langage de description matérielle (HDL) comme Verilog ou VHDL pour capturer l'intention de la conception à un niveau d'abstraction appelé RTL (Register Transfer Level). Ces descriptions RTL peuvent tout d'abord être simulées pour vérifier qu'elles répondent aux besoins, puis être traitées dans un outil de synthèse qui génère le fichier de configuration utilisé pour programmer le FPGA.

L'étape suivante de l'abstraction consiste à capturer l'intention de la conception à l'aide d'un langage de programmation comme C/C++ ou d'une implémentation spéciale comme SystemC, qui est un ensemble de classes et de macros C++ fournissant une interface de simulation axée sur les événements. Ces dernières facilitent la simulation des processus concurrents, qui sont tous décrits à l'aide d'une syntaxe C++ simple. Ces descriptions peuvent être analysées et profilées en les exécutant comme des programmes normaux, avant d'être envoyées à un moteur de synthèse de haut niveau (HLS) qui génère le RTL transmis au moteur de synthèse standard.

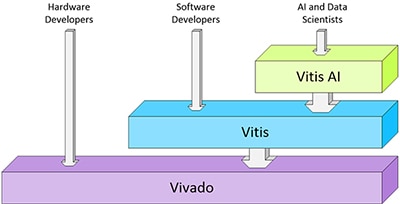

L'ensemble de ce processus est intégré dans la version HLx de la suite de conception Vivado, qui génère le train de bits de configuration à charger dans les dispositifs FPGA, SoC, MPSoC, RFSoC ou ACAP cibles. En plus de permettre aux développeurs matériels d'exploiter une conception en langage C et de la réutiliser de manière optimisée, Vivado permet également de réutiliser des sous-systèmes de propriété intellectuelle, d'automatiser l'intégration et d'accélérer la finalisation de la conception (Figure 6).

Figure 6 : Un aperçu détaillé de la pile d'outils de conception Vivado et Vitis de Xilinx indique la manière dont les utilisateurs peuvent travailler avec les outils aux niveaux d'abstraction les plus appropriés. Les concepteurs matériels utilisent Vivado, les développeurs logiciels utilisent Vitis, et les analystes de données et les spécialistes en IA utilisent Vitis AI. (Source de l'image : Max Maxfield)

Figure 6 : Un aperçu détaillé de la pile d'outils de conception Vivado et Vitis de Xilinx indique la manière dont les utilisateurs peuvent travailler avec les outils aux niveaux d'abstraction les plus appropriés. Les concepteurs matériels utilisent Vivado, les développeurs logiciels utilisent Vitis, et les analystes de données et les spécialistes en IA utilisent Vitis AI. (Source de l'image : Max Maxfield)

Le niveau suivant d'abstraction est pris en charge par la plateforme logicielle unifiée Vitis, qui offre aux développeurs logiciels la possibilité de créer en toute simplicité des applications accélérées. « Au-dessus » de Vitis se trouve Vitis AI, qui permet aux analystes de données et aux spécialistes en IA de travailler au niveau d'abstraction TensorFlow. Vitis AI est une plateforme de développement pour l'inférence IA sur les plateformes matérielles de Xilinx, incluant à la fois des périphériques et des cartes PCIe Alveo. Elle est composée d'une propriété intellectuelle optimisée, d'outils, de bibliothèques, de modèles et de conceptions d'exemple, et est conçue pour exploiter pleinement le potentiel d'accélération IA sur les dispositifs FPGA et ACAP de Xilinx.

Vitis AI alimente Vitis, qui alimente à son tour Vivado. Ce qu'il faut retenir de la Figure 6, c'est que les utilisateurs « voient » uniquement ce qu'ils ont besoin de « voir ». Ainsi, les développeurs matériels « voient » uniquement Vivado, les développeurs logiciels « voient » uniquement Vitis, et les analystes de données et les spécialistes en IA « voient » uniquement Vitis AI. De cette façon, les utilisateurs peuvent travailler avec les outils aux niveaux d'abstraction les plus appropriés.

Le fait de proposer aux développeurs logiciels une suite d'outils comme Vitis, qui les isole du matériel sous-jacent, rend les FPGA accessibles à davantage de développeurs. De même, le fait de proposer aux analystes de données et aux spécialistes en IA une suite d'outils comme Vitis AI, qui leur permet de se concentrer sur leur propre niveau d'abstraction et qui les isole des logiciels sous-jacents, rend les FPGA accessibles à une nouvelle catégorie de développeurs.

En fournissant ces capacités, Xilinx fait figure de pionnier dans l'élévation des outils FPGA à des niveaux d'abstraction toujours plus élevés, qui permettront aux développeurs d'exploiter plus facilement les capacités de ces dispositifs et de les intégrer à leurs prochaines conceptions.

Conclusion

Les solutions de conception de traitement optimales reposent généralement sur des combinaisons de processeurs et de FPGA, sur des FPGA seuls ou sur des FPGA intégrant des cœurs de processeurs matériels dans leur structure. En tant que technologie, les FPGA ont évolué rapidement au fil des années et sont désormais capables de répondre à de nombreuses exigences de conception en matière de flexibilité, de vitesse de traitement et de puissance, ce qui les rend très utiles pour une vaste gamme d'applications s'étendant des interfaces intelligentes à la vision artificielle et à l'intelligence artificielle.

Comme illustré ici, les offres de dispositifs programmables de Xilinx couvrent des niveaux de performances et de capacités modestes à extrêmement élevés. Elles incluent les FPGA traditionnels, les SoC (structure programmable FPGA avec un seul processeur matériel), les MPSoC (structure programmable FPGA avec plusieurs processeurs matériels), les RFSoC (MPSoC avec capacité RF) et les ACAP (plateformes d'accélération de calcul adaptatives).

Pour aider les concepteurs à créer des conceptions avec ces dispositifs, Xilinx propose une suite d'outils répondant aux besoins des développeurs matériels (Vivado), des développeurs logiciels (Vitis), et des analystes de données et des spécialistes en IA (Vitis AI).

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.