Principes de base des FPGA – 5ᵉ partie : premiers pas avec les FPGA d'Intel (Altera)

Avec la contribution de Rédacteurs nord-américains de DigiKey

2020-05-07

Note de l'éditeur : Les solutions de traitement optimales reposent généralement sur la combinaison de processeurs RISC, de microprocesseurs CISC, de processeurs graphiques et de FPGA, sur des FPGA seuls ou sur des FPGA intégrant des cœurs de processeurs matériels dans leur structure. Cependant, beaucoup de concepteurs ne connaissent ni les capacités des FPGA, ni leur évolution, ni leur utilisation. La 1ʳᵉ partie de cette série en plusieurs parties fournit une présentation générale des FPGA. La 2ᵉ partie cible les offres FPGA de Lattice Semiconductor et la 3ᵉ partie se concentre sur les outils de conception et les gammes de dispositifs FPGA de Microchip Technology (de sa filiale Microsemi Corporation). La 4ᵉ partie aborde les composants et les outils de Xilinx. Cette 5ᵉ partie analyse les offres de la société Altera, rachetée par Intel, et formant désormais le groupe Intel Programmable Solutions Group (dans la suite de cet article, nous utiliserons le nom Intel).

Comme indiqué dans la 1ʳᵉ partie, les réseaux de portes programmables par l'utilisateur (FPGA) offrent de nombreuses caractéristiques qui en font une ressource informatique inestimable, autonome ou intégrée dans une architecture hétérogène. Cependant, de nombreux concepteurs ne connaissent pas bien les FPGA et ne savent pas comment les intégrer à leurs conceptions. Pour surmonter cet obstacle, il est possible d'examiner plus en détail les architectures FPGA et les outils associés proposés par les principaux fournisseurs.

Présentation détaillée des options FPGA

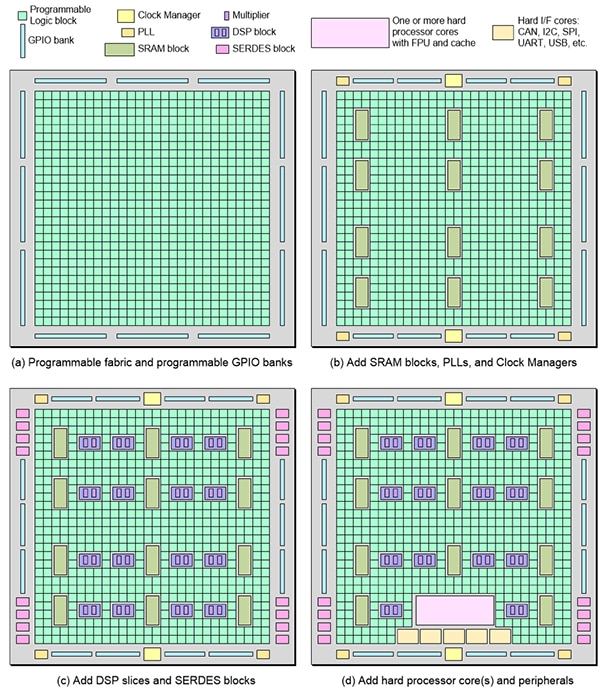

Il existe de nombreux types de FPGA différents sur le marché, chacun intégrant différentes combinaisons de capacités et de fonctions. Au cœur de tout FPGA se trouve une structure programmable. Elle se présente sous forme d'un réseau de blocs logiques programmables, ou éléments logiques (LE) (Figure 1(a)). L'étape suivante de la conception de la structure FPGA consiste à inclure des composants, comme des blocs SRAM, appelés RAM bloc (BRAM), des boucles à verrouillage de phase (PLL) et des gestionnaires d'horloge (Figure 1(b)). Des blocs de traitement des signaux numériques (DSP) (appelés « tranches DSP ») et des blocs de sérialiseur/désérialiseur (SERDES) haute vitesse peuvent également être ajoutés (Figure 1(c)).

Figure 1 : Les FPGA les plus simples contiennent uniquement une structure programmable et des E/S à usage général (GPIO) configurables (a) ; différentes architectures étendent cette structure principale avec des blocs SRAM, des PLL, des gestionnaires d'horloges (b), des blocs DSP et des interfaces SERDES (c), ainsi que des cœurs de processeurs matériels et des périphériques (d). (Source de l'image : Max Maxfield)

Figure 1 : Les FPGA les plus simples contiennent uniquement une structure programmable et des E/S à usage général (GPIO) configurables (a) ; différentes architectures étendent cette structure principale avec des blocs SRAM, des PLL, des gestionnaires d'horloges (b), des blocs DSP et des interfaces SERDES (c), ainsi que des cœurs de processeurs matériels et des périphériques (d). (Source de l'image : Max Maxfield)

Les fonctions d'interfaces périphériques comme CAN, I2C, SPI, UART et USB peuvent être implémentées sous forme de cœurs logiciels dans la structure programmable, mais beaucoup de FPGA les incluent sous forme de cœurs matériels dans la puce. De même, les microprocesseurs peuvent être implémentés sous forme de cœurs logiciels dans la structure programmable ou de cœurs matériels dans la puce (Figure 1(d)). Les FPGA dotés de cœurs de processeur matériels sont appelés des FPGA de type système sur puce (SoC). D'autres FPGA offrent différents ensembles de fonctions, fonctionnalités, possibilités et capacités adaptés à différents marchés et applications.

Il existe un certain nombre de fournisseurs de FPGA, dont Intel (qui a fait l'acquisition d'Altera), Efinix, Lattice Semiconductor, Microchip Technology (qui a fait l'acquisition d'Atmel et de Microsemi) et Xilinx.

Tous ces fournisseurs proposent plusieurs gammes de FPGA : certains proposent des FPGA SoC, d'autres proposent des dispositifs destinés aux applications d'intelligence artificielle (IA) et d'apprentissage automatique (ML), et d'autres encore proposent des dispositifs qui tolèrent les rayonnements pour les applications spatiales. Le choix du meilleur dispositif pour une tâche donnée peut s'avérer difficile, car il existe beaucoup de types de composants, chacun offrant des ressources différentes.

Présentation des FPGA et des FPGA SoC d'Intel

Intel propose des dispositifs programmables aux performances et aux capacités diverses, des plus modestes aux plus élevées, et des FPGA s'étendant des modèles traditionnels aux FPGA SoC (c'est-à-dire des dispositifs qui combinent une structure programmable FPGA avec un ou plusieurs cœurs de processeur renforcés).

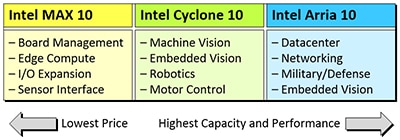

Intel compte cinq gammes de FPGA actives dans son portefeuille de produits actuel, dont les modèles Max 10, Cyclone 10 et Arria 10 (Figure 2). Intel propose également le modèle Stratix 10 très haut de gamme et ses nouveaux dispositifs Agilex de pointe.

Figure 2 : Les marchés et les applications cibles pour trois des cinq gammes de FPGA d'Intel, de la plus économique (Max 10) à celle proposant les meilleures capacités et performances (Arria 10), s'étendent de la gestion de carte et de l'extension E/S à la vision embarquée et au domaine militaire/de la défense. Le Stratix 10 et les derniers dispositifs Agilex améliorent davantage les performances. (Source de l'image : Max Maxfield)

Figure 2 : Les marchés et les applications cibles pour trois des cinq gammes de FPGA d'Intel, de la plus économique (Max 10) à celle proposant les meilleures capacités et performances (Arria 10), s'étendent de la gestion de carte et de l'extension E/S à la vision embarquée et au domaine militaire/de la défense. Le Stratix 10 et les derniers dispositifs Agilex améliorent davantage les performances. (Source de l'image : Max Maxfield)

Les FPGA Max 10 d'Intel intègrent une mémoire Flash NOR sur puce pour contenir leur configuration. Les autres gammes de produits ont des cellules de configuration basées sur SRAM et chargent leur configuration à la mise sous tension à partir d'un dispositif mémoire externe intégré ou d'un autre emplacement du système (par exemple, sous la commande d'un processeur externe). À l'exception de la gamme MAX 10, toutes les autres gammes de FPGA d'Intel sont disponibles sous forme de FPGA ou de FPGA SoC avec des systèmes de microprocesseurs renforcés intégrés.

Les fonctionnalités intégrées des FPGA MAX 10 incluent des convertisseurs analogique-numérique (CAN) et une mémoire Flash double configuration, qui permet de stocker deux images sur une seule puce et de basculer dynamiquement entre elles. Les FPGA MAX 10 prennent également en charge le processeur softcore Nios II embarqué, des blocs DSP et des contrôleurs de mémoire DDR3 (Soft Double Data Rate 3).

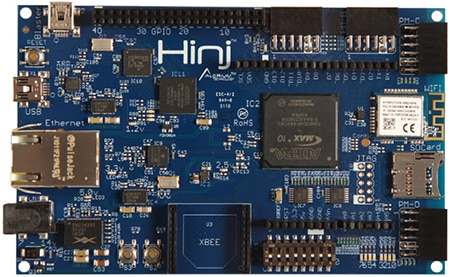

Le 10M16SCU169I7P avec 16 000 cellules/éléments logiques, 562 176 bits de RAM au total et 130 entrées/sorties (E/S) est un dispositif représentatif du portefeuille MAX 10. L'EK-10M08E144 d'Intel est une carte d'évaluation appropriée pour le FPGA MAX 10. Il en est de même pour le HINJKIT, un kit de développement de concentrateur de capteurs FPGA IoT d'Alorium Technology, LLC (Figure 3). Le HINJKIT est particulièrement intéressant, car son FPGA MAX 10 inclut le microcontrôleur 8 bits compatible AVR d'Alorium Technology, ce qui lui permet d'être utilisé avec l'IDE Arduino. La carte offre également un haut niveau de flexibilité d'interface pour les accessoires, les modules et les cartes porteuses IoT tiers.

Figure 3 : Le HINJKIT est une plateforme de développement de FPGA MAX 10 d'Alorium qui fournit un haut niveau de flexibilité d'interface pour les accessoires, les modules et les cartes porteuses IoT tiers. (Source de l'image : Alorium Technology)

Figure 3 : Le HINJKIT est une plateforme de développement de FPGA MAX 10 d'Alorium qui fournit un haut niveau de flexibilité d'interface pour les accessoires, les modules et les cartes porteuses IoT tiers. (Source de l'image : Alorium Technology)

Les FPGA Cyclone 10 GX d'Intel offrent des fonctions basées sur un émetteur-récepteur de 12,5 giga-octets (Go), une signalisation différentielle à basse tension (LVDS) de 1,4 gigabit par seconde (Gb/s) et une interface SDRAM DDR3 de 72 bits de largeur pour des débits de données jusqu'à 1866 mégabits par seconde (Mb/s). Les FPGA Cyclone 10 GX sont optimisés pour les applications de performances à bande passante élevée, telles que la vision artificielle, la connectivité vidéo et les caméras de vision intelligentes.

En comparaison, les FPGA Cyclone 10 LP sont optimisés pour les applications économiques à faible puissance statique comme l'extension E/S, la fusion de capteurs, les commandes moteur, le contrôle de mouvement, le contrôle et le pontage puce-à-puce. Les gammes de dispositifs GX et LP prennent en charge la migration verticale, ce qui permet aux concepteurs de commencer la conception avec un dispositif et de migrer vers des densités adjacentes ultérieurement.

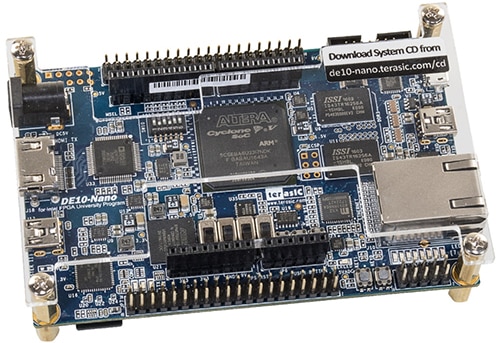

Le 10CL006YU256A7G avec 6272 cellules/éléments logiques, 276 480 bits de RAM au total et 176 E/S est un produit représentatif du portefeuille Cyclone 10. Un large éventail de modules et de cartes de développement et d'évaluation connexes est disponible, notamment le kit SoC Cyclone V SE P0496 DE10-NANO (Figure 4), la carte d'évaluation TSoM Cyclone V SE P0553 (basée elle aussi sur le FPGA SoC Cyclone V) et la carte d'évaluation FPGA TSoM Cyclone V SE P0581, tous de Terasic Inc. (Notez que le FPGA Cyclone V figurant sur ces cartes est une génération antérieure de la gamme Cyclone 10.)

Figure 4 : Le kit de développement économique P0496 DE10-NANO présente une plateforme de conception matérielle robuste permettant aux utilisateurs d'expérimenter et d'évaluer les FPGA Cyclone. (Source de l'image : Terasic Inc.)

Figure 4 : Le kit de développement économique P0496 DE10-NANO présente une plateforme de conception matérielle robuste permettant aux utilisateurs d'expérimenter et d'évaluer les FPGA Cyclone. (Source de l'image : Terasic Inc.)

Basés sur la technologie de processus 20 nanomètres (nm) de TSMC, les dispositifs Arria 10 combinent un système HPS (Hard Processor System) Arm Cortex-A9 MPCore double cœur avec une structure programmable qui inclut des blocs DSP en virgule flottante renforcés. Les dispositifs Arria 10 incluent également des émetteurs-récepteurs haute vitesse embarqués, des contrôleurs de mémoire matérielle et des contrôleurs de propriété intellectuelle (IP) de protocole, et ce dans un seul boîtier hautement intégré.

Le 10AX022C4U19E3SG avec 220 000 cellules/éléments logiques, 13 752 320 bits de RAM au total et 240 E/S est un dispositif représentatif du portefeuille Arria 10. Pour le développement avec ce FPGA, la carte d'évaluation FPGA Arria 10 GX DK-DEV-10AX115S-A d'Intel est la plateforme appropriée (Figure 5). Cette carte permet aux concepteurs de développer et de tester des conceptions PCI Express (PCIe) 3.0 basées sur Arria 10, de développer et de tester des sous-systèmes de mémoire composés de mémoires DDR4, DDR3, QDR IV et RLDRAM III, et de développer des conceptions modulaires et évolutives en utilisant les connecteurs de carte mezzanine FPGA (FMC) pour interfacer avec une carte mezzanine FMC fournie par les partenaires d'Intel.

Figure 5 : Le kit de développement FPGA Arria 10 GX DK-DEV-10AX115S-A offre un environnement de conception complet qui inclut tous les logiciels et le matériel requis pour développer et tester les conceptions basées sur PCIe, les sous-systèmes de mémoire et les systèmes basés sur des cartes FMC. (Source de l'image : Intel)

Figure 5 : Le kit de développement FPGA Arria 10 GX DK-DEV-10AX115S-A offre un environnement de conception complet qui inclut tous les logiciels et le matériel requis pour développer et tester les conceptions basées sur PCIe, les sous-systèmes de mémoire et les systèmes basés sur des cartes FMC. (Source de l'image : Intel)

Les FPGA Stratix 10 et les FPGA SoC d'Intel sont dotés de l'architecture FPGA Hyperflex d'Intel. Les FPGA de cette ligne de dispositifs répondent aux besoins des systèmes à haut débit avec des performances en virgule flottante jusqu'à 10 TFLOPS et la prise en charge d'émetteurs-récepteurs de 28,3 Gb/s (GX) à 57,8 Gb/s, ce dernier avec jusqu'à 144 voies d'émetteur-récepteur disponibles pour répondre aux demandes en bande passante des communications 5G, du cloud computing, de la virtualisation réseau et des réseaux de transport optique. Une variante inclut une interface PCIe Gen4 dotée d'une configuration jusqu'à x16 à 16 giga-transferts par seconde (GT/s) et un nouveau contrôleur de mémoire pour prendre en charge une sélection de mémoire persistante Optane DC d'Intel.

La carte d'évaluation FPGA Stratix 10 GX DK-DEV-1SGX-L-A d'Intel prend en charge le développement avec la ligne Stratix 10 (Figure 6). Cette carte permet aux concepteurs de développer et de tester les conceptions PCI Express (PCIe) 3.0 basées sur Stratix 10, de développer et de tester des sous-systèmes de mémoire composés de mémoires DDR4, DDR3, QDR IV et RLDRAM III, et de développer des conceptions modulaires et évolutives en utilisant les connecteurs de carte mezzanine FPGA (FMC) pour interfacer avec une carte mezzanine FMC, également fournie par les partenaires d'Intel.

Figure 6 : La carte d'évaluation FPGA Stratix 10 GX DK-DEV-1SGX-L-A fournit un environnement de conception complet qui inclut tous les logiciels et le matériel requis pour développer et tester les conceptions basées sur PCIe, les sous-systèmes de mémoire et les systèmes basés sur les cartes FMC. (Source de l'image : Intel)

Figure 6 : La carte d'évaluation FPGA Stratix 10 GX DK-DEV-1SGX-L-A fournit un environnement de conception complet qui inclut tous les logiciels et le matériel requis pour développer et tester les conceptions basées sur PCIe, les sous-systèmes de mémoire et les systèmes basés sur les cartes FMC. (Source de l'image : Intel)

Conception et développement avec des FPGA et des FPGA SoC d'Intel

Dans la 1ʳᵉ partie de cette série sur les FPGA, nous avons expliqué que pour concevoir de manière traditionnelle ces dispositifs, les ingénieurs devaient utiliser un langage de description matérielle (HDL) comme Verilog ou VHDL pour capturer l'intention de la conception à un niveau d'abstraction appelé RTL (Register Transfer Level). Ces descriptions RTL peuvent tout d'abord être simulées pour vérifier qu'elles répondent aux besoins, puis être traitées dans un outil de synthèse qui génère le fichier de configuration utilisé pour configurer (programmer) le FPGA.

L'étape suivante de l'abstraction consiste à capturer l'intention de la conception à l'aide d'un langage de programmation comme C/C++ ou d'une implémentation spéciale comme SystemC, qui est un ensemble de classes et de macros C++ fournissant une interface de simulation axée sur les événements. Ces dernières facilitent la simulation des processus concurrents, qui sont tous décrits à l'aide d'une syntaxe C++ simple. Ces descriptions peuvent être analysées et profilées en les exécutant comme des programmes normaux, avant d'être envoyées à un moteur de synthèse de haut niveau (HLS) qui génère le RTL transmis au moteur de synthèse standard.

À un niveau conceptuellement plus élevé d'abstraction se trouve le langage OpenCL (Open Computing Language), qui est une structure pour l'écriture des programmes s'exécutant sur des plateformes hétérogènes. En plus des FPGA, ces plateformes incluent des processeurs (CPU), des processeurs graphiques (GPU), des processeurs de signaux numériques (DSP) et d'autres processeurs ou accélérateurs matériels. OpenCL spécifie des langages de programmation (basés sur C99 et C++11) pour programmer ces dispositifs, ainsi que des interfaces de programmation (API) pour contrôler la plateforme et exécuter des programmes sur les appareils informatiques.

Dans le cas des FPGA et des FPGA SoC d'Intel, les utilisateurs développent des conceptions pour toutes les gammes de produits en utilisant le logiciel de conception Quartus Prime d'Intel. Ce logiciel est disponible en trois versions : Quartus Prime Pro Edition, Quartus Prime Standard Edition et Quartus Prime Lite Edition. Les éditions Pro et Standard exigent une licence payante, tandis que l'édition Lite est disponible en téléchargement gratuit.

L'édition Pro est optimisée pour prendre en charge les fonctionnalités avancées des FPGA et FPGA SoC nouvelle génération avec les gammes de dispositifs Agilex, Stratix 10, Arria 10 et Cyclone 10 GX. L'édition Standard inclut une prise en charge étendue pour les gammes de dispositifs antérieures, mais également pour la gamme de dispositifs Cyclone 10 LP. L'édition Lite, qui est disponible en téléchargement gratuit sans licence requise, fournit un point d'entrée idéal pour les gammes de dispositifs haut volume.

Intel offre une sélection étendue d'outils et de ressources de conception supplémentaires, notamment l'outil Intel DSP Builder, le compilateur Intel High Level Synthesis (HLS) Compiler et le kit de développement logiciel Intel FPGA SDK for OpenCL.

Le kit d'outils Intel Distribution of the OpenVINO Toolkit est également utile, car il permet aux développeurs de créer des applications d'intelligence artificielle (IA), de vision artificielle, audio, vocales et de langage qui offrent une inférence d'apprentissage profond de la périphérie au cloud. En plus des FPGA, ce kit d'outils prend en charge une exécution hétérogène sur l'architecture et les accélérateurs IA d'Intel grâce à une API commune : CPU, iGPU, unité de traitement de la vision (VPU) Movidius d'Intel et accélérateur Gaussian & Neural Accelerator (GNA) d'Intel. Ce kit d'outils est pris en charge par le kit de démarrage OpenVINO basé sur le FPGA Cyclone V GT.

Conclusion

Les solutions de conception de traitement optimales reposent généralement sur des combinaisons de processeurs et de FPGA, sur des FPGA seuls ou sur des FPGA intégrant des cœurs de processeurs matériels dans leur structure. En tant que technologie, les FPGA ont évolué rapidement au fil des années et sont désormais capables de répondre à de nombreuses exigences de conception en matière de flexibilité, de vitesse de traitement et de puissance, ce qui les rend très utiles pour une vaste gamme d'applications s'étendant des interfaces intelligentes à la vision artificielle et à l'intelligence artificielle.

Du bas de gamme au très haut de gamme, des FPGA traditionnels aux FPGA SoC, Intel propose une vaste gamme de dispositifs programmables. Comme démontré, pour créer des conceptions avec ces dispositifs, Intel et d'autres fabricants tiers proposent une puissante suite d'outils et de kits de développement pour répondre aux besoins des développeurs de matériel, des développeurs de logiciels et des créateurs de systèmes d'intelligence artificielle et de vision artificielle.

En savoir plus

- Principes de base des FPGA : présentation et rôle des FPGA

- Principes de base des FPGA — 2ᵉ partie : premiers pas avec les FPGA de Lattice Semiconductor

- Principes de base des FPGA — 3ᵉ partie : premiers pas avec les FPGA de Microchip Technology

- Principes de base des FPGA — 4ᵉ partie : premiers pas avec les FPGA de Xilinx

- Notions de base sur les FPGA : guide pour les débutants

- Implémenter l'edge computing basse consommation et hautes performances avec les FPGA à technologie Quantum d'Efinix

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.