Utiliser des FPGA dans les applications à ressources limitées

Avec la contribution de Rédacteurs nord-américains de DigiKey

2025-05-07

Les systèmes embarqués à ressources limitées ont de plus en plus besoin d'une logique configurable. Les applications telles que l'Edge AI, la vision industrielle et l'automatisation industrielle requièrent une logique flexible et spécifique à l'application pour répondre aux exigences de performances en constante évolution tout en fonctionnant dans des limites strictes de consommation, de taille et de coût. Les réseaux de portes programmables par l'utilisateur (FPGA) modernes peuvent répondre à ces demandes contradictoires.

Cet article passe en revue les principaux critères de conception à prendre en compte lors de la sélection d'un FPGA pour les applications à ressources limitées. Il décrit ensuite comment les différentes lignes de produits s'adaptent à des scénarios spécifiques à l'aide d'exemples utilisant des FPGA optimisés en termes de consommation et de coût d'Altera. Il se termine par une présentation des kits de développement et des cartes d'évaluation pouvant être utilisés pour prototyper et valider les concepts de conception.

Éléments à prendre en compte lors du choix d'un FPGA

Le choix d'un FPGA pour un système à ressources limitées implique de prendre en compte plusieurs exigences de conception et de les adapter à la solution appropriée. Plusieurs caractéristiques clés doivent être considérées pour un FPGA :

Capacité des éléments logiques (LE) : en tant que bloc fonctionnel fondamental pour un FPGA, le nombre de LE détermine la quantité de logique personnalisée pouvant être implémentée. Des nombres plus élevés permettent des conceptions plus complexes : le compromis est une augmentation de la consommation, du coût et de la taille du boîtier.

E/S et mémoire : les FPGA sont souvent utilisés pour connecter des composants disparates au sein d'un système, ce qui fait du nombre de broches E/S une considération clé. Pour améliorer les performances E/S, de nombreux FPGA intègrent des blocs logiques fixes renforcés pour les interfaces telles que PCI Express (PCIe), la mémoire haute vitesse et les émetteurs-récepteurs multi-gigabits.

De plus, certains FPGA intègrent des fonctionnalités telles que des convertisseurs analogique-numérique (CAN) et de la mémoire Flash. Ces améliorations peuvent réduire le recours à des puces auxiliaires, permettant d'économiser de l'espace carte et d'améliorer le rendement énergétique.

Intégration du processeur : au lieu d'utiliser un processeur externe, un microprocesseur (MPU) logiciel peut être implémenté dans le FPGA. Cette approche peut réduire l'empreinte d'un système, mais elle convient mieux aux applications présentant des charges de travail de microprocesseur moins exigeantes.

Pour les applications nécessitant des microprocesseurs plus rapides et plus efficaces, les concepteurs peuvent envisager un FPGA avec un système de processeur matériel (HPS) qui implémentera un microprocesseur en tant que bloc logique fixe dans le FPGA.

Accélérateurs matériels : les FPGA incluent généralement des blocs de traitement des signaux numériques (DSP) dédiés qui gèrent efficacement les tâches à calcul intensif comme le contrôle de mouvement. Les dispositifs haut de gamme peuvent comporter des blocs tenseurs spécialisés pour les charges de travail d'IA. Les capacités de ces blocs accélérateurs varient considérablement selon les gammes de FPGA et peuvent avoir un impact significatif sur les performances globales du système.

Optimisations de la consommation et des boîtiers : certains FPGA sont spécifiquement conçus pour minimiser leur empreinte physique et électrique. Par exemple, ils peuvent proposer des modes veille basse consommation.

Outils : la création d'une logique personnalisée peut constituer un défi de taille, en particulier pour les concepteurs novices. Des outils comme le logiciel de conception Quartus Prime d'Altera ont été développés pour rationaliser le processus.

Conçu pour rendre la conception FPGA plus accessible, Quartus Prime offre une expérience de développement conviviale, un vaste catalogue de blocs logiques pré-construits et la possibilité d'interconnecter ces blocs logiques automatiquement. L'outil s'intègre aux flux de travail d'IA et d'apprentissage automatique (ML) courants, permettant aux développeurs de déployer des systèmes d'exploitation (OS) populaires comme Linux et Zephyr sur un FPGA.

De telles capacités peuvent accélérer de manière significative la conception FPGA, de sorte que les caractéristiques des outils jouent un rôle crucial lors de la sélection d'un dispositif.

Calcul à haute performance pour charges de travail embarquées avancées

Pour illustrer la manière dont les exigences de conception influencent le choix du FPGA, il est utile de commencer par les applications haut de gamme qui requièrent une densité de calcul, une bande passante et une intégration exceptionnelles. Les exemples incluent des applications Edge AI avancées et des passerelles industrielles hautes performances.

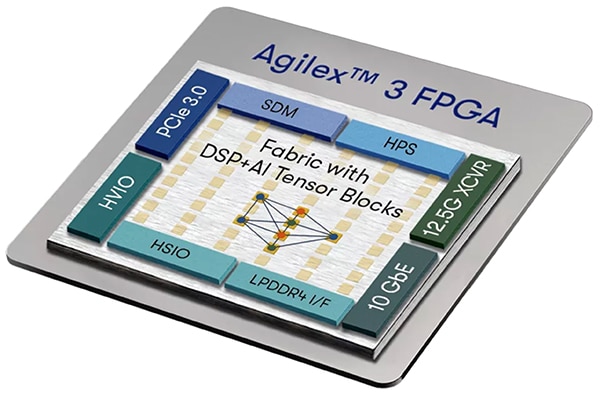

Les FPGA Agilex 3 (Figure 1) sont conçus pour répondre à ces exigences applicatives, offrant jusqu'à 135 000 LE. Les puces sont disponibles en variantes FPGA uniquement et système sur puce (SoC). Les dispositifs SoC intègrent un processeur Arm® Cortex®-A55 double cœur de 800 MHz, permettant au FPGA de prendre en charge des piles logicielles complexes telles que des interfaces homme-machine (IHM) ou des piles réseau.

La structure programmable comprend des blocs AI Tensor capables de fournir jusqu'à 2,8 téra-opérations INT8 par seconde (TOPS). Ces blocs prennent en charge divers formats de calcul, y compris FP16, FP19, FP32 et BFLOAT16, et ils sont optimisés pour l'exécution efficace des charges de travail IA. Des blocs DSP à précision variable sont également inclus, offrant des performances jusqu'à 180 giga-opérations en virgule flottante par seconde (GFLOPS) pour le traitement des signaux à usage général.

Figure 1 : L'Agilex 3 se distingue par ses blocs DSP et AI Tensor hautes performances. (Source de l'image : Altera)

Figure 1 : L'Agilex 3 se distingue par ses blocs DSP et AI Tensor hautes performances. (Source de l'image : Altera)

La connectivité haut débit est un autre atout de l'architecture Agilex 3. Les émetteurs-récepteurs prennent en charge des débits de données jusqu'à 12,5 gigabits par seconde (Gb/s), avec des blocs E/S renforcés disponibles pour PCIe 3.0, 10 Gigabit Ethernet (GbE) et les interfaces mémoire LPDDR4. La prise en charge de la synchronisation temporelle de précision IEEE 1588 améliore encore son adéquation aux réseaux industriels en temps réel.

Le dispositif A3CZ135BB18AE7S illustre les capacités de cette gamme de produits. Il comprend 135 000 LE, 184 blocs DSP et délivre 2,54 TOPS.

Intégration avancée pour systèmes complexes

Pour les applications telles que l'automatisation industrielle et les systèmes de vision de milieu de gamme, la puissance de calcul brute peut être moins importante que la capacité à prendre en charge des configurations complexes avec de grandes quantités de logique et d'E/S personnalisées. Les FPGA Cyclone V sont bien adaptés à ces scénarios, offrant jusqu'à 300 000 LE et de nombreuses interfaces haut débit. Comme l'Agilex 3, ces puces sont disponibles en variantes FPGA uniquement et SoC. Dans ce cas, les dispositifs SoC intègrent un processeur Arm Cortex-A9 double cœur.

La structure programmable de ces puces inclut des blocs DSP à précision variable qui prennent en charge la multiplication à virgule fixe triple 9 × 9 et double 18 × 18, ainsi que la multiplication à virgule fixe ou flottante 27 × 27. Ces blocs peuvent être utilisés pour l'IA et le traitement avancé des signaux.

Un large éventail d'E/S prend en charge plusieurs niveaux de tension et types d'interfaces. Les blocs logiques renforcés permettent une connectivité haut débit avancée, notamment PCIe 2.0, des contrôleurs DDR3 et des émetteurs-récepteurs fonctionnant jusqu'à 6,144 Gb/s.

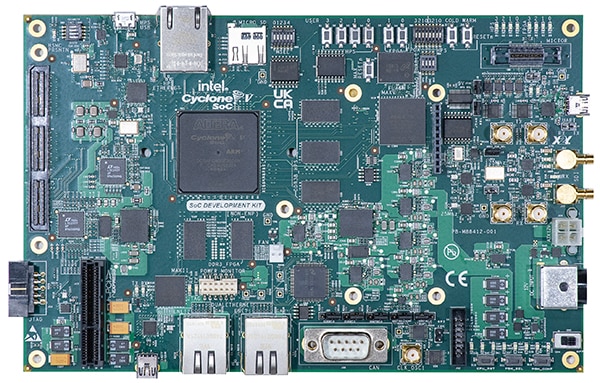

Les développeurs peuvent évaluer la gamme de SoC Cyclone V à l'aide du kit de développement DK-DEV-5CSXC6N-B (Figure 2). Ce kit est conçu pour le prototypage rapide de systèmes haut débit complexes.

Figure 2 : Le kit de développement Cyclone V DK-DEV-5CSXC6N-B permet le prototypage hautes performances. (Source de l'image : Altera)

Figure 2 : Le kit de développement Cyclone V DK-DEV-5CSXC6N-B permet le prototypage hautes performances. (Source de l'image : Altera)

Le kit offre plusieurs fonctionnalités importantes :

- Deux ports Ethernet, un connecteur PCIe x4 et une carte mezzanine haute vitesse (HSMC) avec 16 canaux LVDS dans chaque direction

- USB 2.0 OTG, CAN, UART et une interface LCD à deux lignes

- 1 Go de SDRAM DDR3 pour chaque côté FPGA et HPS, 128 Mo de Flash Quad-SPI et une carte microSD de 4 Go

La carte est équipée du dispositif 5CSXFC5D6F31C8N, qui comprend un processeur Arm Cortex-A9 double cœur fonctionnant à 600 MHz, avec 85 000 LE, 87 blocs DSP et 288 broches E/S dans un boîtier 896-FBGA de 31 mm × 31 mm.

Logique configurable écoénergétique dans un boîtier compact

De nombreuses applications se caractérisent par des contraintes strictes d'espace et de consommation d'énergie. Les exemples incluent les interfaces de capteurs, le séquencement de l'alimentation et le contrôle des périphériques. Les FPGA tels que ceux de la famille MAX 10 offrent une solution efficace dans ces situations. Les dispositifs MAX 10 sont disponibles dans des configurations de 2000 à 50 000 LE et des boîtiers de seulement 3 mm × 3 mm.

Les fonctionnalités clés incluent jusqu'à deux CAN 12 bits intégrés, une interface mémoire DDR3 et des blocs multiplicateurs prenant en charge les modes 18 × 18 et doubles 9 × 9 à virgule fixe. La mémoire Flash intégrée avec prise en charge de double stockage d'images permet au FPGA de s'auto-configurer sans dispositif de mémoire externe.

Les capacités d'économie d'énergie sont l'un des attributs les plus remarquables de la famille MAX 10. Un mode veille intégré peut réduire la consommation d'énergie dynamique jusqu'à 95 %. Grâce à la mémoire Flash intégrée, les dispositifs peuvent également être complètement mis hors tension puis reprendre leur fonctionnement en moins de 10 ms.

Une option d'alimentation unique permet de simplifier davantage la distribution d'énergie. C'est pourquoi les dispositifs MAX 10 sont particulièrement adaptés aux rôles de supervision, où les domaines d'alimentation doivent parfois être mis en service avant le reste du système.

Les développeurs intéressés par le MAX 10 peuvent évaluer la famille de produits à l'aide de la carte d'évaluation FPGA MAX 10 EK-10M08E144 (Figure 3). Cette carte permet d'accéder aux signaux externes via des connecteurs Arduino UNO R3 et des points de test, avec une configuration conçue pour prendre en charge la mesure des performances CAN et du comportement de consommation global.

Figure 3 : La carte d'évaluation FPGA MAX 10 EK-10M08E144 offre un accès aisé aux principales E/S. (Source de l'image : Altera)

La carte est dotée du dispositif 10M08SAE144C8G, qui comprend 8000 LE et un seul CAN dans un boîtier LQFP à 144 broches. En plus de ses ressources matérielles intégrées, ce FPGA prend en charge le processeur logiciel Nios V basé sur RISC-V, permettant aux concepteurs d'implémenter des fonctions de contrôle légères sans avoir besoin de microcontrôleur (MCU) externe.

Performances équilibrées pour les applications de milieu de gamme

Certaines applications requièrent plus de capacités logiques et E/S que ce que les FPGA d'entrée de gamme peuvent fournir. Les exemples incluent la fusion de capteurs, le contrôle de mouvement et le pontage puce-à-puce. Les FPGA Cyclone 10 LP répondent à ces exigences en offrant jusqu'à 120 000 LE et 525 broches E/S dans des dispositifs optimisés pour une consommation et une bande passante équilibrées dans les applications sensibles aux coûts.

Comme le MAX 10, la famille de produits comprend des blocs DSP adaptés aux charges de travail telles que le filtrage, les boucles de commande et l'inférence IA de base. Contrairement au MAX 10, les dispositifs Cyclone 10 LP intègrent de véritables émetteurs-récepteurs LVDS et une terminaison sur puce (OCT) pour prendre en charge l'interfaçage numérique à haut débit.

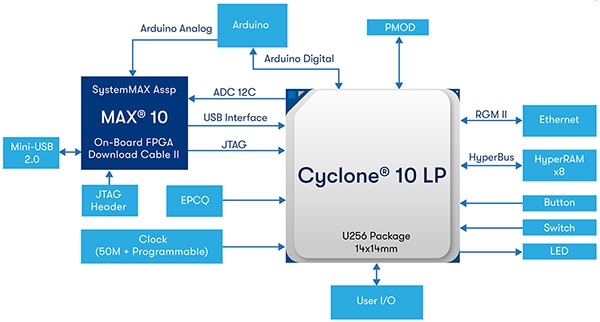

Les développeurs intéressés par le Cyclone 10 LP peuvent évaluer la famille de produits à l'aide du kit d'évaluation Cyclone 10 EK-10CL025U256 (Figure 4). Cette carte offre des connecteurs Arduino UNO R3 et Digilent Pmod pour une extension aisée. Les autres fonctionnalités incluent GbE, USB 2.0, 128 Mb de SDRAM et 64 Mb de Flash.

Figure 4 : Le kit d'évaluation Cyclone 10 EK-10CL025U256 permet l'extension périphérique aisée. (Source de l'image : Altera)

Figure 4 : Le kit d'évaluation Cyclone 10 EK-10CL025U256 permet l'extension périphérique aisée. (Source de l'image : Altera)

La carte comprend le dispositif 10CL025YU256C8G, avec 25 000 LE, 66 blocs DSP et 150 broches E/S dans un boîtier de 14 mm × 14 mm. Comme le MAX 10, le Cyclone 10 LP prend en charge le processeur logiciel Nios V.

Conclusion

Les concepteurs disposent d'une flexibilité sans précédent pour mettre en œuvre une logique personnalisée dans les systèmes embarqués. Les applications hautes performances peuvent bénéficier de FPGA avec accélérateurs IA intégrés. Les conceptions basse consommation peuvent tirer parti de dispositifs dotés de modes veille. Les systèmes à E/S intensives peuvent utiliser des puces à grand nombre de broches et des interfaces à haut débit. Il est important de noter que toutes ces capacités peuvent être réalisées dans les limites strictes des systèmes embarqués à ressources limitées, avec des kits faciles à utiliser.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.