Carte d'accélération Spartan Edge

Utilisateurs cibles

- Professeurs

- Ingénieurs bricoleurs

- Makers

- Développeurs de FPGA

- Étudiants

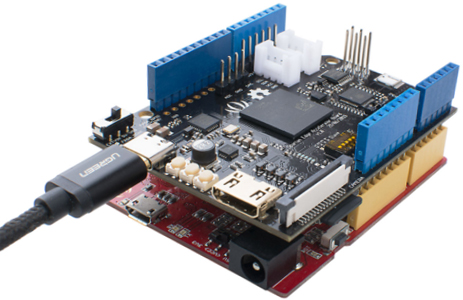

La carte d'accélération Spartan Edge (carte SEA en abrégé) est une carte de développement de FPGA légère, basée sur la puce Spartan-7 de Xilinx et respectant le facteur de forme du shield Arduino. Par conséquent, vous pouvez l'utiliser comme shield Arduino pour piloter un écran LCD et une caméra, ou en tant que carte de développement de FPGA autonome. En outre, grâce à la puce ESP32 embarquée, la carte SEA permet également à votre Arduino de bénéficier de fonctions WiFi et Bluetooth.

Spartan-7 est la puce FPGA la plus récente et la plus rentable de la famille de FPGA de Xilinx. Elle offre les meilleures performances de sa catégorie par watt. Par ailleurs, nous fournissons les API FPGA complètes pour Arduino, ce qui signifie que les utilisateurs d'Arduino sont en mesure d'utiliser la fonction FPGA sans rien connaître des FPGA. Cette carte permettra d'élargir les capacités d'Arduino à bien des égards, comme le traitement d'image simple et les applications de vision par ordinateur, le chiffrement et le déchiffrement des signaux, ainsi que l'échantillonnage et le traitement des signaux.

- Fonctionnalités

- Spécifications et périphériques de la carte

- Mise en route et conceptions de référence

Fonctionnalités

- Interface MIPI, mini HDMI intégrée

- Prise en charge de la caméra Raspberry Pi v1.0 (OV5640)

- Prise en charge maximale de la transmission d'images à 30 ips

- IoT WiFi et Bluetooth avec ESP32

- Prise en charge d'AWS, d'Azure et d'autres services cloud

- Prise en charge d'un algorithme de chiffrement logiciel

- 20 ports d'E/S étendus définis par l'utilisateur (mode autonome)

- 10 ports d'E/S étendus définis par l'utilisateur (mode shield Arduino)

- API FPGA complètes pour Arduino

- CAN et CNA 8 bits

- Gyroscope et accéléromètre à 6 axes

- 2 LED RVB et boutons utilisateur

- Mode Shield Arduino

- Mode autonome FPGA

Applications

- Entrée caméra MIPI et sortie HDMI Vivado Engineering

- LED embarquée, commutateur DIP, cas de référence CAN et CNA

- Cas de gyroscope embarqué

- Extension GPIO/UART/CAN/CNA/LED RVB pour Arduino

- Cas de générateur de signaux (nécessite une configuration Arduino)

- Cas de générateur de signaux contrôlé par ESP32

- Utiliser le cas de la plateforme AWS GreenGrass IoT

- Cas de reconnaissance des couleurs et de suivi d'objets

- Cas de reconnaissance graphique (reconnaissance du triangle, du cercle et du carré)

- Cas de reconnaissance de caractères numériques

- Implémentation des algorithmes de chiffrement et de déchiffrement AES dans le FPGA

- Implémentation de l'algorithme PID dans le FPGA

Carte d'accélération Spartan Edge

Référence DigiKey :1597-102030005-ND

Carte d'extension d'évaluation de la plateforme Arduino pour FPGA XC7S15 embarqué, ESP32

Spécifications du FPGA

Attention

La tension d'E/S du shield SEA étant de 5 V et la tension d'E/S du FPGA de 3,3 V, nous avons créé un diviseur de tension pour rendre les tensions d'E/S compatibles. La tension d'E/S de 3,3 V de la série SAM D21 sera inférieure à 3,3 V après division de la tension, ce qui n'est pas suffisant pour piloter les E/S du FPGA. Par conséquent, à l'heure actuelle, la carte de développement SEA ne prend en charge que les cartes Arduino à E/S de 5 V, telles que Arduino UNO et Seeduino V4.2.

| Puce FPGA | Spartan-7 XC7S15 | Cellules logiques | 12 800 |

|---|---|---|---|

| Tranches | 2000 | Bascules CLB | 160 000 |

| RAM distribuée max. (Ko) | 150 | Bloc RAM/FIFO avec ECC (36 Ko chacun) | 10 |

| RAM totale du bloc (Ko) | 360 | Tuiles de gestion d'horloge (1 MMCM + 1 PLL) | 2 |

| Tranches DSP | 20 | Puce sans fil | Espressif ESP32-D0WDQ6 |

| WiFi | 802.11 b/g/n 2,4 GHz | Bluetooth | Bluetooth 4.1 avec BLE |

| Vidéo | Mini HDMI x1 | Caméra | Interface CSI/MIPI x1 (compatible avec la caméra Raspberry Pi V1 - OV5640) |

| Carte SD | Emplacement pour carte Micro SD/TF x1 | GPIO du FPGA | Embase 10 broches (IO9 ~ IO0) |

| GPIO Arduino | Embase 32 broches (facteur de forme Arduino) | Grove | Connecteur Grove x2 (I2C/D2) |

| LED | LED monochrome x2 | Bouton | Démarrage x1 |

| Réinitialisation x1 | |||

| LED RVB x2 | Réinitialisation FPGA x1 | ||

| Utilisateur x2 | |||

| Commutateur | Commutateur de mode d'alimentation x1 | Tension de fonctionnement | 5 V |

| Commutateur DIP 5 canaux x1 | |||

| Tension d'E/S | 5 V | Mode d'alimentation | USB Type-C 5 V |

| VIN 8~17 V | |||

| Arduino Micro USB 5 V | |||

| CAN | ADC1173 8 bits | Accéléromètre et gyroscope | LSM6DS3TR 6 axes |

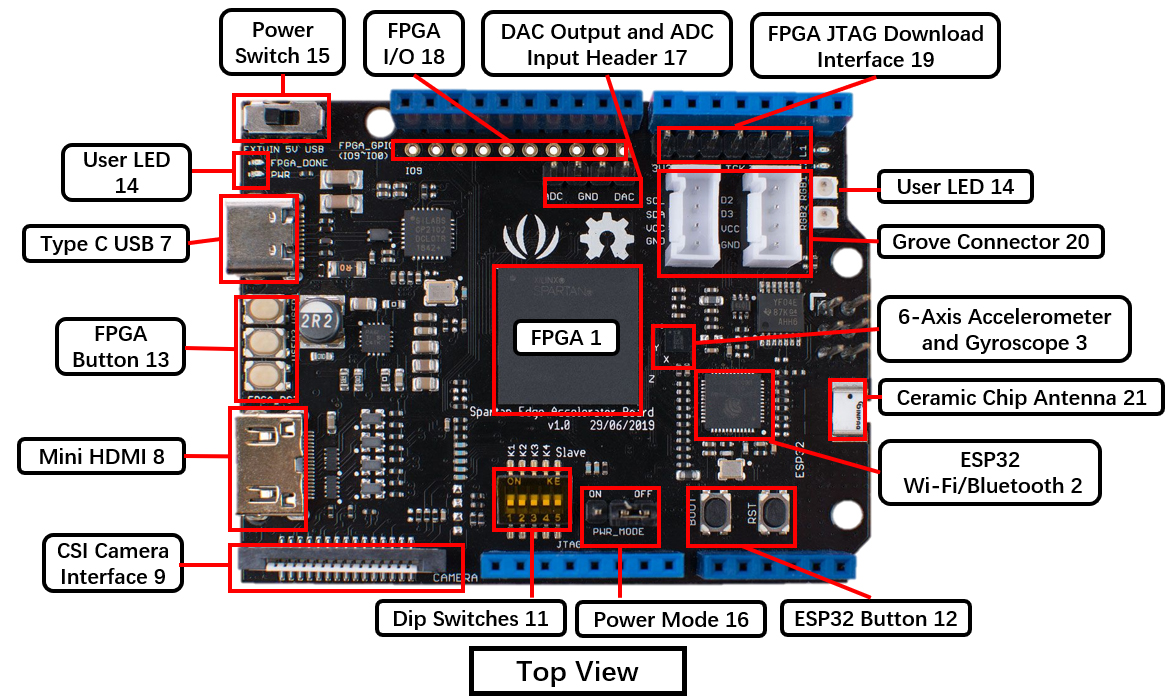

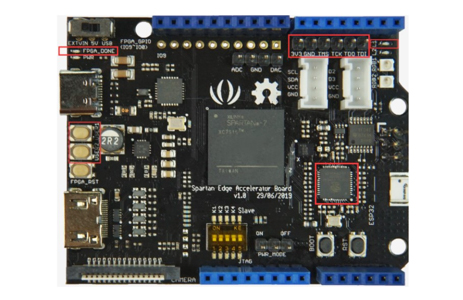

Descriptions et emplacements des périphériques de la carte SEA

| 1 | FPGA : XC7S15-1FTGB196C | 11 | Commutateurs DIP | 19 | Interface de téléchargement JTAG FPGA |

|---|---|---|---|---|---|

| 2 | Wi-Fi/Bluetooth : ESP32-D0WDQ6 | Commutateurs utilisateur K1-K4 | 20 | Connecteur Grove : 1x I2C ; 1x D2 et D3 | |

| Commutateur K5 : mode de programmation FPGA | |||||

| 3 | Gyroscope et accéléromètre 6 axes : LSM6DS3TR | ->>>> JTAG : Utilisation de l'outil de programmation officiel de Xilinx | 21 | Antenne monopuce en céramique | |

| ->>>> Esclave : Utilisation d'ESP32 pour programmer le FPGA | |||||

| 4 | CNA : DAC7311IDCKR | 12 | Bouton ESP32 : démarrage et réinitialisation | 22 | CAN : ADC1173 |

| 5 | Abaisseur-CC/CC : TPS62130 | 13 | Bouton FPGA : USER1 USER2 FPGA_RST | 23 | Flash SPI : W25Q32JVZPIG |

| 6 | USB vers UART : CP2102-GMR | 14 | LED utilisateur : L1/L2/RGB1/RGB2 | 24 | Commutateur analogique : DG2788A |

| PWR : mise sous tension | |||||

| FPGA_DONE : s'allume après la programmation du FPGA avec esp32. | |||||

| 7 | USB : Type-C | 15 | Commutateur : | 25 | LDO : XC6221B102MR |

| USB -> Alimentation par USB Type-C (5 V CC) | |||||

| 5 V -> Alimentation par la broche VIN (8 ~ 17 V CC) | |||||

| 8 | Mini-HDMI | 16 | Mode d'alimentation : | 26 | LDO : RT9013-18GB |

| OFF -> Isolement de l'alimentation d'Arduino et du shield | |||||

| ON -> Connexion de l'alimentation d'Arduino et du Shield | |||||

| 9 | Interface CSI : caméra MIPI (compatible avec la caméra Raspberry Pi V1 - OV5640) | 17 | Embase d'entrée CAN et sortie CNA | 27 | LDO : CJ1117-3V3 |

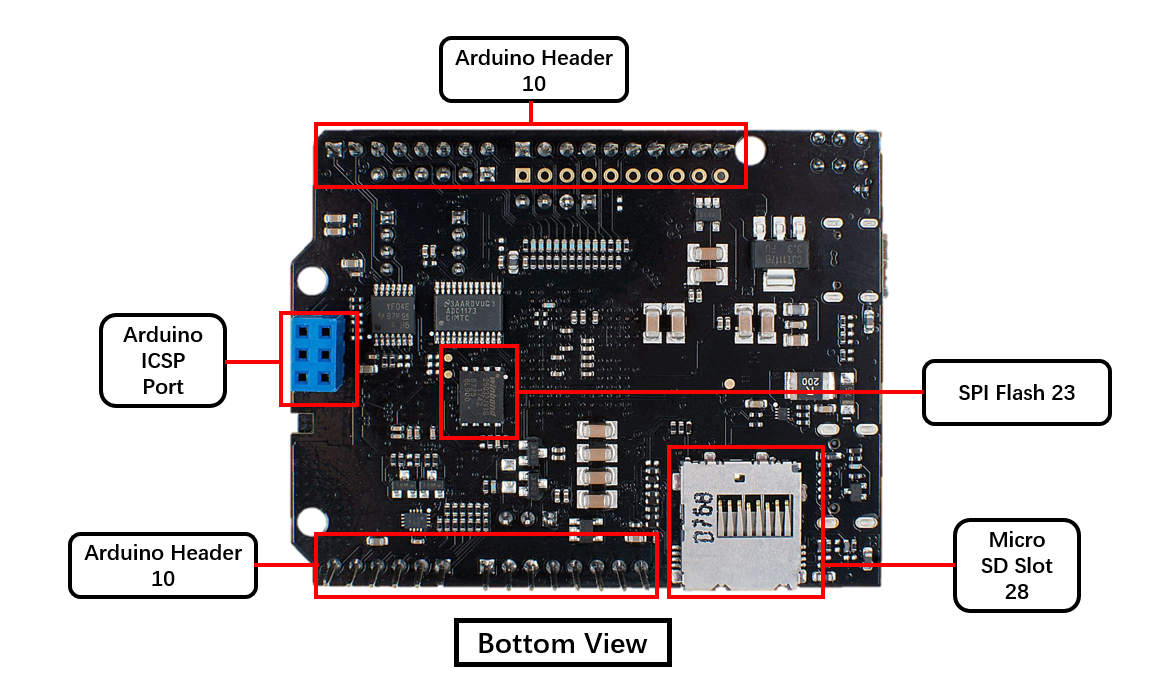

| 10 | Embase Arduino : compatible avec Arduino UNO | 18 | E/S FPGA : IO9~IO0 | 28 | Emplacement pour carte SD : carte Micro SD/TF |

La documentation suivante vous guidera tout au long du processus de création de conceptions de FPGA sur la carte SEA avec le logiciel Vivado 2019.2 de Xilinx.

Manuel de développement de la carte d'accélération Spartan Edge - Partie FPGA

Manuel de développement de la carte d'accélération Spartan Edge - Partie expérimentale

Manuel de développement de la carte d'accélération Spartan Edge - Partie ESP32

Yongming Tang, chercheur ; membre du SID, de l'IEEE, de la CVS (China Vacuum Society), directeur du Centre de développement de l'enseignement de l'Université du Sud-Est. Il a donné des cours de science et de technologie électroniques pendant de nombreuses années, a édité un manuel intitulé « Building Your Digital Building Blocks » et traduit un ouvrage scolaire. Il a créé et organisé le concours de conception PLD de l'Université du Sud-Est et le concours national de conception d'innovation de FPGA pour étudiants universitaires. Il a également remporté le deuxième prix de l'enseignement national, un prix spécial pour l'enseignement dans la province de Jiangsu, une fois le premier prix et le deuxième prix dans chaque cas.

Zhixiong Di, titulaire d'un doctorat, vice-doyen du département d'ingénierie électronique de la faculté des sciences et technologies de l'information de l'Université Jiaotong du Sud-Ouest. En 2014, il est diplômé de l'Université de Xidian avec une spécialisation en microélectronique et électronique à semi-conducteurs. Ses recherches portent sur la conception de systèmes matériels VLSI de compression d'images hautes performances et sur un algorithme d'implantation de circuits intégrés numériques, ainsi que sur la conception de matériel intelligent FPGA. Il a publié plusieurs articles de recherche SCI/EI et approuvé plus de dix brevets d'invention chinois. Il a présidé le sous-forum de la conférence CCF-DAC 2020. Il a été juge des finales de disciplines telles que le concours chinois de conception électronique de troisième cycle, le concours chinois d'innovation de troisième cycle « Core » et le concours national de conception d'innovation de FPGA de premier cycle.