Pourquoi et comment étendre la mémoire programme d'un microcontrôleur avec une mémoire Flash XiP SPI

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-05-08

Tandis que les applications de microcontrôleur se complexifient, les développeurs utilisent davantage de mémoire programme Flash pour le micrologiciel d'application. Cet élément est particulièrement vrai dans le cas des points d'extrémité IoT (Internet des objets) qui commencent à réaliser des tâches informatiques relativement complexes. Cependant, les applications peuvent parfois s'étendre jusqu'à nécessiter l'ajout d'une mémoire programme externe, poussant alors les développeurs à choisir entre une mémoire Flash parallèle ou série.

L'ajout d'une puce externe de mémoire Flash parallèle relie les lignes E/S, augmente la complexité et occupe un espace carte supplémentaire. Cet article décrit comment étendre la mémoire programme Flash d'un microcontrôleur en ajoutant une puce de mémoire Flash série externe d'Adesto Technologies qui prend en charge une interface XiP (eXecute in Place) SPI. Il explique également le mappage de la mémoire Flash XiP dans l'espace mémoire d'un microcontrôleur de Microchip Technology afin que l'exécution du code soit presque transparente pour le micrologiciel.

Les raisons d'une extension de mémoire externe

Les développeurs devraient, dans la mesure du possible, commencer le développement d'une application par la sélection d'un microcontrôleur disposant d'une feuille de route pour les dispositifs à brochage compatible offrant davantage de mémoire. Si, au cours du développement, le micrologiciel d'application s'étend jusqu'à dépasser la mémoire Flash du dispositif cible, ce dernier peut être facilement remplacé par un dispositif à brochage compatible présentant plus de mémoire Flash. La mémoire d'application peut ainsi être étendue sans nécessiter une nouvelle conception de la carte à circuit imprimé pour un microcontrôleur différent.

Cependant, l'application peut nécessiter plus de mémoire programme que celle dont dispose une puce de la gamme de microcontrôleurs à brochage compatible, nécessitant alors l'utilisation d'une mémoire Flash hors puce. Cette situation est de plus en plus courante et peut se produire pour différentes raisons, notamment :

- Le champ d'application du système peut s'étendre au-delà de son concept initial pendant la phase de développement. Des changements de dernière minute apportés à l'application, un ajout excessif de nouvelles fonctionnalités ou une prévision erronée des besoins en mémoire peuvent être à l'origine du problème. Les solutions sont une mise à niveau à l'aide d'un microcontrôleur à brochage compatible disposant de plus de mémoire programme Flash ou l'ajout d'une mémoire programme Flash externe, ce qui peut retarder le projet si le développement est déjà bien avancé.

- Les futures mises à niveau du micrologiciel sur le terrain peuvent nécessiter davantage de mémoire programme Flash que celle dont dispose le microcontrôleur déjà présent sur la carte système. Dans ce cas, les solutions sont limitées : le remplacement des systèmes sur le terrain par des systèmes offrant plus de mémoire programme Flash ou l'annulation de la mise à niveau.

- Le développement de la gamme de produits d'un système peut nécessiter un nouveau produit exigeant davantage de mémoire programme Flash que celle disponible pour la gamme de microcontrôleurs à brochage compatible. Les solutions consistent à reconcevoir le système à l'aide d'une nouvelle gamme de microcontrôleurs ou d'ajouter une mémoire programme Flash externe.

À l'évidence, l'anticipation des besoins des systèmes actuels et futurs quant à cette extension de mémoire est essentielle pour un développeur, ainsi que leur planification. S'il est possible que le projet nécessite une mémoire programme Flash externe, le développeur doit prévoir un emplacement pour une future extension du circuit imprimé. Bien que la puce de mémoire Flash n'ait pas à être installée sur la carte, il est préférable d'être prudent et de prévoir un espace.

La méthode classique pour augmenter une mémoire programme Flash consiste à utiliser une interface Flash parallèle avec des lignes d'adresse et de données. Cependant, même l'utilisation la plus efficace d'une mémoire Flash parallèle qui ne sacrifie pas la vitesse peut utiliser 16 bits d'adresse, 16 bits de données et au moins quatre signaux de commande. Pour ce faire, au moins 36 broches de microcontrôleur sont nécessaires.

En plus de représenter une utilisation inefficace des ressources du microcontrôleur, la sélection du microcontrôleur est limitée aux dispositifs disposant d'un bus externe, ce qui augmente le nombre de broches du microcontrôleur. Un bus parallèle externe occupe également une place importante sur un circuit imprimé, tandis que le bus d'adresse et de données haute vitesse augmente la possibilité d'interférences électromagnétiques (EMI).

Exécution du code XiP SPI

L'utilisation d'un dispositif de mémoire programme Flash externe prenant en charge une interface XiP SPI est une solution plus efficace. Une interface XiP SPI peut utiliser uniquement six broches pour interagir avec le microcontrôleur hôte. Contrairement à une interface SPI classique, la mémoire sur le dispositif de mémoire Flash externe n'est pas directement accessible à partir d'un pilote de micrologiciel SPI, mais est mappée dans la mémoire programme du microcontrôleur.

Le modèle AT25SL321-UUE-T d'Adesto Technologies (Figure 1) est un bon exemple de dispositif de mémoire Flash série conçu pour une interaction à l'aide d'une interface XiP SPI. Il s'agit d'une mémoire Flash de 32 mégabits (Mbit) prenant en charge les modes SPI simple, double et quadruple. Elle intègre une horloge SPI de 104 mégahertz (MHz), dont le mode SPI double offre une fréquence d'horloge équivalente de 266 MHz et le mode SPI quadruple une fréquence d'horloge équivalente de 532 MHz.

Figure 1 : L'AT25SL321 d'Adesto est une mémoire Flash de 32 Mbits prenant en charge les modes SPI simple, double et quadruple. La mémoire Flash de 32 Mbits est fournie en boîtier DFN8, TSSOP8 ou SOIC à 8 broches. (Source de l'image : Adesto Technologies)

En plus des 32 Mbits de mémoire Flash, le dispositif possède des registres d'état pour sa propre configuration. La lecture des registres d'état peut indiquer au micrologiciel si le dispositif présente une opération d'écriture ou d'effacement en cours. L'écriture sur les registres d'état permet de protéger en écriture des blocs de mémoire Flash.

L'AT25SL321 d'Adesto dispose également de 4 kilobits (kbit) de mémoire OTP (One-Time Programmable) pouvant être utilisés pour stocker des informations de sécurité, telles qu'un numéro de série unique. Il est fourni en boîtier DFN8, TSSOP8 ou SOIC à 8 broches.

Comme tous les dispositifs de mémoire série prenant en charge XiP SPI, l'AT25SL321 d'Adesto est configuré à l'aide d'un jeu d'instructions spécifique aux dispositifs Adesto. Le jeu d'instructions est constitué de 38 commandes utilisées par le microcontrôleur hôte pour contrôler la mémoire Flash série. Un périphérique XiP SPI sur un microcontrôleur hôte inclut une machine à états programmable initialisée à la mise sous tension du microcontrôleur avec le jeu d'instructions de la mémoire Flash série cible. Une fois le périphérique SPI initialisé, son fonctionnement est transparent pour l'exécution du code par le micrologiciel dans la région XiP SPI mappée en mémoire.

À titre d'exemple, si le micrologiciel de microcontrôleur hôte lit des données provenant de la région mappée en mémoire, le XiP SPI configuré à l'aide du jeu d'instructions Adesto envoie un code d'instruction de lecture des données suivi d'une adresse de 24 bits à la mémoire série Adesto. La mémoire série Adesto envoie alors, octet par octet, le contenu de la mémoire au microcontrôleur hôte. Le micrologiciel interprète cette situation comme une lecture normale depuis la mémoire.

En plus des broches d'horloge SPI, de données et de sélection de puce, l'AT25SL321 d'Adesto possède deux broches supplémentaires pour des fonctionnalités en système améliorées. WP\ est une broche de protection en écriture active basse qui empêche toute écriture sur les registres d'état afin de protéger en écriture des blocs de code. Le microcontrôleur peut utiliser cette broche pour empêcher les tâches à basse priorité d'effectuer des modifications non autorisées. HOLD\ est utilisée pour interrompre un transfert de données en cours. Cette fonctionnalité peut être utile si le microcontrôleur reçoit un signal d'interruption haute priorité tandis qu'un transfert de données vers la mémoire est en cours et qu'il doit être mis en pause jusqu'à ce que l'interruption soit traitée.

Le dispositif Flash 32 Mbits AT25SL321 d'Adesto prend en charge quatre modes de fonctionnement :

- Fonctionnement SPI standard : la mémoire Flash est accessible comme un dispositif de mémoire SPI standard avec une horloge SPI (SCLK), une sélection de puce active basse (CS\), des données d'entrée série (SI) et des données de sortie série (SO). Les modes de bus SPI standard 0 et 3 sont pris en charge.

- Fonctionnement SPI double : ce fonctionnement offre deux fois le débit de données d'un fonctionnement SPI standard grâce aux broches SI et SO utilisées en tant que broches de données bidirectionnelles, appelées IO0 et IO1.

- Fonctionnement SPI quadruple : ce fonctionnement offre quatre fois le débit de données d'un fonctionnement SPI standard. Outre IO0 et IO1, les broches WP\ et HOLD\ sont utilisées en tant que broches de données bidirectionnelles, appelées IO2 et IO3. Lors d'un fonctionnement SPI quadruple, les fonctionnalités WP\ et HOLD\ ne sont pas disponibles.

- Fonctionnement QPI : uniquement utilisé dans le cas d'un fonctionnement XiP SPI. Tandis que les modes SPI standard, double et quadruple permettent tous d'envoyer des commandes à la mémoire SPI uniquement à l'aide de la broche IO0, le fonctionnement QPI permet d'envoyer des commandes à l'aide des quatre broches IO[0:3], améliorant ainsi grandement les performances XiP SPI.

Si les 32 Mbits de l'AT25SL321 ne suffisent pas, Adesto propose également l'AT25QL641-UUE-T de 64 Mbits. Le brochage des deux dispositifs étant compatible, l'AT25QL641 peut représenter un équivalent exact. En plus de posséder davantage de mémoire, la seule différence entre les deux dispositifs est que l'AT25QL641 est défini en fonctionnement QPI par défaut à la mise sous tension. Le temps de configuration du dispositif est ainsi réduit sur les systèmes hautes performances. Les deux dispositifs ne consomment que 5 milliampères (mA) au cours d'un cycle de lecture de mémoire. Les deux dispositifs de mémoire d'Adesto fonctionnent à partir d'un rail unique de 1,7 V à 2 V et peuvent interfacer avec n'importe quel microcontrôleur à la tension compatible disposant d'une interface XiP SPI.

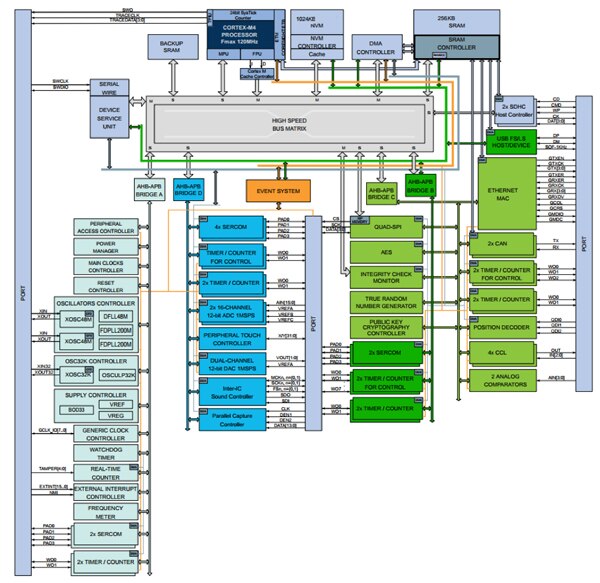

Pour le microcontrôleur hôte, Microchip Technology propose des interfaces XiP SPI sur sa série VATSAMD51, y compris le microcontrôleur basé Arm® Cortex®-M4F 120 MHz ATSAMD51J20A-UUT. Ce dispositif présente 1 Mo de mémoire Flash et 256 ko de RAM. Il offre une gamme complète de périphériques, notamment un convertisseur analogique-numérique (CAN), un convertisseur numérique-analogique (CNA), un port USB et I2S. Il dispose également d'un périphérique de cryptage à clé publique et d'un générateur de nombres aléatoires (TRNG) pour les fonctions de sécurité.

Figure 2 : L'ATSAMD51J20A de Microchip offre un ensemble complet de périphériques, notamment une interface série XiP SPI, un CAN, un CNA et la prise en charge pour le cryptage des données. (Source de l'image : Microchip Technology)

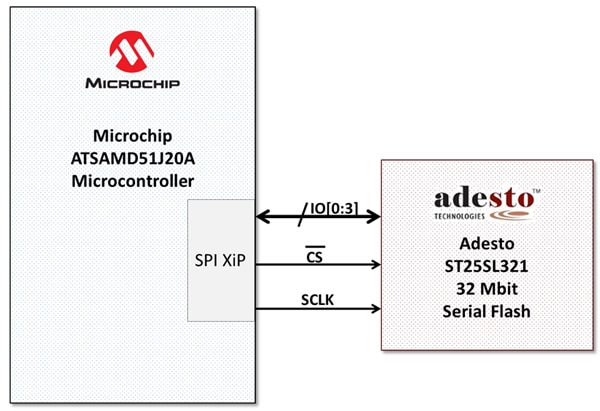

Afin de connecter une mémoire Flash externe, les développeurs peuvent utiliser le périphérique QSPI de l'ATSAMD51J20A qui prend en charge XiP SPI. Le code peut ainsi être directement exécuté à partir de la mémoire Flash d'Adesto. L'ATSAMD51J20A mappe la mémoire Flash Adesto dans l'espace de mémoire programme AHB (bus hautes performances avancé) d'Arm. Afin de protéger les données en mémoire Flash série, le XiP SIP ATSAMD51J20A permet le cryptage des données écrites dans une mémoire SPI externe et le décryptage des données lues à partir d'une mémoire SPI externe en toute transparence. Tout piratage du système et toute copie non autorisée du micrologiciel sont ainsi évités.

Figure 3 : Le microcontrôleur 32 bits ATSAMD51J20A de Microchip a un périphérique QSPI qui prend en charge un port série XiP SPI. Seulement six broches sont nécessaires pour communiquer facilement avec la mémoire Flash série AT25SL321 d'Adesto. (Source de l'image : DigiKey Electronics)

Utilisation de l'ATSAMD51J20A de Microchip avec un dispositif de mémoire Flash série d'Adesto

Le périphérique XiP SPI ATSAMD51J20A de Microchip possède trois registres qui sont utilisés pour envoyer des commandes à une mémoire Flash XiP série externe. Puisque les dispositifs de mémoire XiP Flash série des différents fournisseurs utilisent des codes d'instructions différents, ces registres doivent être configurés comme suit par le développeur selon le fournisseur de mémoire spécifique utilisé :

- Le registre de code d'instructions contient les instructions utilisées pour accéder à la mémoire Flash série. Pour un dispositif de mémoire Flash d'Adesto fonctionnant en mode SPI quadruple, ce registre contient une instruction 0x6B de sortie quadruple à lecture rapide si le micrologiciel exécute le code depuis la région XiP mappée en mémoire. Ce registre doit être modifié afin de correspondre au code d'instructions approprié si une opération d'écriture, d'effacement ou de registre d'état est réalisée.

- Le registre d'adresse d'instructions contient l'adresse de mémoire Flash à laquelle on accède dans la mémoire Flash série externe. Lorsque le XiP SPI ATSAMD51J20A de Microchip est configuré pour un mode de mémoire série, cette adresse est automatiquement définie par le périphérique XiP SPI sur l'adresse exécutée par le micrologiciel dans la plage comprise entre 0x0400 0000 et 0x0500 0000 d'espace de mémoire AHB mappée en mémoire.

- Le registre de trame d'instructions configure le XiP SPI pour le format de trame d'instructions spécifique au dispositif de mémoire externe utilisé. La sélection de la longueur d'adresse de 24 ou 32 bits, l'activation du débit de données double (DDR), la prise en charge du mode de lecture continue et la longueur du code d'opération sont incluses dans ce registre.

Le reste de l'interface XiP SPI de Microchip se configure facilement à l'aide des pilotes SPI de Microchip.

Tant que le micrologiciel d'application présent sur le microcontrôleur exécute le code depuis la région mappée en mémoire XiP SPI, le périphérique XiP SPI du microcontrôleur ne nécessite aucune nouvelle configuration. La mémoire Flash d'Adesto prend également en charge un mode de lecture avec une seule broche SI avec le code d'instruction 0x03. Si seul le mode SPI double est utilisé, le code d'instructions est 0x3B. Ces codes sont écrits par le micrologiciel d'application dans le registre de codes d'instructions.

Vider le cache associé à un espace d'adressage mappé en mémoire en cas de modification du registre de code d'instructions est considéré comme une bonne pratique. Lors d'une lecture ou d'une écriture dans les registres d'état de la mémoire Flash série, le cache doit être vidé, puis désactivé. Cette opération doit également être effectuée en cas d'écriture dans la mémoire Flash dans les régions mappées en mémoire. Le cache doit être réactivé lors de la reprise des opérations de lecture de la mémoire.

En raison des transferts de données à haut débit concernés, la mémoire Flash série doit être installée sur le circuit imprimé le plus proche possible du port XiP SPI du microcontrôleur. Si cette installation n'est pas possible, alors aucune piste ne doit être supérieure à 120 millimètres (mm). Le signal d'horloge doit se situer à une distance correspondant à au moins trois fois la largeur des pistes du circuit imprimé par rapport aux autres signaux pour éviter les interférences. Les signaux de données bidirectionnels IO[0:3] doivent tous se situer à moins de 10 mm les uns des autres pour éviter tout décalage.

Conclusion

Les dispositifs de mémoire Flash série externes peuvent fournir une exécution rapide du code de micrologiciel, sans la complexité ni l'espace carte excessif des puces Flash parallèles. L'extension du code de programme au fil du temps est ainsi simplifiée, ainsi que les mises à jour sur le terrain, sans nécessiter une nouvelle conception de la carte système.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.