Comment utiliser la mémoire MRAM pour améliorer la fiabilité et réduire la latence et la consommation d'énergie pour l'edge computing

Avec la contribution de Rédacteurs nord-américains de DigiKey

2020-11-05

L'utilisation de l'edge computing s'étend dans les applications telles que l'Internet industriel des objets (IIoT), la robotique, les appareils médicaux, les dispositifs corporels, l'intelligence artificielle, l'automobile et les conceptions portables. Cette croissance s'accompagne d'un besoin en matière de mémoire haute vitesse, non volatile, basse consommation, à faible latence et à faible coût pour des utilisations telles que le stockage de programmes et la sauvegarde de données. Bien que de nombreuses options soient disponibles, notamment la mémoire vive statique (SRAM), la mémoire vive dynamique (DRAM), la mémoire Flash et la mémoire morte programmable effaçable électriquement (EEPROM), chacune de ces technologies largement utilisées nécessite des compromis dans un ou plusieurs domaines, ce qui fait qu'elles sont loin d'être idéales pour l'edge computing.

Au lieu de cela, les concepteurs peuvent se tourner vers les mémoires vives magnétorésistives (MRAM). Les dispositifs MRAM, comme leur nom l'indique, stockent les données dans des éléments de stockage magnétique et offrent un véritable accès aléatoire, permettant des opérations de lecture et d'écriture de manière aléatoire dans la mémoire. Leur structure et leur fonctionnement sont tels qu'ils se caractérisent par une faible latence, une faible fuite, un nombre élevé de cycles d'écriture et une rétention élevée, autant de caractéristiques très souhaitables pour l'edge computing.

Cet article compare brièvement les capacités de performances des technologies de mémoires courantes (notamment EEPROM, SRAM et Flash) avec la mémoire MRAM. Il aborde ensuite les avantages de l'utilisation de la MRAM dans plusieurs applications edge computing, puis présente des dispositifs MRAM spécifiques de Renesas Electronics, quelques conseils d'utilisation de la MRAM et une plateforme d'évaluation pour aider les concepteurs à démarrer leur projet.

Comparaison des technologies de mémoire

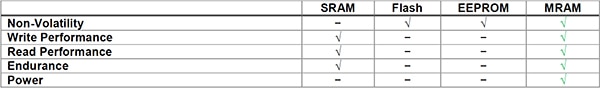

Les concepteurs d'applications edge computing ont le choix entre plusieurs technologies de mémoire, chacune offrant des performances et des compromis différents (Figure 1). La DRAM fournit le plus souvent la mémoire de travail pour différents types de processeurs pendant l'exécution des logiciels. Elle est économique, relativement lente (par rapport à la SRAM), consomme beaucoup d'énergie et ne conserve les données que tant qu'elle est alimentée. En outre, les cellules de mémoire DRAM sont sujettes à la corruption par rayonnement.

La SRAM est plus rapide et plus coûteuse que la DRAM. Elle est souvent utilisée comme mémoire cache pour les processeurs, tandis que la DRAM fournit la mémoire principale. Elle constitue la mémoire la plus gourmande en énergie des mémoires décrites ici, et comme la DRAM, c'est une mémoire volatile. Les cellules SRAM sont sujettes à la corruption par rayonnement. La DRAM et la SRAM offrent toutes les deux une grande endurance.

L'EEPROM est une mémoire non-volatile qui utilise une tension appliquée en externe pour effacer les données. Les EEPROM sont lentes, ont une endurance limitée — typiquement jusqu'à 1 million de cycles — et sont relativement gourmandes en énergie. L'EEPROM est actuellement la moins utilisée des technologies mémoire décrites ici.

La mémoire Flash est une variante de l'EEPROM, avec une capacité de stockage nettement supérieure et des vitesses de lecture/écriture plus rapides, mais elle reste relativement lente. La mémoire Flash est peu coûteuse et les données survivent à des conditions de mise hors tension pendant jusqu'à 10 ans. Cependant, la mémoire Flash est plus complexe à utiliser que les autres types de mémoire. Les données doivent être lues par bloc et ne peuvent pas être lues octet par octet. De plus, avant d'être réécrites, les cellules doivent être effacées. L'effacement doit être effectué bloc par bloc, et non par octet individuel.

La MRAM, pour sa part, est une véritable mémoire vive ; elle permet à la fois les opérations de lecture et d'écriture de manière aléatoire dans la mémoire. La MRAM se caractérise également par l'absence de fuite en veille, par sa capacité à supporter 1016 cycles d'écriture et par une capacité de rétention des données supérieure à 20 ans à 85°C. Elle est actuellement proposée dans des densités s'étendant de 4 mégabits (Mb) à 16 Mb.

La technologie MRAM est similaire à la technologie Flash avec des délais de lecture/écriture compatibles avec la SRAM (la MRAM est parfois appelée SRAM persistante (P-SRAM)). Grâce à ses caractéristiques, la MRAM est particulièrement adaptée aux applications qui doivent stocker et récupérer des données avec une latence minimale. Elle combine cette faible latence avec une basse consommation, une endurance illimitée, une évolutivité et une non-volatilité. L'immunité inhérente de la MRAM aux particules alpha la rend également adaptée aux dispositifs qui sont régulièrement exposés aux rayonnements.

Figure 1 : La MRAM est non volatile comme les mémoires Flash et EEPROM, et elle affiche des délais de lecture/écriture compatibles avec la SRAM. (Source de l'image : Renesas Electronics)

Figure 1 : La MRAM est non volatile comme les mémoires Flash et EEPROM, et elle affiche des délais de lecture/écriture compatibles avec la SRAM. (Source de l'image : Renesas Electronics)

Fonctionnement de la mémoire MRAM

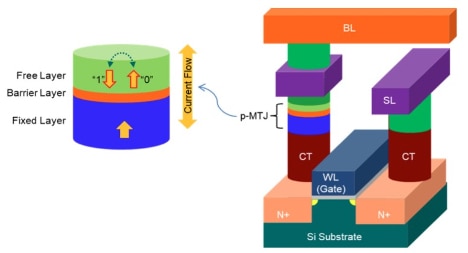

Comme son nom l'indique, les données en mémoire MRAM sont stockées par des éléments de stockage magnétique. Les éléments sont constitués de deux plaques ferromagnétiques, chacune pouvant contenir une magnétisation, séparées par une fine couche isolante. Cette structure est appelée « jonction tunnel magnétique » (MTJ). L'une des deux plaques est un aimant permanent défini sur une polarité spécifique lors de la fabrication ; la magnétisation de l'autre plaque peut être changée pour stocker des données. Renesas Electronics a récemment ajouté des dispositifs MRAM qui utilisent une technologie STT-MRAM (Spin Transfer Torque MRAM) propriétaire, basée sur une jonction tunnel magnétique perpendiculaire (p-MTJ). La jonction p-MTJ comprend une couche magnétique fixe et non modifiable, une couche de barrière diélectrique et une couche de stockage ferromagnétique modifiable (Figure 2).

Figure 2 : La cellule de base de la STT-MRAM est constituée d'une jonction MTJ et d'un transistor d'accès. (Source de l'image : Avalanche Technology)

Figure 2 : La cellule de base de la STT-MRAM est constituée d'une jonction MTJ et d'un transistor d'accès. (Source de l'image : Avalanche Technology)

Lors d'une opération de programmation, l'orientation magnétique de la couche de stockage est électriquement commutée d'un état parallèle (état de faible résistance « 0 ») à un état antiparallèle (état de haute résistance « 1 »), ou vice versa, selon le sens du courant à travers l'élément p-MTJ. Ces deux états de résistance distincts sont utilisés pour la détection et le stockage des données.

Cas d'utilisation MRAM

Les cas d'utilisation MRAM incluent l'enregistrement des données, les mémoires dans les nœuds IoT, l'apprentissage automatique/l'intelligence artificielle dans les dispositifs edge computing et les étiquettes RFID dans les hôpitaux.

Les enregistreurs de données exigent plusieurs mégabits de mémoire non volatile pour permettre l'accumulation de données à long terme. Ils sont généralement alimentés par batteries, mais peuvent également s'appuyer sur la récupération d'énergie pour leur alimentation, c'est pourquoi ils nécessitent une mémoire basse consommation. En cas de coupure de courant, les données enregistrées doivent pouvoir être conservées indéfiniment. La MRAM répond aux exigences de performances des enregistreurs de données.

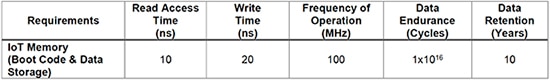

La persistance de la MRAM, combinée à un mode ultrabasse consommation, permet une solution de mémoire unifiée pour le code et les données dans les nœuds IoT fonctionnant à partir de récupérateurs d'énergie ou de sources batteries dans des facteurs de forme extrêmement compacts (Figure 3). Le temps de démarrage est souvent un point important à prendre en compte dans les nœuds IoT. La mise en œuvre d'une structure Code-in-Place utilisant la MRAM peut réduire le temps requis pour l'amorçage, ainsi que le coût global de la nomenclature puisqu'il y a moins besoin de DRAM ou de SRAM.

Figure 3 : Les capacités de vitesse, d'endurance et de conservation des données de la MRAM lui permettent de répondre aux exigences de mémoire des nœuds IoT. (Source de l'image : Avalanche Technology)

Figure 3 : Les capacités de vitesse, d'endurance et de conservation des données de la MRAM lui permettent de répondre aux exigences de mémoire des nœuds IoT. (Source de l'image : Avalanche Technology)

La persistance offerte par la MRAM permet également une nouvelle génération de nœuds IoT à capacité d'apprentissage automatique, où les algorithmes d'inférence n'ont pas à être rechargés à chaque activation du dispositif. Le traitement local inclut l'analyse des données de capteurs, la prise de décisions et, dans certains cas, la reconfiguration du nœud. Cette intelligence localisée exige une mémoire persistante et basse consommation. Ces dispositifs peuvent implémenter une inférence brute locale en temps réel et peuvent utiliser le cloud pour une analyse améliorée.

La rapidité de la MRAM est un avantage pour la mise en œuvre de l'apprentissage automatique dans des dispositifs périphériques tels que les systèmes de planification des ressources d'entreprise (ERP), les systèmes industriels d'exécution (MES) et les systèmes de contrôle et d'acquisition de données (SCADA). Dans ces systèmes, les données sont analysées et des modèles intermédiaires sont identifiés et partagés avec les domaines adjacents. L'architecture périphériques exige une vitesse de traitement et une mémoire persistante.

Les concepteurs peuvent également appliquer la MRAM dans les dispositifs de soins de santé où l'identification par radiofréquence (RFID) peut être utile. Grâce à sa basse consommation et à son immunité aux rayonnements, elle est adaptée aux environnements hospitaliers. Les étiquettes RFID dans les hôpitaux sont utilisées pour diverses raisons, notamment la gestion des stocks, les soins et la sécurité des patients, l'identification des équipements médicaux, ainsi que l'identification et le suivi des consommables.

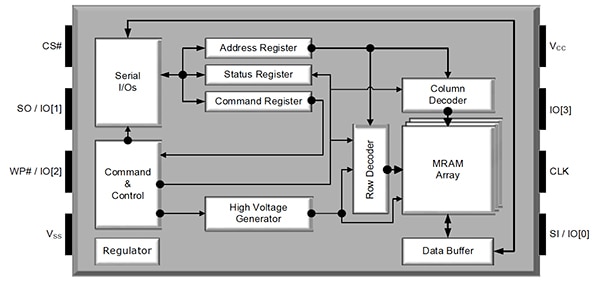

Mémoire MRAM série hautes performances

Les concepteurs de systèmes edge computing, y compris les contrôles et l'automatisation industriels, les dispositifs médicaux, les dispositifs corporels, les systèmes réseau, le stockage/RAID, l'automobile et la robotique peuvent utiliser le M30082040054X0IWAY de Renesas (Figure 4). Il est disponible dans des densités s'étendant de 4 Mb à 16 Mb. La technologie MRAM de Renesas est similaire à la technologie Flash avec des délais de lecture/écriture compatibles SRAM. Les données sont toujours non volatiles avec une endurance de 1016 cycles d'écriture et une conservation supérieure à 20 ans à 85°C.

Le M30082040054X0IWAY est doté d'une interface périphérique série (SPI), ce qui élimine le recours à des pilotes de périphériques logiciels. L'interface SPI est une interface série synchrone qui utilise des lignes séparées pour les données et l'horloge afin de maintenir l'hôte et l'esclave en parfaite synchronisation. L'horloge indique au récepteur le moment exact où il doit échantillonner les bits sur la ligne de données. Il peut s'agir du front montant (de bas en haut) ou descendant (de haut en bas) ou des deux fronts du signal d'horloge.

Figure 4 : Le M30082040054X0IWAY offre des schémas de protection des données à la fois matériels et logiciels. La protection matérielle est assurée via la broche WP#. La protection logicielle est contrôlée par des bits de configuration dans le registre d'état. Ces deux schémas empêchent l'écriture dans les registres et la matrice mémoire. (Source de l'image : Renesas)

Figure 4 : Le M30082040054X0IWAY offre des schémas de protection des données à la fois matériels et logiciels. La protection matérielle est assurée via la broche WP#. La protection logicielle est contrôlée par des bits de configuration dans le registre d'état. Ces deux schémas empêchent l'écriture dans les registres et la matrice mémoire. (Source de l'image : Renesas)

Le M30082040054X0IWAY prend en charge le mode eXecute-In-Place (XIP) qui permet d'exécuter une série d'instructions de lecture et d'écriture sans avoir à charger individuellement la commande de lecture ou d'écriture pour chaque instruction. Ainsi, le mode XIP permet de réduire les surcharges de commandes et le temps d'accès des lectures et écritures aléatoires.

Le M30082040054X0IWAY offre des schémas de protection des données à la fois matériels et logiciels. La protection matérielle est assurée via la broche WP#. La protection logicielle est contrôlée par des bits de configuration dans le registre d'état. Ces deux schémas empêchent l'écriture dans les registres et la matrice mémoire. Le dispositif est doté d'une matrice de stockage augmentée de 256 octets qui est indépendante de la matrice mémoire principale. Il est programmable par l'utilisateur et peut être protégé en écriture contre les écritures accidentelles.

Pour répondre encore mieux aux exigences des applications basse consommation, le M30082040054X0IWAY propose deux états basse consommation : arrêt prolongé et hibernation. Les données ne sont pas perdues lorsque le dispositif se trouve dans l'un de ces deux états basse consommation. De plus, le dispositif conserve toutes ses configurations.

Le dispositif est disponible en boîtiers DFN (WSON) à 8 broches et SOIC à 8 broches compacts. Ces boîtiers sont compatibles avec des produits basse consommation similaires, volatils et non volatils. Le dispositif est proposé avec des plages de températures de fonctionnement industrielles (-40°C à +85°C) et industrielles renforcées (-40°C à +105°C).

Utilisation de la MRAM

La MRAM peut réduire considérablement la consommation d'énergie globale par rapport aux autres technologies de mémoire. Mais le montant des économies d'énergie peut varier en fonction des modes d'utilisation de la conception d'application spécifique. Comme pour les autres mémoires non volatiles, le courant d'écriture est beaucoup plus élevé que le courant de lecture ou de veille. Par conséquent, les temps d'écriture doivent être réduits dans les applications à consommation d'énergie critique, en particulier dans les conceptions qui exigent des écritures fréquentes en mémoire. Les temps d'écriture plus courts de la MRAM peuvent atténuer cette considération et réduire la consommation d'énergie par rapport à d'autres choix de mémoires non volatiles, comme les mémoires EEPROM ou Flash.

Des économies d'énergie supplémentaires sont possibles avec la MRAM en utilisant une architecture de système de contrôle d'alimentation et en mettant la mémoire en veille aussi souvent que possible. Le temps d'activation d'écriture plus rapide de la MRAM permet de la mettre en veille plus fréquemment que d'autres mémoires non volatiles. L'absence de fuite de la MRAM lorsqu'elle est en veille est également un plus dans ce cas. Notez qu'un condensateur de découplage plus grand est souvent nécessaire pour prendre en charge l'énergie de mise sous tension lorsque le contrôle d'alimentation est utilisé.

Carte d'évaluation MRAM

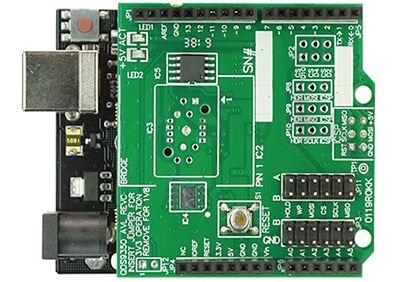

Pour aider les concepteurs à démarrer avec le M30082040054X0IWAY, Renesas fournit le kit d'évaluation M3016-EVK. Ce kit contient la MRAM 16 bits et permet aux utilisateurs de développer des solutions matérielles interactives en utilisant la populaire carte Arduino (Figure 5). Le kit plug-and-play fournit une carte hôte Arduino et un logiciel d'émulation de terminal qui communique avec l'interface USB de l'ordinateur. La carte d'évaluation se monte sur la carte hôte Arduino UNO avec des embases UNO R3. Les programmes de test fournis permettent aux utilisateurs d'évaluer rapidement les fonctionnalités du dispositif MRAM.

Figure 5 : Le kit d'évaluation M3016-EVK se monte sur une carte hôte Arduino UNO pour permettre une évaluation rapide des performances MRAM. (Source de l'image : Renesas)

Figure 5 : Le kit d'évaluation M3016-EVK se monte sur une carte hôte Arduino UNO pour permettre une évaluation rapide des performances MRAM. (Source de l'image : Renesas)

Conclusion

La conception de dispositifs edge computing utilisant des technologies de mémoires conventionnelles telles que DRAM, SRAM, Flash et EEPROM exige un certain nombre de compromis pouvant limiter les performances. Pour l'edge computing, les concepteurs peuvent se tourner vers les mémoires MRAM récemment introduites qui offrent un véritable accès aléatoire, permettant à la fois les opérations de lecture et d'écriture aléatoires dans la mémoire.

Comme illustré, la MRAM répond aux besoins en mémoire des concepteurs d'edge computing, notamment : un dispositif devant stocker et récupérer des données sans subir de latences importantes ; une faible consommation d'énergie grâce à l'absence de fuite en veille ; et la capacité à supporter 1016 cycles d'écriture avec une capacité de rétention des données supérieure à 20 ans à 85°C.

Lecture recommandée

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.