Comment déployer l'Edge AI sur des FPGA avec des outils familiers

Avec la contribution de Rédacteurs nord-américains de DigiKey

2026-02-17

L'Edge AI, ou intelligence artificielle (IA) en périphérie du réseau, se limite rarement à l'inférence. Les déploiements dans le monde réel impliquent généralement des entrées/sorties (E/S) haute vitesse, une mise en forme des signaux et des boucles de commande en temps réel, qui s'exécutent toutes simultanément. Ces charges de travail multifonctions exigent une coordination étroite et des niveaux de déterminisme que les concepteurs ont du mal à atteindre avec le matériel d'IA traditionnel.

Deux facteurs aggravent le problème. Tout d'abord, les modèles d'IA évoluent à un rythme effréné, ce qui pousse les concepteurs à adopter des plateformes prenant en charge la mise à jour rapide des algorithmes. Dans le même temps, de nombreux systèmes périphériques restent en service pendant une dizaine d'années, voire plus, ce qui complique la garantie d'une adaptabilité à long terme. Ensuite, le chemin entre le modèle entraîné et le système déployé reste fragmenté. Les experts en mégadonnées travaillent avec PyTorch et TensorFlow, tandis que les équipes de systèmes embarqués utilisent des chaînes d'outils totalement différentes, ce qui crée des frictions lors des transitions et ralentit la mise en production.

Relever ces défis exige des plateformes qui combinent un traitement IA à haut débit avec un comportement déterministe, des E/S flexibles et une adaptabilité à long terme, et ce, dans des enveloppes énergétiques limitées, typiques des déploiements en périphérie.

Cet article met l'accent sur les applications et les exigences associées qui incitent les concepteurs à explorer de nouvelles architectures Edge AI. Il présente ensuite des dispositifs FPGA et des outils logiciels compatibles Edge AI d'Altera, et montre comment ils peuvent être utilisés pour répondre aux besoins de ces applications pour de nombreux points de performances et de puissance.

L'évolution de l'Edge AI exige une innovation architecturale

Les systèmes périphériques utilisent de plus en plus diverses techniques d'IA, l'apprentissage automatique (ML) classique pour la détection d'anomalies, les réseaux neuronaux convolutifs (CNN) pour la perception et les transformateurs pour les grands modèles de langage (LLM). Ces algorithmes à calculs intensifs coexistent souvent avec des fonctions non-IA exigeantes, telles que le traitement des signaux, la mise en réseau et le contrôle en temps réel.

Les systèmes autonomes sont un parfait exemple. Ils doivent souvent ingérer des données provenant de multiples modalités de capteurs (par exemple, vidéo, audio, radar, LiDAR et retour de mouvement/position), pré-traiter ces flux à haut débit, analyser les résultats avec une IA sophistiquée, puis gérer des boucles de commande haute précision, et ce, avec un déterminisme fiable.

De nombreux exemples similaires existent dans les applications d'automatisation industrielle, d'imagerie médicale, de défense et de télécommunications. Un constat récurrent est que les charges de travail convergentes sont difficiles à gérer avec les architectures traditionnelles.

Comment les FPGA sont particulièrement adaptés à l'Edge AI

En revanche, ces exigences correspondent bien aux capacités des FPGA. Les FPGA, par essence, fournissent une logique configurable qui exécute les opérations en véritable parallèle, avec un comportement de temporisation intégré dès la conception plutôt que fluctuant pendant l'exécution. Cette architecture permet le déterminisme à faible latence essentiel à l'Edge AI. La logique flexible tire également parti de puissantes E/S : les FPGA offrent généralement une multitude d'E/S à haut débit capables d'interfacer avec une large gamme de capteurs et d'actionneurs, permettant un couplage étroit avec le traitement de l'IA.

Les FPGA contiennent également une mémoire interne distribuée, qui maintient les données à proximité de la logique qui les utilise. Cela réduit les goulets d'étranglement qui surviennent lorsque plusieurs étapes de traitement doivent se disputer l'accès à un bus de mémoire partagé, une contrainte courante dans les architectures basées sur des processeurs.

De nombreux FPGA intègrent également du matériel de traitement des signaux numériques (DSP) spécialisé. Ces circuits renforcés offrent des performances supérieures et un meilleur rendement énergétique pour les charges de travail de traitement des signaux par rapport aux structures à usage général. Certains FPGA intègrent également des systèmes de processeurs câblés capables d'exécuter des piles logicielles standard, y compris Linux, permettant ainsi le développement logiciel conventionnel pour des tâches telles que la mise en réseau, la gestion des périphériques et les interfaces utilisateur.

En résumé, un seul FPGA peut consolider des fonctions qui nécessiteraient autrement des puces d'E/S, des accélérateurs d'IA, un processeur DSP et des processeurs de plan de contrôle distincts. Cela peut se traduire par une nomenclature (BOM) réduite, une empreinte carte plus petite et une consommation d'énergie moindre, tout en maintenant la faible latence et le déterminisme exigés par les applications Edge AI.

Comment l'ajout de blocs tenseurs d'IA ouvre de nouvelles perspectives

Le matériel DSP FPGA traditionnel est déjà bien adapté à de nombreuses charges de travail en périphérie, mais l'inférence IA a tendance à être dominée par des opérations de multiplication-accumulation denses mais de faible précision. Pour remédier à ce problème, les dispositifs Agilex 3 et Agilex 5 d'Altera sont dotés d'un processeur DSP amélioré avec des blocs tenseurs d'IA. Il s'agit d'un matériel spécialisé pour les multiplications matrice-matrice et vecteur-matrice, qui apparaissent fréquemment dans les graphes de calcul d'IA.

Au cœur de cette approche se trouve un moteur de produit scalaire et d'additionneur/accumulateur (Figure 1). En mode tenseur, le moteur câblé effectue un produit scalaire à 10 éléments en utilisant des entrées 8 bits et des poids 8 bits préchargés. Pour étendre la plage dynamique, le chemin de données peut également utiliser un « exposant commun » partagé pour la mise à l'échelle de type virgule flottante des blocs, répondant au scénario typique dans lequel l'inférence IA requiert une plage dynamique élevée mais une faible précision.

Figure 1 : Le bloc tenseur d'IA peut effectuer des produits scalaires à 10 éléments. (Source de l'image : Altera)

Figure 1 : Le bloc tenseur d'IA peut effectuer des produits scalaires à 10 éléments. (Source de l'image : Altera)

Le résultat du produit scalaire est de 32 bits (en virgule fixe ou en virgule flottante simple précision), et il peut être mis en cascade sur un étage additionneur/accumulateur supplémentaire pour calculer des produits scalaires plus grands sur des blocs adjacents. Chaque bloc tenseur d'IA comprend deux colonnes de produits scalaires, permettant une variété de modes de fonctionnement.

Dans un cas d'utilisation typique, une partie du matériel mathématique amélioré est utilisée dans son rôle DSP traditionnel, comme par exemple pour effectuer des transformations de Fourier rapides (FFT) sur des données radar. D'autres parties sont utilisées comme blocs tenseurs d'IA, comme un réseau CNN pour effectuer la détection d'objets. Cette flexibilité est essentielle pour les systèmes périphériques qui doivent gérer l'IA en même temps que d'autres fonctions à calcul intensif.

Choix d'options FPGA pour différentes charges de travail d'IA

Les gammes Agilex offrent également une flexibilité considérable en matière d'évolutivité des performances. Les composants s'étendent des dispositifs axés sur l'efficacité mesurant seulement 12 mm × 12 mm à des variantes hautes performances offrant jusqu'à 152,6 TOPS de crête, avec une mise à l'échelle similaire des capacités d'interface mémoire et d'E/S.

Un exemple de composant hautes performances est l'Agilex 5 A5ED065BB32AE4SR0, qui fournit 22,17 TOPS dans un boîtier de 32 mm × 32 mm. Un exemple de composant axé sur l'efficacité est l'Agilex 3 A3CW135BM16AE6S, qui fournit 2,8 TOPS dans un boîtier de 16 mm × 16 mm. Les spécifications clés de chaque produit sont présentées dans le Tableau 1.

|

Tableau 1 : Quelques spécifications clés pour les FPGA Agilex 5 et Agilex 3. (Source du tableau : Altera (modifié par l'auteur))

Les deux gammes sont disponibles en tant que FPGA traditionnels ou systèmes sur puce (SoC) avec processeurs Arm intégrés. Les SoC Agilex 3 intègrent un processeur Arm Cortex-A55 800 MHz double cœur. Les SoC Agilex 5 présentent un ensemble asymétrique avec deux cœurs Cortex-A76 1,8 GHz et deux cœurs Cortex-A55 1,5 GHz. Les deux configurations prennent en charge Linux, permettant le développement logiciel conventionnel pour la mise en réseau, la gestion des périphériques et les interfaces utilisateur.

Simplifier le déploiement Edge AI à l'aide de FPGA

Les modèles d'IA sont généralement développés dans des structures axées sur des logiciels avec des cycles d'itération rapides, tandis que les implémentations FPGA requièrent historiquement des compétences en développement matériel et des cycles d'intégration plus longs. L'outil FPGA AI Suite d'Altera (Figure 2) offre un chemin plus direct depuis un modèle entraîné vers une propriété intellectuelle (IP) d'inférence FPGA déployable, en utilisant un flux compatible avec les outils d'IA standard de l'industrie.

Figure 2 : Le flux de travail de l'outil FPGA AI Suite relie les structures d'IA standard et le déploiement FPGA. (Source de l'image : Altera)

Figure 2 : Le flux de travail de l'outil FPGA AI Suite relie les structures d'IA standard et le déploiement FPGA. (Source de l'image : Altera)

Le flux de travail peut être résumé comme suit :

- Développer le modèle d'inférence dans une structure standard tel que PyTorch, TensorFlow ou ONNX.

- Utiliser le kit d'outils OpenVINO pour convertir le modèle en une représentation intermédiaire (IR) comprenant un fichier graphique (.xml) et des poids (.bin).

- Transmettre les artefacts IR au compilateur de graphes FPGA AI, qui mappe le modèle sur les ressources FPGA disponibles. Ces ressources peuvent inclure un processeur hôte externe, un processeur interne ou une configuration sans interface.

- Compiler et déployer les couches résultantes à l'aide de Quartus Prime Pro Edition, l'exécution étant gérée par la pile d'exécution du moteur d'inférence et les interfaces de programmation (API) FPGA AI pour le traitement de la mémoire et la planification matérielle.

- Utiliser l'optimiseur d'architecture pour équilibrer les performances et l'utilisation des ressources dans le cadre du processus de compilation. Il peut par exemple être utilisé pour garantir que l'implémentation répond aux objectifs de débit d'inférence tout en laissant de la place pour d'autres logiques FPGA.

Concrètement, l'intérêt de cette approche réside dans le fait qu'elle transforme le « déploiement sur un FPGA » en un processus d'intégration plutôt qu'en un effort de conception d'accélérateur. Les experts en mégadonnées peuvent rester dans des flux de travail de développement de modèles établis, tandis que les équipes de systèmes embarquées et FPGA reçoivent des artefacts qui s'intègrent naturellement dans un cycle de construction et de déploiement, permettant une itération plus rapide à mesure que les modèles et les exigences évoluent. Les modèles pré-entraînés disponibles via Open Model Zoo pour OpenVINO peuvent accélérer davantage le développement.

Démarrer rapidement avec des kits de développement faciles à utiliser

Pour commencer à explorer l'Edge AI sur FPGA, les concepteurs disposent de plusieurs options de kits de développement. Pour les applications hautes performances, le kit de développement Atum A5 P0775 de Terasic (Figure 3) constitue un bon choix. Conçu autour de l'Agilex 5 A5ED065BB32AE4SR0, le kit offre un large éventail d'interfaces adaptées aux systèmes de périphérie. Les fonctionnalités clés incluent 8 Go de DDR4, des ports QSFP+ et 2,5 Gb Ethernet (GbE), PCIe Gen3 x4, deux connecteurs de caméra MIPI et une sortie HDMI. Le kit inclut une licence gratuite pour Quartus Prime Pro Edition.

Figure 3 : Le kit de développement Atum A5 P0775 permet d'accéder au développement d'IA et de vision hautes performances. (Source de l'image : Terasic)

Figure 3 : Le kit de développement Atum A5 P0775 permet d'accéder au développement d'IA et de vision hautes performances. (Source de l'image : Terasic)

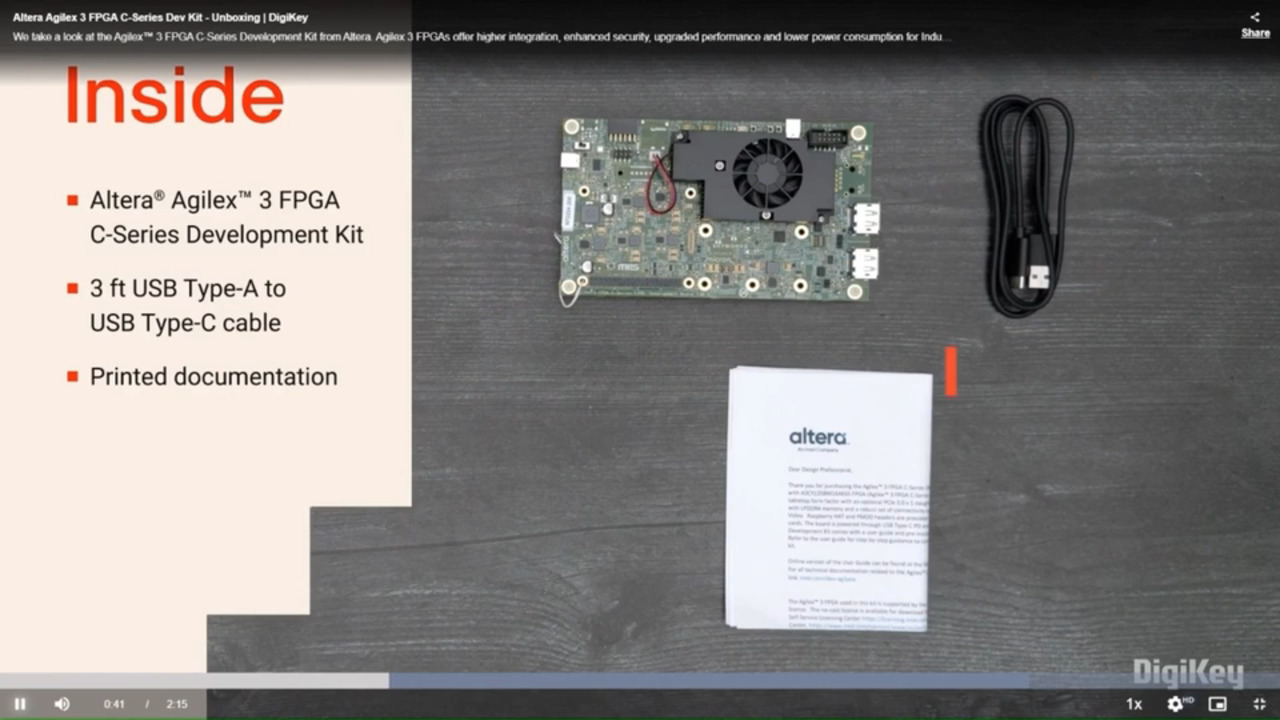

Pour les applications axées sur l'efficacité, les concepteurs peuvent se tourner vers le kit de développement série C SoC et FPGA Agilex 3 DK-A3W135BM16AEA (Figure 4). Architecturé autour de l'Agilex 3 A3CW135BM16AE6S, ce kit met l'accent sur le prototypage compact avec une extension compatible avec l'écosystème. La carte offre 4 Go de mémoire LPDDR4, GbE, DisplayPort et USB 2.0, ainsi qu'un connecteur Raspberry Pi HAT et une interface Digilent Pmod pour une extension fluide.

Figure 4 : Le kit de développement série C SoC et FPGA Agilex 3 DK-A3W135BM16AEA offre une plateforme compacte pour l'Edge AI axée sur l'efficacité. (Source de l'image : Altera)

Figure 4 : Le kit de développement série C SoC et FPGA Agilex 3 DK-A3W135BM16AEA offre une plateforme compacte pour l'Edge AI axée sur l'efficacité. (Source de l'image : Altera)

Conclusion

L'introduction de grands modèles de langage et d'autres nouvelles charges de travail d'IA en périphérie incite les développeurs à rechercher de nouvelles approches. Les FPGA offrent une solution unique qui permet non seulement de fournir une faible latence et des performances déterministes, mais également de gérer de nombreuses autres fonctions système. Grâce aux FPGA Agilex compatibles avec l'IA et à l'outil FPGA AI Suite, les développeurs peuvent accéder rapidement et facilement à ces fonctionnalités, ouvrant ainsi la voie à de nouvelles possibilités architecturales pour des conceptions hautement adaptatives et durables.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.