La mémoire Flash externe présente des avantages lors de l'utilisation de tables de correspondance dans des points d'extrémité IoT hautes performances

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-05-21

Comme les réseaux Internet des objets (IoT) se complexifient, les points d'extrémité IoT effectuent des traitements plus compliqués en périphérie. Cela peut nécessiter la mise à niveau d'un point d'extrémité existant avec un système doté d'un microcontrôleur affichant une fréquence d'horloge plus rapide, une mémoire plus étendue et un cœur de processeur plus puissant.

Des capteurs et des convertisseurs analogique-numérique (CAN) présentant un niveau élevé de précision peuvent également être requis, ce qui peut nécessiter un étalonnage régulier. Les erreurs linéaires peuvent facilement être compensées par une formule. Toutefois, les erreurs non linéaires ne suivent pas de schéma de déviation défini à partir de la lecture du capteur et ne peuvent donc pas être facilement compensées mathématiquement. Souvent, la façon la plus simple de compenser les erreurs non linéaires dans le micrologiciel consiste à stocker les données de correction requises dans la mémoire, grâce à une table de correspondance des données.

Cet article évoque brièvement les erreurs de capteurs et de CAN, et aborde les avantages de l'utilisation des tables de correspondance des données pour corriger ces erreurs. Il explique ensuite comment implémenter une table de correspondance Flash de données pratique et économique dans un système basé sur un microcontrôleur STM32L496VG de STMicroelectronics avec une puce mémoire Flash externe à interface périphérique série (SPI) LE25S161PCTXG d'ON Semiconductor.

Erreurs de capteurs

Les capteurs qui détectent les conditions analogiques comme la température, la pression et la tension peuvent présenter des erreurs non linéaires. Lors de la phase de développement d'un projet, il est important de tester les capteurs par rapport à une référence précise et de comparer la valeur de référence avec la sortie numérique du capteur. Cette opération permet au développeur d'identifier très tôt la nature des déviations de capteur par rapport aux valeurs de référence et de déterminer si les déviations sont acceptables au vu des exigences de l'application. Le développeur peut alors décider s'il est nécessaire de compenser les éventuelles déviations et, le cas échéant, si les déviations doivent être compensées dans le matériel ou dans le micrologiciel.

Certaines erreurs de capteurs peuvent être des erreurs linéaires prévisibles. La compensation de ce type d'erreurs peut simplement consister à ajouter ou à soustraire une valeur constante à la sortie du capteur. Ces erreurs varient parfois sur l'échelle du capteur. Par exemple, de zéro à un tiers de la pleine échelle, il peut s'avérer nécessaire d'ajouter une constante ; d'un tiers à un demi de la pleine échelle, une constante différente pourra être requise.

Ces erreurs sont prévisibles et, à l'évidence, faciles à corriger. Toutefois, la déviation par rapport à une lecture précise peut changer au fil du temps. De plus, de nouvelles erreurs de capteur peuvent survenir par la suite, pour des raisons d'exposition à des températures extrêmes, d'humidité ambiante importante ou encore de vieillissement des capteurs. Le besoin de corriger ou non ces erreurs dépend toujours de l'application. Il peut être nécessaire de tester le système dans des conditions extrêmes de température, de pression et d'humidité pour déterminer le comportement des capteurs. Ces tests environnementaux sont requis pour certaines applications telles que les applications automobiles, militaires et certains systèmes industriels. Toutefois, de nombreux nouveaux points d'extrémité IoT s'aventurent là où aucun capteur n'était jamais allé ; le test des capteurs pourrait donc devenir une nouvelle exigence.

Les périphériques analogiques de microcontrôleurs courants, comme les CAN, peuvent également exiger un étalonnage périodique du système comme tout capteur analogique. Les erreurs de CAN ne sont pas toujours prévisibles et même si l'erreur initiale peut être corrigée avec un algorithme, l'erreur peut changer au fil du temps, d'une manière qui ne pourra peut-être pas être facilement corrigée par un algorithme. Il peut s'ensuivre une incapacité du système à fonctionner avec la précision requise, entraînant ainsi des coûts de remplacement onéreux.

Avantages de l'utilisation d'une table de correspondance des données pour corriger les erreurs de capteurs analogiques

Une table de correspondance des données peut être une méthode pratique et efficace pour effectuer rapidement des calculs courants aussi complexes que des fonctions trigonométriques ou aussi simples qu'une inversion de bits d'un octet ou qu'une conversion d'un octet en code Gray. L'utilisation d'une table de correspondance de 256 octets pour l'inversion de bits d'un octet est significativement plus rapide que la réalisation d'une inversion de bits dans un micrologiciel. Il est sans danger de stocker cette table de correspondance dans une mémoire Flash de programme ou de données, car elle prend peu d'espace et n'a jamais besoin d'être modifiée.

Une table de correspondance de données est également une méthode très pratique pour stocker des données d'étalonnage de capteurs. Un périphérique analogique de microcontrôleur comme un CAN intégré peut nécessiter un étalonnage périodique en utilisant exactement la même méthode qu'un capteur analogique. Les CAN présents dans la plupart des microcontrôleurs peuvent afficher une précision jusqu'à ±2 ou ±3 bits les moins significatifs (LSB). Bien que cette précision puisse convenir à la plupart des applications, il est logique d'étalonner périodiquement les CAN pour les systèmes qui nécessitent une haute précision.

Une table de correspondance à étalonnage partiel pour corriger des données 24 bits pourrait ressembler à l'exemple du Tableau 1.

|

Tableau 1 : Extrait d'un exemple de table de correspondance de données pour les données d'étalonnage 24 bits. La valeur d'entrée brute est la lecture de la source dont les erreurs doivent être corrigées. La valeur brute est alors utilisée comme adresse 24 bits et pour chercher une valeur correspondante corrigée de 32 bits où l'octet le plus significatif est toujours 00h. (Source des données de la table : DigiKey Electronics)

Dans cet exemple, la valeur d'entrée brute est la lecture de la source dont les erreurs doivent être corrigées. La valeur brute est alors utilisée comme adresse 24 bits et pour chercher une valeur corrigée correspondante de 32 bits où l'octet le plus significatif est toujours 00h. Un décalage peut être ajouté à la valeur d'entrée brute si la table de correspondance ne démarre pas à l'adresse zéro.

Avant de décider où stocker la table de correspondance, il est important de déterminer la largeur requise pour la table de correspondance et si elle doit être réécrite. Ces deux décisions sont importantes. Il est logique d'utiliser une table de correspondance qui loge dans la mémoire Flash intégrée disponible si elle ne doit pas être réécrite. Mais si le capteur requiert un réétalonnage périodique, il faudra alors réécrire la mémoire Flash interne, ce qui nécessite l'effacement et la reprogrammation du secteur Flash complet.

Si le secteur Flash partage l'espace avec une mémoire programme, il peut s'avérer nécessaire de recompiler le code. Même si la table de correspondance se trouve dans son propre secteur dédié, les exigences de mémoire peuvent changer ou augmenter ultérieurement, ce qui entraîne la redéfinition d'une partie de l'espace du secteur de la table de correspondance pour du code supplémentaire. Cela complique l'étalonnage du capteur sur le terrain et peut empêcher l'auto-étalonnage indépendant du point d'extrémité IoT, en exigeant le téléchargement du code recompilé sur le réseau. Le problème se complique si de multiples capteurs sont impliqués.

Les grandes tables de correspondance, comme une table à 16 777 216 entrées pour l'étalonnage des données numériques de 24 bits, sont peu pratiques, voire impossibles à utiliser pour la mémoire programme Flash intégrée. La taille de la table de correspondance peut être réduite de moitié si seule une entrée sur deux est stockée, et si les résultats des entrées manquantes sont interpolés sur la base des données de table existantes. Cela entraîne une petite perte de performances et une possible perte de précision de ±1 LSB. Cependant, même cette table de correspondance à 8 388 608 entrées peut ne pas être pratique à stocker dans une mémoire Flash interne.

La meilleure solution pour ces grandes tables de correspondance de données dans un système basé sur un microcontrôleur est une mémoire Flash externe. Elle permet d'ajouter de manière simple plusieurs mégaoctets de tables de correspondance, sans sacrifier la mémoire programme Flash interne. Elle facilite également la réécriture de la table de correspondance par le système, sans interférer avec la mémoire Flash interne du microcontrôleur.

Pour les systèmes hautes performances, l'ajout d'une mémoire Flash externe parallèle est courant pour l'extension de la mémoire programme et de la mémoire de données. Toutefois, cette démarche nécessite un microcontrôleur avec un bus de données externe. L'adresse et les bus de données supplémentaires, ainsi que les signaux de contrôle requis, peuvent utiliser 36 broches du microcontrôleur ou plus. Cette exigence limite le nombre de microcontrôleurs disponibles pour l'application. Ces bus externes occupent aussi de l'espace supplémentaire sur le circuit imprimé et peuvent augmenter les interférences électromagnétiques (EMI) du système.

Pour la plupart des systèmes, la meilleure solution consiste à utiliser une mémoire de données Flash externe série qui utilise une interface périphérique série (SPI) pour le transfert des données. Il se peut alors que quatre broches suffisent sur le microcontrôleur.

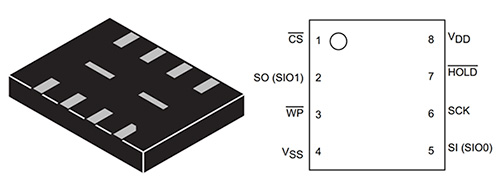

Le LE25S161PCTXG d'ON Semiconductor est un bon exemple de ce type de dispositif à mémoire Flash. Il s'agit d'un dispositif à mémoire Flash série de 16 mégabits (Mb) qui prend en charge une horloge SPI de 70 mégahertz (MHz). Cependant, il prend aussi en charge un mode SPI double qui lui permet de transférer les données à une vitesse maximale de 140 Mbps. Des registres d'état internes sont utilisés pour configurer les modes de lecture, d'écriture et basse consommation du dispositif.

Le LE25S161PCTXG présente les signaux SPI habituels pour la sélection d'horloge, de données et de puce (Figure 1). Il est également doté de deux broches supplémentaires. WP\ est un signal de protection en écriture actif bas qui empêche l'écriture sur les registres d'état du dispositif. Il peut être utilisé pour empêcher les tâches basse priorité du micrologiciel de procéder à une réécriture non autorisée du dispositif. HOLD\ interrompt un transfert de données en cours. Cela est utile si le microcontrôleur doit effectuer une interruption lorsqu'un transfert de données est en cours. Le transfert de données peut être mis en pause jusqu'à la fin de l'interruption, puis reprendre où il en était.

Figure 1 : La mémoire Flash série LE25S161PCTXG d'ON Semiconductor est fournie dans un boîtier UDFN à 8 broches avec une empreinte ultracompacte de 3 mm x 4 mm, et présente les signaux SPI habituels pour la sélection d'horloge, de données et de puce. (Source de l'image : ON Semiconductor)

La façon la plus aisée de lire une table de correspondance simple à deux colonnes stockée sur ce dispositif est de prendre la lecture du capteur, d'ajouter un décalage de mémoire, puis de lire le contenu de la mémoire à l'emplacement de cette adresse. Le contenu de la mémoire à cette adresse représente la lecture corrigée du capteur.

Un point d'extrémité IoT hautes performances requiert une fréquence d'horloge élevée, un processeur hautes performances et une interface SPI flexible. Pour ces applications, STMicroelectronics propose la gamme de microcontrôleurs hautes performances STM32L4. Par exemple, le microcontrôleur STM32L496VG fait partie de la gamme de produits STM32L4 qui fonctionne à 80 MHz et possède un cœur Arm® Cortex®-M4 avec une unité en virgule flottante (FPU). Il est équipé d'une mémoire Flash de 8 Mb et d'une mémoire SRAM de 320 kilo-octets (Ko). Il prend en charge une tension de fonctionnement de 1,71 V à 3,6 V, chevauchant la tension de fonctionnement du LE25S161PCTXG d'ON Semiconductor de 1,65 V à 1,95 V.

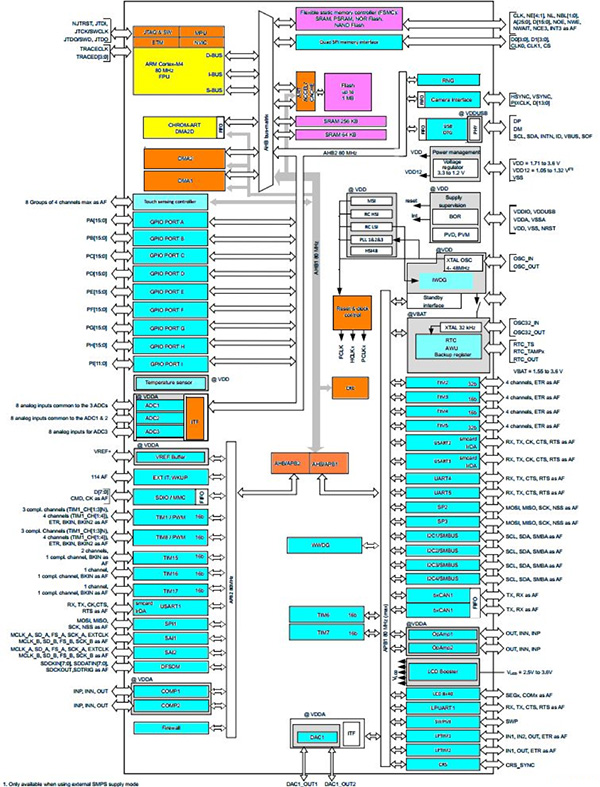

Le STM32L496VG offre une gamme complète de périphériques pour un point d'extrémité IoT hautes performances, notamment une horloge temps réel (RTC) avec calendrier, trois CAN de 5 méga-échantillons par seconde (Méch./s), un convertisseur numérique-analogique (CNA) à deux canaux, deux interfaces CAN (Controller area network) et quatre interfaces I2C (Figure 2). Il est également doté de trois interfaces SPI standard et d'une interface SPI quadruple.

Figure 2 : Le microcontrôleur STM32L496 est basé sur Arm Cortex-M4 80 MHz avec unité en virgule flottante, et présente une collection complète de périphériques, notamment une interface SPI quadruple de 40 MHz. (Source de l'image : STMicroelectronics)

Le développement du STM32L496VG est pris en charge par la carte de découverte STM32L496G-DISCO (Figure 3). Il s'agit d'une carte de développement complète pour un point d'extrémité IoT qui inclut des microphones MEMS (microsystèmes électromécaniques) stéréo, un connecteur de caméra 8 bits, huit LED, un joystick à quatre directions et un afficheur LCD couleur de 240 x 240 pixels. Les entrées CAN, les broches SPI quadruples et la plupart des E/S sont disponibles au niveau des broches de connecteur.

Figure 3 : La carte de découverte STM32L496G-DISCO est un environnement d'évaluation complet destiné au développement matériel et micrologiciel pour le ST32L496VG. (Source de l'image : STMicroelectronics)

L'interface SPI quadruple sur le STM32L496VG prend en charge une horloge SPI maximum de 40 MHz et des modes SPI standard et mappés en mémoire. L'interface SPI quadruple prend en charge le mode SPI double, ce qui permet un transfert de données à 80 Mbps maximum.

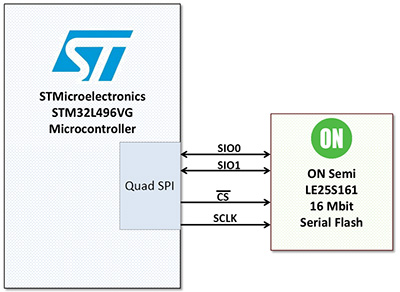

L'interface SPI quadruple de STMicroelectronics fournit une interface rapide pour les dispositifs de mémoire de données Flash série. En mode SPI standard, toutes les opérations sont effectuées à l'aide des registres SPI. Les données sont transférées en lisant et en écrivant le registre de données SPI. Une interruption est générée lorsque les données sont reçues. Il s'agit du même mode de fonctionnement que les trois SPI standard sur le STM32L496VG. Le mode SPI standard prend en charge les transferts de données simples, doubles et quadruples. Le LE25S161 d'ON Semiconductor prend en charge les modes SPI simple et double, et peut facilement communiquer avec le STM32L496VG en mode SPI double (Figure 4).

Figure 4 : Le port série SPI quadruple du STM32L496VG de STMicroelectronics peut communiquer avec le LE25S161 d'ON Semiconductor en mode SPI double, ce qui permet des transferts bidirectionnels de données sur SIO0 et SIO1 avec une horloge série SCLK de 40 MHz à 80 Mbps. (Source de l'image : DigiKey Electronics)

L'implémentation d'une table de correspondance des données dans cette situation est simplifiée grâce au choix des composants d'ON Semiconductor et de STMicroelectronics, ce qui permet une implémentation facile. L'interface SPI quadruple offre également une mémoire FIFO, utile pour les transferts de données en masse. Cependant, dans le cas d'une table de correspondance où il est nécessaire d'atteindre un seul emplacement de mémoire à la fois, il est recommandé de désactiver la mémoire FIFO, car elle n'est pas nécessaire et peut même ajouter des délais inutiles.

SPI quadruple avec mode mappé en mémoire

L'interface SPI quadruple prend également en charge un mode mappé en mémoire. Cela mappe la mémoire Flash série externe dans l'espace de mémoire de données ou de mémoire programme du microcontrôleur. Cela permet ainsi au micrologiciel du microcontrôleur d'accéder à la mémoire Flash SPI externe comme si elle faisait partie de la propre mémoire du micrologiciel, ce qui entraîne un fonctionnement transparent de la SPI quadruple pour le micrologiciel.

Si les accès à la table de correspondance ne sont pas fréquents, l'implémentation d'une table de correspondance avec un mode mappé en mémoire par rapport au mode SPI standard peut ne pas présenter d'avantages significatifs autres que la simplification du micrologiciel de l'application. Cependant, si l'application est un environnement à interruptions fréquentes, les transferts SPI peuvent être régulièrement mis en pause pour traiter ces interruptions. La situation peut encore se compliquer si une opération de correspondance SPI quadruple est interrompue par une autre.

Une combinaison d'accès fréquents à la table de correspondance et d'un environnement à interruptions élevées peut rapidement rendre le mode mappé en mémoire plus efficace, comparé au mode SPI standard. Cette combinaison simplifie le micrologiciel, empêche les problèmes dus à des accès SPI quadruples simultanés avec des priorités différentes et réduit les conflits d'interruption.

Cependant, l'un des inconvénients de l'implémentation d'une table de correspondance mappée en mémoire est la possibilité de polluer le cache de données. Même si le STM32L496 ne possède pas de cache de données, ce n'est pas le cas de certains microcontrôleurs qui ciblent des applications hautes performances en temps réel. L'accès à la table de correspondance mènera probablement à un échec d'accès au cache. Pour la plupart des applications, en effet, il y a une très faible possibilité d'avoir besoin d'accéder deux fois au même emplacement de table de correspondance dans le même fil ou la même sous-routine. Les données de la table de correspondance ne sont donc pas initialement mises en cache, et la mise en cache des données peut entraîner la suppression de données importantes du cache de données. Bien que le problème ne se pose que pour les applications ultra-hautes performances, ce sont ces applications hautes performances qui nécessitent un cache de données en premier lieu.

Les solutions à la pollution du cache de données par une table de correspondance sont limitées. Si le matériel le permet, la zone de la table de correspondance peut être marquée comme impossible à placer dans le cache. Une autre solution consiste à désactiver, puis à réactiver le cache de données avant et après l'accès à la table de correspondance. Cette solution peut être acceptable si la baisse de performances due à l'activation et à la désactivation du cache est acceptable. Certains caches de données prennent en charge des instructions de contrôle du cache spécifiques à l'architecture qui peuvent fournir de l'aide pour empêcher la pollution du cache. Il est important de comparer les performances du système lors de la configuration du cache de données, afin de trouver la meilleure méthode en fonction de l'application donnée.

La mémoire Flash série doit être placée sur le circuit imprimé pour qu'aucune piste ne dépasse les 120 mm de longueur. Pour éviter les interférences, le trajet du signal d'horloge SPI doit se situer à une distance correspondant à au moins trois fois la largeur des pistes du circuit imprimé par rapport aux autres signaux. Les deux signaux de données bidirectionnels doivent tous se situer à moins de 10 mm les uns des autres pour éviter tout décalage.

Conclusion

Un dispositif Flash SPI externe peut constituer une solution efficace pour implémenter de grandes tables de correspondance de données dans un point d'extrémité IoT. Il est facile à reprogrammer dans le système et facile à mettre à niveau, et il utilise des ressources de microcontrôleurs minimales.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.