Qu'est-ce que le temps de récupération d'un convertisseur de puissance et comment le contrôler ?

Les exigences de puissance accrues dans l'automobile, les petits véhicules électriques, les outils sans fil et les stations de charge entraînent une transition vers les systèmes d'alimentation 48 V. Ces systèmes présentent divers avantages : meilleur rendement, réduction des pertes, taille plus compacte et poids réduit. Tous ces systèmes d'alimentation convertissent la puissance fournie par le bus 48 V en tensions utilisables, ce qui nécessite l'utilisation de convertisseurs de puissance.

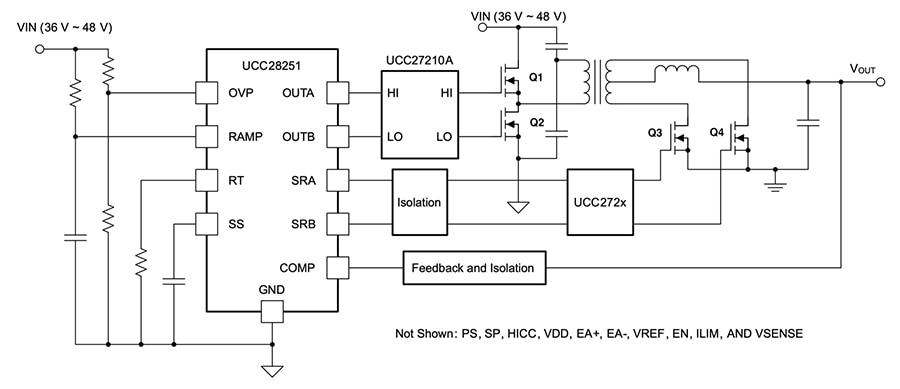

Les convertisseurs de puissance utilisent des techniques de commutation de puissance pour convertir 48 VCC en différentes valeurs de tension. Un convertisseur 48 V typique (ici, l'UCC28251PWR de Texas Instruments) repose sur des dispositifs de commutation de puissance configurés en demi-pont comme des transistors à effet de champ (FET), représentés sur la Figure 1 par Q1 et Q2. Ils sont contrôlés par un contrôleur à modulation de largeur d'impulsion (PWM) pour produire et réguler la tension de sortie souhaitée.

Figure 1 : Un convertisseur CC/CC typique utilise un contrôleur PWM pour commander des FET de puissance configurés en demi-pont. Le contrôleur ajuste la largeur d'impulsion au niveau des entrées des FET pour produire et réguler la tension souhaitée en sortie (VOUT). (Source de l'image : Texas Instruments)

Figure 1 : Un convertisseur CC/CC typique utilise un contrôleur PWM pour commander des FET de puissance configurés en demi-pont. Le contrôleur ajuste la largeur d'impulsion au niveau des entrées des FET pour produire et réguler la tension souhaitée en sortie (VOUT). (Source de l'image : Texas Instruments)

Dans ce circuit, les FET (Q1 et Q2) forment une topologie en demi-pont. Ils sont activés tour à tour pour commander le transformateur. Les FET Q3 et Q4 sont des redresseurs synchrones qui reconvertissent la forme d'onde de commutation du transformateur secondaire en courant continu. Les redresseurs synchrones éliminent les chutes de tension série associées aux redresseurs à semi-conducteurs, ce qui améliore le rendement. Ces FET redresseurs doivent être commandés de manière synchrone à l'aide des dispositifs de commutation de puissance primaires.

D'autres topologies d'onduleur incluent le pont complet, ou pont en H, avec quatre FET, ou le pont complet en cascade avec six FET, utilisé pour les convertisseurs triphasés. Toutes ces technologies utilisent une ou plusieurs paires de dispositifs de puissance. Ces paires sont connectées en série, comme les FET de la Figure 1.

Toutes ces topologies présentent deux problèmes critiques. Le premier est que les dispositifs de commutation haut potentiel (Q1) et bas potentiel (Q2) ne peuvent jamais être activés en même temps. Si cela se produit, il y a alors un court-circuit entre le bus 48 V et la terre. C'est ce qu'on appelle le « shoot-through », qui endommage en général les commutateurs. Ce phénomène peut être évité en contrôlant les temps de commutation de chaque dispositif de puissance de manière indépendante. Le but est de désactiver le dispositif actif avant d'activer le dispositif inactif.

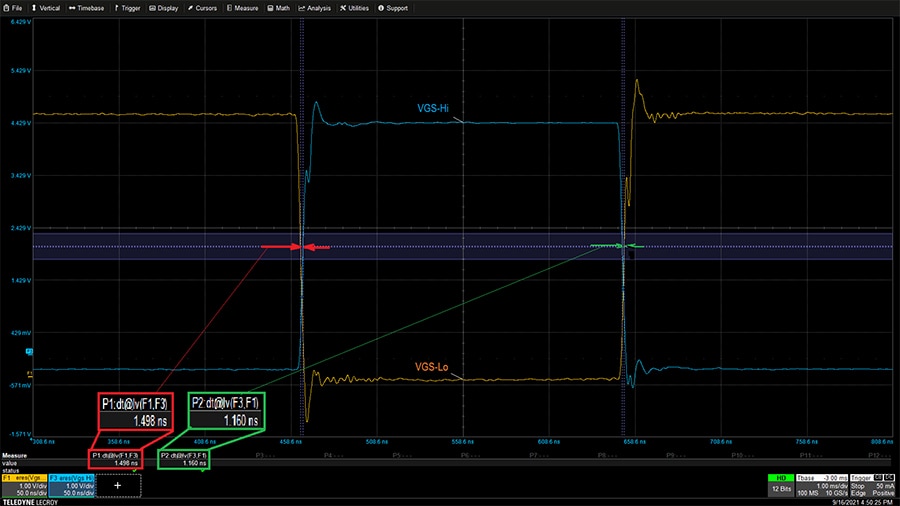

Le décalage entre les deux événements (activation et désactivation) est appelé « temps de récupération primaire ». Il se mesure en comparant les temps de transition de la tension grille-source (VGS) des FET haut potentiel et bas potentiel à la largeur d'impulsion maximale du contrôleur (Figure 2). Le décalage entre les deux ensembles de transitions correspond au temps de récupération.

Figure 2 : Le temps de récupération primaire se mesure en comparant les temps de transition de la tension grille-source (VGS) des FET haut potentiel et bas potentiel à la largeur d'impulsion maximum du contrôleur. Le décalage entre les deux ensembles de transitions correspond au temps de récupération. Dans cet exemple, il s'élève à 1,498 ns et 1,166 ns. (Source de l'image : Art Pini)

Figure 2 : Le temps de récupération primaire se mesure en comparant les temps de transition de la tension grille-source (VGS) des FET haut potentiel et bas potentiel à la largeur d'impulsion maximum du contrôleur. Le décalage entre les deux ensembles de transitions correspond au temps de récupération. Dans cet exemple, il s'élève à 1,498 ns et 1,166 ns. (Source de l'image : Art Pini)

Dans la Figure 2, le décalage entre la désactivation du FET bas potentiel (VGS Lo) et l'activation du FET haut potentiel (VGS Hi) est de 1,498 ns. Dans l'autre sens, lors de la désactivation du FET haut potentiel et de l'activation du FET bas potentiel, il y a un décalage de 1,166 ns. Si ces deux décalages mesurés sont positifs, le temps de récupération est acceptable. Notez que cette mesure est réalisée à la largeur d'impulsion maximum de la sortie du contrôleur PWM.

Lors du temps de récupération, aucun des dispositifs n'est conducteur. Il s'agit d'une perte liée au temps de récupération. Comme toutes les pertes, il est de plus en plus important de la maintenir à un niveau minimal.

Le deuxième problème critique consiste à coordonner le fonctionnement des redresseurs synchrones avec les opérations de commutation primaires.

Le contrôleur UCC28251PWR illustré à la Figure 1 peut contrôler des circuits en demi-pont ou en pont complet et fournit des décalages programmables aux signaux d'attaque de grille et aux sorties de redresseurs synchrones. L'UCC28251PWR contrôle le temps de récupération côté primaire et inclut également une protection contre la surintensité cycle-à-cycle. Les décalages entre les sorties primaires et les signaux d'attaque des redresseurs synchrones secondaires, appelés temps de récupération secondaire, sont programmables de manières indépendantes via deux résistances externes.

Le contrôleur PWM est utilisé en conjonction avec un circuit intégré d'attaque de grille en demi-pont côté primaire, l'UCC27210DDAR de Texas Instruments. Ce circuit intégré commande les deux entrées grille-source des deux FET à canal N dans cette configuration en demi-pont. Il a un impact sur le temps de récupération primaire en raison de son temps de propagation inhérent de 18 ns (typique). Le problème du temps de propagation est minimisé en adaptant le décalage entre les deux sorties d'attaque de grille. L'adaptation des sorties du circuit d'attaque de grille UCC27210DDAR se fait en 2 ns. Un circuit d'attaque de grille de la même gamme présentant les mêmes caractéristiques de temporisation est utilisé pour commander les FET redresseurs synchrones.

Conclusion

L'adoption des systèmes 48 V présente des avantages inhérents en termes de rendement, de taille et de poids, mais les concepteurs doivent comprendre la cause du temps de récupération et savoir comment le minimiser. Comme illustré, il existe des circuits intégrés à usage spécifique dotés des fonctions nécessaires pour garantir le bon fonctionnement des convertisseurs de puissance 48 V. Ils contrôlent les temps de récupération primaire et secondaire, éliminant ainsi les principaux problèmes possibles pour les topologies en demi-pont et en pont complet.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum