Intégrez RISC-V à votre cours d'architecture informatique en utilisant RVfpga !

Chers professeurs et amis,

Les cours en ligne sont pratiques et nous ont sauvés pendant la pandémie, mais rien ne vaut les cours en personne, en classe ! Il n'y a rien de mieux que ce sentiment de terrain immersif et la mission partagée avec des collègues qui essaient tous de maîtriser le même sujet.

Nous sommes au cœur d'une série mondiale d'ateliers pour « former les enseignants » à l'utilisation de RISC-V dans les cours d'architecture informatique et la conception de systèmes sur puce (SoC). Nous avons commencé aux États-Unis l'année dernière et avons également assisté à plusieurs événements européens. L'atelier de décembre dans la Silicon Valley a réuni près de 60 enseignants et formateurs, et nous tenions à le souligner !

Nous mettons à présent le cap vers l'Est : direction Israël, le Japon, Taïwan, la Corée et la Chine.

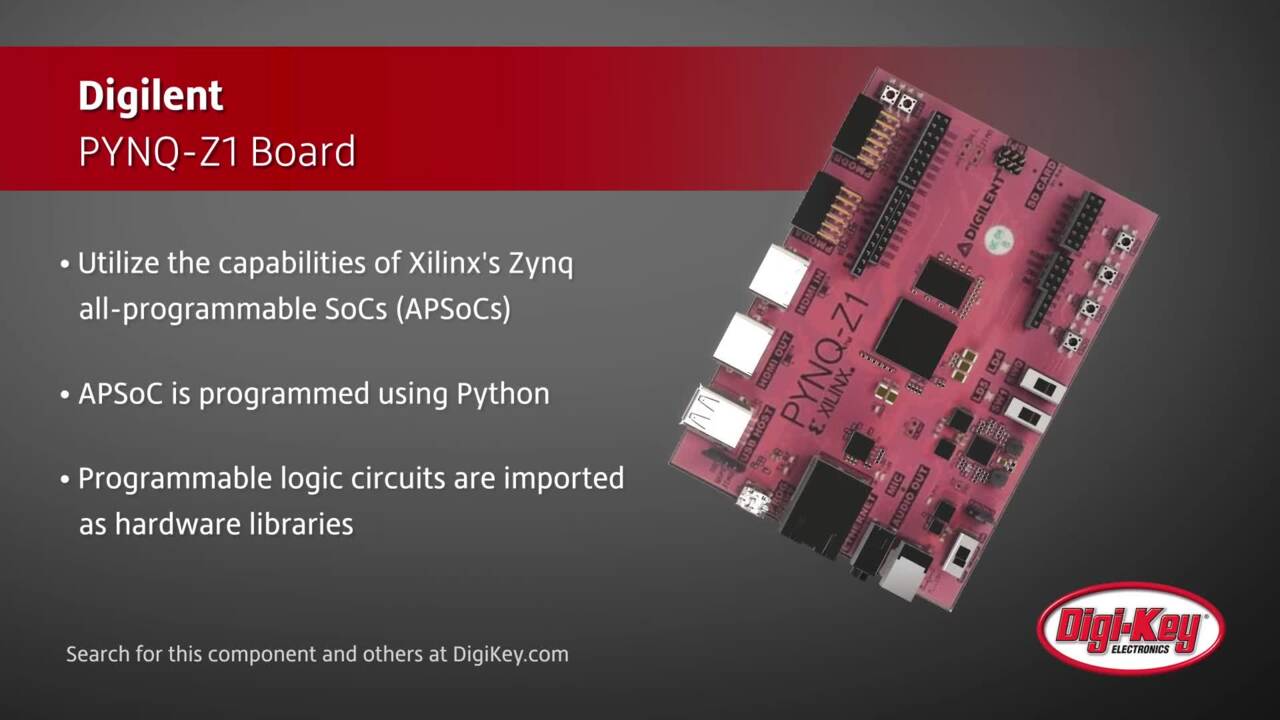

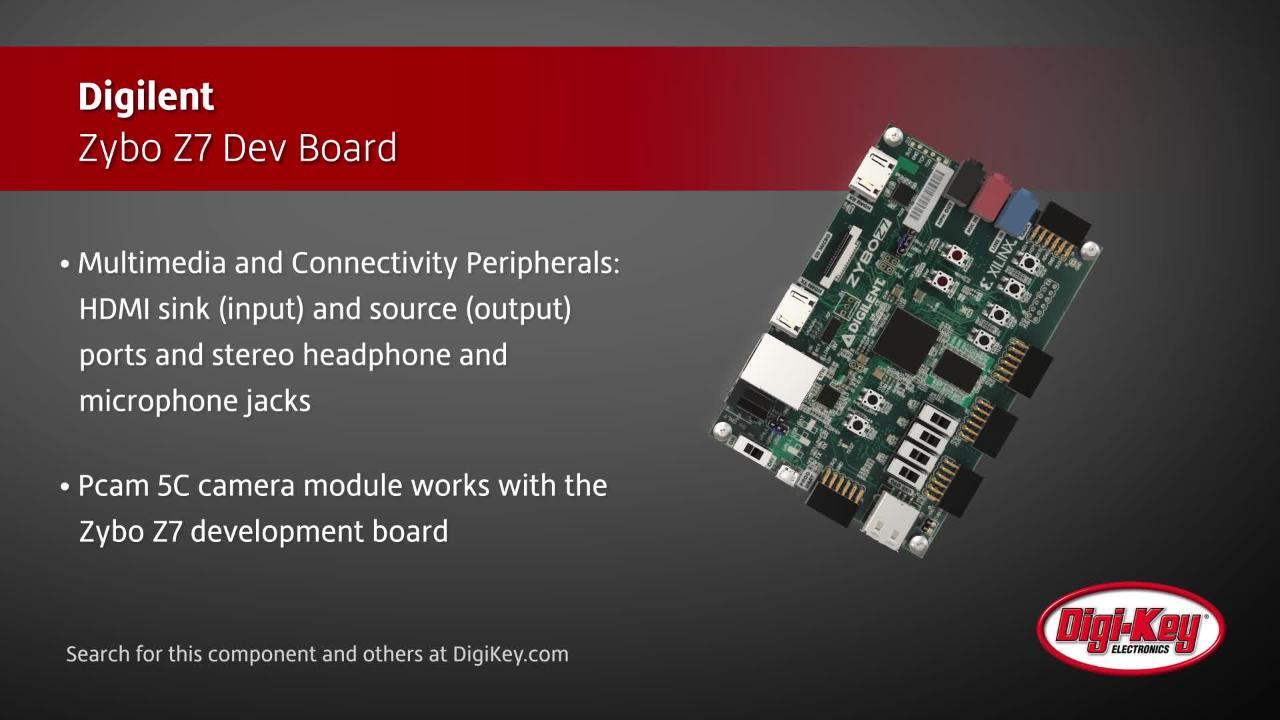

Nos partenaires RVfpga, notamment DigiKey, travaillent avec nous pour rendre cela possible !

Pour ce faire, nous vous demandons une journée de votre temps afin que vous puissiez permettre à la prochaine génération d'étudiants en informatique et en ingénierie d'acquérir une expertise réelle en architecture informatique et en architecture de jeu d'instructions RISC-V.

Qu'est-ce que RVfpga ?

Cet atelier RVfpga d'une journée en présentiel présente un système RISC-V commercial destiné à un FPGA, discute de la théorie, de l'architecture et de la structure du cours, et montre comment utiliser les laboratoires pratiques dans le cadre du cours RVfpga complet. Le cours explore les principes fondamentaux de l'architecture informatique en utilisant le cœur SweRV EH1 RISC-V open-source, entièrement vérifié et déjà intégré à la puce, de Western Digital, destiné à un FPGA Artix 7 de Xilinx sur la carte de développement Nexys A7 de Digilent. Tout le monde profitera d'une expérience pratique de la plateforme FPGA et des outils logiciels, ce qui vous permettra de démarrer rapidement à votre retour à l'université.

Le SweRV n'est pas un « cœur éducatif ». Il est concret, utilisé à l'intérieur des processeurs graphiques d'Imagination et des disques SSD de Western Digital.

Qu'allez-vous apprendre ?

- L'atelier montrera comment mettre rapidement en place le système FPGA RISC-V et les outils RISC-V.

- Nous décrirons chacun des laboratoires et explorerons une partie d'entre eux dans la pratique.

- Nous discuterons également de la façon d'intégrer RVfpga dans votre programme d'études.

Les sujets spécifiques incluent les suivants :

- Installation des outils (que nous encourageons avant l'atelier)

- Application du cœur SweRV EH1 RISC-V et du SoC sur un FPGA

- Programmation du SoC RISC-V

- Ajout de fonctionnalités supplémentaires au SoC RISC-V

- Analyse et modification de la hiérarchie de la mémoire et du cœur RISC-V

À qui s'adresse cette formation ?

- Il s'agit principalement d'un événement visant à « former les enseignants », qui offre une grande valeur aux enseignants en génie électrique, sciences informatiques et génie informatique souhaitant enseigner l'architecture informatique.

- Les formateurs dans les entreprises commerciales et les diplômés qui envisagent de faire carrière dans l'enseignement ou de devenir concepteurs de puces le trouveront également utile.

Réseaux

Il s'agit d'une excellente occasion de tisser de nouveaux liens et de renouveler les liens existants avec d'autres professeurs désireux de maintenir leurs cours à jour. Parlez-en autour de vous et invitez vos collègues.

Vous rencontrerez des innovateurs qui évaluent RISC-V pour les projets de start-up, ainsi que des formateurs en entreprise qui ont besoin de supports adaptés pour former leurs nouvelles recrues.

Nos formateurs :

Grâce à notre partenariat avec des universitaires qualifiés et des experts d'autres entreprises travaillant sur RISC-V, nous pouvons bénéficier de l'expertise des meilleurs formateurs au monde !

ASEE Baltimore et UCSC Santa Clara

Sarah Harris est professeure de génie électrique et informatique à l'Université du Nevada, à Las Vegas. Sarah Harris a obtenu son master et son doctorat à l'université de Stanford. Elle est co-auteure de trois manuels populaires : Digital Design and Computer Architecture, 2nd Edition (2007), ARM Edition (2015) et RISC-V Edition (2021). Ses recherches portent sur l'architecture informatique et les applications de systèmes embarqués, l'apprentissage automatique, le génie biomédical et la robotique.

Taïwan

Michio Abe est un expert reconnu en architectures de processeur RISC. Il est directeur des ventes et des solutions pour le Japon chez MIPS LLC. Il a débuté sa carrière chez NEC en 1985, où il a participé au développement de processeurs MIPS, notamment des processeurs MIPS originaux de NEC en 1991. Il a ensuite développé des SoC embarqués dans les véhicules avec MIPS, et d'autres cœurs et architectures. Il est responsable de la promotion et du marketing des processeurs MIPS au Japon depuis 2015, à l'origine pour Imagination Technologies et désormais en tant qu'entreprise indépendante.

Notre organisateur local est le professeur Brian Lin de l'université nationale des sciences et des technologies de Taïwan (NTUST) à Taipei.

FPL 2023 Göteborg

Daniel A. Chaver Martínez a obtenu un diplôme en physique à l'Université de Saint-Jacques-de-Compostelle (USC) en 1998 et un diplôme d'ingénieur en électronique à l'Université Complutense de Madrid (UCM) en 2000. Il a préparé son doctorat de 2000 à 2006 à l'UCM. Il dispense de nombreux cours liés à l'architecture informatique depuis 2000. Ses centres d'intérêt de recherche actuels incluent les techniques architecturales pour les mémoires caches et non volatiles, ainsi que la planification des systèmes d'exploitation pour les multiprocesseurs asymétriques. Depuis 2015, il collabore avec Imagination Technologies dans le cadre du développement de certains de leurs processeurs et supports pédagogiques.

Ateliers (date et lieu)

| Date | Lieu/événement | Ville, pays | Format | Inscription |

|

25-28 juin |

Conférence ASEE | Baltimore, États-Unis |

Papier : RVfpga, cours sur l'architecture informatique et MOOC avec SoC RISC-V appliqué à un FPGA et simulation |

https://nemo.asee.org/public/conferences/327/registration |

| 5 et 6 juillet |

NTUST |

Taipei, Taïwan |

DEUX ateliers RVfpga d'une journée en présentiel en anglais (avec support en mandarin et japonais) |

https://www.eventbrite.co.uk/e/549461984587 [eventbrite.co.uk] https://www.eventbrite.co.uk/e/602617443997 [eventbrite.co.uk] |

| Octobre, date à confirmer | Université du Zhejiang |

Hangzhou, Chine |

Atelier RVfpga d'une demi-journée en présentiel en chinois Formateurs : professeurs Liu, Peng & Xi, Yuhao, université du Zhejiang, Hangzhou |

À venir |

| 5 septembre, 9h - 13h |

FPL 2023 |

Université Chalmers, Göteborg, Suède |

Atelier RVfpga d'une demi-journée en présentiel en anglais (Inscription à l'atelier seulement, disponible ~$120) |

https://2023.fpl.org/attend/registration |

| 9 novembre |

Centre de formation UCSC Silicon Valley |

Santa Clara, Californie, États-Unis |

Atelier RVfpga d'une journée en présentiel en anglais |

https://www.eventbrite.co.uk/e/rvfpga-understanding-computer-architecture-in-person-workshop-nov-9th-tickets-654132025497 |

Plus d'informations

- À propos de l'IUP et de RVfpga : https://university.imgtec.com/teaching-download/

- Blog RISC-V : https://blog.imaginationtech.com/how-rvfpga-understanding-computer-architecture-will-give-under-grads-real-world-skills

- Présentation de RISC-V : https://www.digikey.fr/fr/resources/risc-v

Nous avons hâte de vous rencontrer en personne !

Cordialement,

Robert C.W. Owen

Consultant principal : programme universitaire mondial

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum