Pourquoi le bus I2C simplifie la connexion de circuits intégrés — et comment l'utiliser

Avec la contribution de Rédacteurs nord-américains de DigiKey

2020-04-07

Les communications et le contrôle entre circuits intégrés utilisant un bus parallèle sur une carte à circuit imprimé ne sont pas pratiques. Même un processeur 8 bits nécessiterait 16 lignes rien que pour les données et bien d'autres pour un bus d'adresses. C'est encore plus problématique si plusieurs circuits intégrés doivent être sur un bus de communication partagé. L'espace est insuffisant pour toutes les pistes de circuit imprimé. La solution consiste à relier les circuits intégrés à l'aide d'un bus de communication série comme le bus Inter-Integrated Circuit (I2C), un bus série à deux fils qui résout ce problème.

Cet article décrit les origines du bus I2C et explique comment il fonctionne pour fournir une liaison série efficace entre les circuits intégrés. Il aborde ensuite l'implémentation physique du bus I2C, la structure du protocole et les applications courantes de ce bus de communication omniprésent. Des exemples de solutions et d'interfaces I2C de Microchip Technology sont utilisés à des fins de démonstration. L'article aborde également les similitudes et les différences entre I2C et System Management Bus (SMBus).

Présentation du bus I2C

Le bus I2C a été développé par Phillips Semiconductors, désormais NXP Semiconductors, au début des années 1980 comme un simple bus bidirectionnel à deux fils pour des communications et un contrôle efficaces des circuits intégrés sur une carte à circuit imprimé commune. La première spécification a été finalisée en 1992, et le bus est depuis devenu de fait une norme incluse dans les composants fournis par plus de 50 fabricants de circuits intégrés. Ce vaste déploiement permet une approche système de la conception où les circuits intégrés peuvent être facilement inclus dans la structure de bus I2C sans nécessiter de conception personnalisée. Plusieurs autres bus spécialisés, comme SMBus et Power Management Bus (PMBus), entre autres, partagent la même architecture de base.

Le bus I2C peut relier plusieurs circuits intégrés et capteurs, car il s'agit d'un bus adressable. Un champ d'adresse à sept ou dix bits permet l'envoi de messages vers un dispositif sélectionné par le dispositif maître. Le bus I2C d'origine présentait une fréquence d'horloge maximale de 100 kilohertz (kHz), mais au fil des années, des modes de fonctionnement à fréquence plus élevée ont repoussé cette limite à 3,4 mégahertz (MHz).

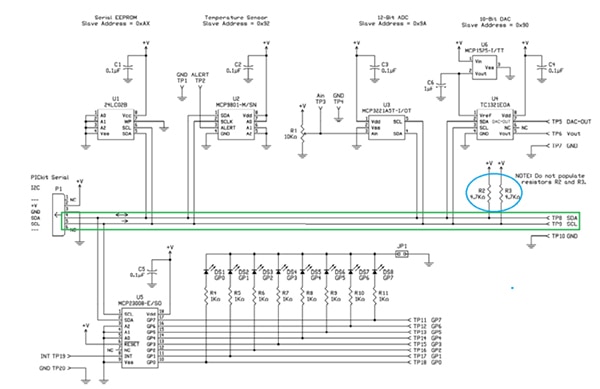

Le bus I2C utilise une ligne de données série (SDA) désignée à deux fils et une ligne d'horloge série (SCL). Les lignes SDA et SCL sont des lignes bidirectionnelles à drain/collecteur ouvert et sont connectées au bus d'alimentation positive via une source de courant ou une résistance d'excursion haute. Plusieurs dispositifs peuvent être connectés au bus, le nombre maximal étant limité par la capacité du bus. Un dispositif maître contrôle le bus, et chaque dispositif sur le bus possède une adresse unique. Le dispositif maître peut à la fois émettre et recevoir des données par l'intermédiaire du bus (Figure 1). I2C prend en charge un fonctionnement à plusieurs maîtres avec détection de collision et arbitrage pour empêcher deux dispositifs maîtres ou plus d'initialiser des transferts de données en même temps. Toutefois, cet article se concentre sur les configurations à un seul maître.

Figure 1 : Schéma d'une carte à circuit imprimé de Microchip Technology qui implémente le bus I2C et le connecte à cinq dispositifs différents. Le dispositif maître est hors carte via le connecteur P1. Les lignes SCL et SDA sont encadrées en vert et les deux résistances d'excursion haute sont entourées en bleu. (Source de l'image : Microchip Technology)

Figure 1 : Schéma d'une carte à circuit imprimé de Microchip Technology qui implémente le bus I2C et le connecte à cinq dispositifs différents. Le dispositif maître est hors carte via le connecteur P1. Les lignes SCL et SDA sont encadrées en vert et les deux résistances d'excursion haute sont entourées en bleu. (Source de l'image : Microchip Technology)

La Figure 1 montre le schéma d'une carte de démonstration I2C PKSERIAL-I2C1 de Microchip Technology. Cette carte implémente le bus I2C avec cinq dispositifs différents : une mémoire EEPROM, un capteur de température, un convertisseur analogique-numérique (CAN) 12 bits, un convertisseur numérique-analogique (CNA) 10 bits et un convertisseur série-parallèle 8 bits. Le dispositif maître ne se trouve pas sur la carte et est connecté via le connecteur P1. Les lignes de bus SDA et SCL sont encadrées en vert et les résistances d'excursion haute sont entourées en bleu.

Les niveaux SDA et SCL sont en général un pourcentage fixe de la tension d'alimentation positive, généralement appelée VDD. Les niveaux de référence sont définis à 70 % et 30 % de VDD pour le « 1 » logique (haut) et le « 0 » logique (bas), respectivement.

Les signaux d'horloge se produisent en rafales, avec une horloge pour chaque bit de données transféré. Les données sur la ligne SDA doivent être valides lorsque l'horloge est à l'état haut. Les données peuvent être modifiées uniquement lorsque l'horloge est à l'état bas.

Du point de vue d'un concepteur, les nouveaux projets sont simplifiés, car les interfaces I2C sont intégrées dans les circuits intégrés et il n'est donc pas nécessaire de concevoir une interface. Il suffit de connecter chaque dispositif directement au bus. Les circuits intégrés peuvent être ajoutés ou retirés du bus sans affecter les autres circuits (en supposant que le nombre total de circuits intégrés ne dépasse pas la limite de capacité). Le bus simple à deux fils réduit le nombre de broches sur chaque circuit intégré et le nombre de pistes sur la carte à circuit imprimé.

Le protocole I2C

Le bus est orienté 8 bits et communique en octets. Comme indiqué précédemment, la fréquence d'horloge maximum d'origine était de 100 kHz, ce que l'on appelle désormais le mode standard (Standard Mode). Le bus prend maintenant en charge 400 kilobits par seconde (kbit/s) en Fast Mode (mode rapide), jusqu'à 1 mégabit par seconde (Mbit/s) en Fast Mode Plus (mode rapide plus) et jusqu'à 3,4 Mbits/s en High Speed Mode ou Hs-Mode (mode haute vitesse).

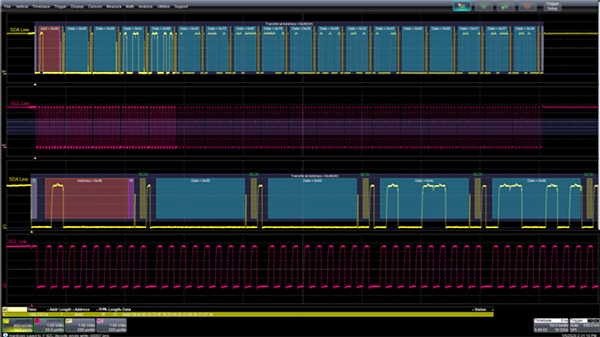

Un transfert typique sur le bus (Figure 2) permet de visualiser parfaitement le protocole I2C. La source de l'image d'écran est un oscilloscope WS4KHD-EMB TD de Teledyne LeCroy avec option de déclenchement et de décodage des données série à faible vitesse. Cette option d'oscilloscope peut déclencher et décoder jusqu'à 19 interfaces de données série à faible vitesse, y compris I2C.

Figure 2 : Un paquet de données I2C typique composé d'un bit de départ, d'un champ d'adresse, d'un bit d'acquittement, de 17 octets de données avec chacun son propre bit ACK, et enfin d'un bit d'arrêt. Chaque champ est identifié par un cache de couleur. Le tracé du haut (jaune) représente le paquet SDA complet, en dessous duquel se trouve l'horloge SCL (rouge). Les troisième et quatrième tracés sont des vues étendues horizontalement des deux signaux. (Source de l'image : DigiKey Electronics)

Figure 2 : Un paquet de données I2C typique composé d'un bit de départ, d'un champ d'adresse, d'un bit d'acquittement, de 17 octets de données avec chacun son propre bit ACK, et enfin d'un bit d'arrêt. Chaque champ est identifié par un cache de couleur. Le tracé du haut (jaune) représente le paquet SDA complet, en dessous duquel se trouve l'horloge SCL (rouge). Les troisième et quatrième tracés sont des vues étendues horizontalement des deux signaux. (Source de l'image : DigiKey Electronics)

L'oscilloscope peut se déclencher en fonction d'événements série spécifiques, notamment : départ, arrêt, acquittement (ACK) manquant, transfert de données EEPROM, adresse, données, adresse et données et longueur de trame. Les éléments de protocole de la norme de données série sont identifiés par un cache de couleur. Chaque champ du protocole est décodé en binaire, hexadécimal ou ASCII avec le code sélectionné affiché dans le cache.

Le signal SDA apparaît sous forme de tracé jaune, tandis que le signal SCL est affiché sous forme de tracé rouge. Les caches gris indiquent les fonctions de départ et d'arrêt. Le cache rouge brique marque les données d'adresse, le champ bleu correspond aux données du paquet, et les caches vert olive marquent les fonctions ACK.

Le tracé du haut montre le paquet SDA I2C dans son intégralité, du départ à l'arrêt. Juste en dessous se trouve le signal SCL correspondant. Le troisième tracé est un tracé agrandi du signal SDA en fonction du temps, et en dessous se trouve le signal SCL synchrone.

Les lignes SDA et SCL restent à l'état haut entre les transferts lorsque le bus est libre. Le signal SCL est composé de rafales de neuf impulsions à la fréquence d'horloge, une pour chaque bit de données transféré et une autre pour le bit ACK.

Toutes les transactions du bus commencent par un bit de départ généré par le dispositif maître, représenté dans le tracé SDA agrandi sous forme de cache gris. Le départ est indiqué par le dispositif maître qui fait passer la ligne SDA à l'état bas tandis que la ligne SCL est dans un état haut. Lorsque le dispositif maître émet le bit de départ, le bus est considéré comme étant occupé. Le dispositif maître peut émettre plusieurs départs, une situation dans laquelle les départs suivants sont souvent appelés des redémarrages.

Tous les transferts de données présentent une longueur de 8 bits (un octet), chacun étant suivi par un bit ACK. Les bits sont transmis avec le bit le plus significatif (MSB) en premier. Chaque transfert d'octet doit être reconnu. Si le dispositif esclave est occupé et ne peut pas recevoir ni transmettre de données, il peut faire passer la ligne SCL à l'état bas. Cela oblige le dispositif maître à entrer dans un état d'attente jusqu'à ce que le dispositif esclave libère la ligne SCL.

Le bit ACK est formé après que le dispositif émetteur libère la ligne SDA avant la neuvième impulsion d'horloge d'acquittement. Si le dispositif de réception a reçu l'octet de données, il fait passer la ligne SDA à l'état bas. Dans la vue agrandie de la ligne SDA de la Figure 2, il y a une petite pointe juste avant la neuvième impulsion d'horloge, qui correspond à la libération de la ligne SDA pour lui permettre de revenir à l'état haut. Le récepteur fait passer la ligne SDA à l'état bas en générant le signal ACK, qui est marqué symboliquement par le cache vert olive. Si le récepteur ne fait pas passer la ligne SDA à l'état bas avant la neuvième impulsion d'horloge, il s'agit d'une réponse de non-acquittement (NACK). Si une réponse NACK se produit, le dispositif maître peut générer un signal d'arrêt et annuler le transfert ou émettre un nouveau départ pour réessayer.

Immédiatement après la condition de départ, une adresse esclave est émise. Cela est indiqué par un cache rouge brique. Il existe deux formats d'adresse possibles : 7 bits ou 10 bits, l'adresse à 7 bits étant la plus courante. Les 7 premiers bits après le départ représentent les données d'adresse. Le 8e bit indique la direction des données (lecture ou écriture). Une écriture est indiquée par la ligne SDA à l'état bas, tandis que la ligne SDA à l'état haut à ce moment indique une opération de lecture. L'adressage 10 bits utilise les deux premiers octets après la condition de départ. I2C réserve plusieurs adresses pour des fonctions internes. Les données d'adresse de décodage s'affichent dans la zone de cache d'adresse au format binaire, hexadécimal ou ASCII.

Les caches bleus marquent les transferts de données. Chacun présente une longueur de huit bits et est suivi d'une réponse ACK/NACK. Le nombre d'octets de données dans un paquet I2C est illimité, mais la Figure 2 en contient 17. Les données décodées, comme le décodage de l'adresse, s'affichent dans la zone de cache de données. Le flux de données est suivi par un bit d'arrêt généré par le dispositif maître à la fin du transfert de données, indiqué par un cache gris sur le tracé de données du haut. Le bit d'arrêt est une transition bas-haut sur la ligne SDA, tandis que la ligne SCL est dans un état haut. Après le signal d'arrêt, le bus est à nouveau libre.

Le tableau en bas de l'écran résume toutes les informations sur le paquet de données concerné, notamment la durée depuis le déclenchement, la longueur d'adresse, l'adresse, l'opération de lecture ou d'écriture, la longueur du paquet et un résumé du contenu des données. Le nombre d'entrées dans le tableau correspond au nombre de paquets I2C acquis par l'oscilloscope, qui équivaut ici à une seule ligne.

Si une erreur de protocole se produit, elle est indiquée par une zone rouge vif derrière les autres zones de cache de protocole.

Dispositifs I2C

L'un des plus grands avantages du bus I2C est le nombre extrêmement important de dispositifs qui l'ont intégré dans leur conception. La carte de démonstration de Microchip Technology fournit quelques exemples des types de circuits intégrés qui intègrent le bus I2C ou l'un de ses dérivés, comme le SMBus.

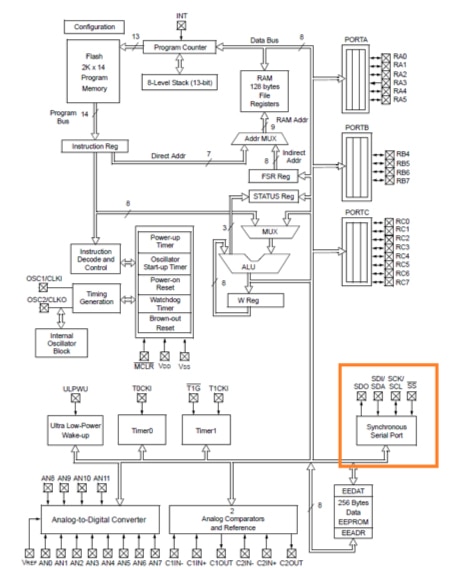

Le PIC16F677 de Microchip Technology est un microcontrôleur 8 bits qui est utilisé dans de nombreuses conceptions embarquées. Il implémente un port série synchrone qui peut être contrôlé pour communiquer avec l'interface périphérique série (SPI) ou le bus I2C vers d'autres contrôleurs ou périphériques (Figure 3).

Figure 3 : Le PIC16F677 de Microchip Technology est un microcontrôleur 8 bits qui inclut un port série synchrone (encadré en orange) capable d'être programmé en tant qu'interface SPI ou que bus I2C. (Source de l'image : Microchip Technology)

Figure 3 : Le PIC16F677 de Microchip Technology est un microcontrôleur 8 bits qui inclut un port série synchrone (encadré en orange) capable d'être programmé en tant qu'interface SPI ou que bus I2C. (Source de l'image : Microchip Technology)

Ce microcontrôleur prend en charge le mode maître et le mode esclave d'I2C en utilisant un adressage à 7 ou 10 bits. Il utilise la broche SCK/SCL pour le signal d'horloge SCL I2C et la broche SDI/SDA pour le signal de données.

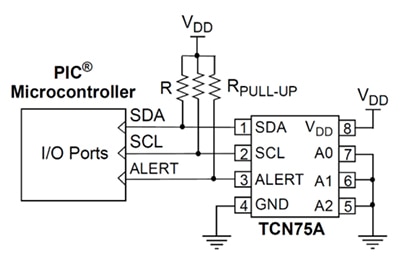

Ces deux broches sont connectées aux lignes SCL et SDA sur le bus I2C pour permettre la communication avec d'autres dispositifs. La connexion est souvent établie avec un capteur basé sur I2C, comme le capteur de température série à deux fils TCN75AVOA713 de Microchip Technology (Figure 4).

Figure 4 : Le capteur de température TCN75A de Microchip Technology est directement connecté au microcontrôleur PIC16F677 pour communiquer des données de température. (Source de l'image : Microchip Technology)

Figure 4 : Le capteur de température TCN75A de Microchip Technology est directement connecté au microcontrôleur PIC16F677 pour communiquer des données de température. (Source de l'image : Microchip Technology)

Doté d'une capacité de communication série, ce capteur de température présente des fonctionnalités accrues. Ses registres internes programmables par l'utilisateur peuvent être utilisés pour définir la résolution de mesure de température, le mode d'arrêt écoénergétique et même la sortie d'alerte pour indiquer lorsque la plage de températures dépasse les limites prédéfinies.

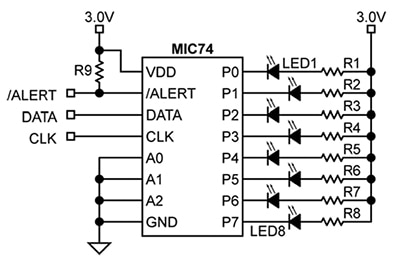

Il existe également des dispositifs qui décodent le flux de données série I2C et le divisent en données parallèles. Prenons par exemple le contrôleur de ventilateur et l'expanseur E/S à deux fils MIC74YQS-TR de Microchip Technology (Figure 5).

Figure 5 : L'expanseur E/S MIC74YQS-TR de Microchip Technology convertit le flux de données série en huit lignes E/S parallèles indépendantes. (Source de l'image : Microchip Technology)

Figure 5 : L'expanseur E/S MIC74YQS-TR de Microchip Technology convertit le flux de données série en huit lignes E/S parallèles indépendantes. (Source de l'image : Microchip Technology)

Ce circuit intégré est un expanseur E/S entièrement programmable fournissant huit lignes E/S indépendantes. Les lignes E/S peuvent être programmées individuellement en tant qu'entrée ou sortie. La Figure 5 montre le MIC74YQS-TR qui commande huit LED sous le contrôle du bus série. Cela est similaire à l'utilisation du MCO23008 sur la carte de démonstration I2C de la Figure 1. Le MIC74YQS-TR, en conjonction avec un régulateur de puissance, peut également implémenter un contrôle de vitesse de moteur de ventilateur en utilisant ses quatre bits les plus significatifs.

SMBus et I2C

L'entrée série vers l'expanseur E/S est conçue pour le SMBus, mais est également compatible avec le bus I2C. La spécification SMBus est basée sur I2C et a été définie par Intel et Duracell en 1994. La principale différence est que les niveaux logiques d'I2C en mode standard sont relatifs à VDD tandis que ceux de SMBus sont fixes. Dans la plupart des cas, avec VDD entre 3 V et 5 V, l'expérience a montré qu'il ne s'agissait pas d'un problème.

Autre différence : SMBus est limité à des fréquences d'horloge de 100 kHz maximum, tandis qu'I2C dispose de plusieurs modes qui prennent en charge des fréquences d'horloge supérieures. En ce qui concerne la compatibilité du bus, cela limite la fréquence d'horloge maximum à 100 kHz ou au mode d'horloge standard I2C.

De ce fait, à l'exception de situations très spéciales, SMBus et I2C sont compatibles.

Conclusion

Le bus I2C et ses dérivés sont omniprésents dans des centaines de circuits intégrés de tous types, ce qui permet de les connecter facilement dans des conceptions et applications multifacettes. Le couplage de signaux mixtes et de capteurs analogiques étend la portée des systèmes embarqués basés sur microcontrôleur. Et ce, grâce à une interface numérique série à deux fils simple.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.