Pourquoi et comment utiliser l'interface périphérique série pour simplifier les connexions entre plusieurs dispositifs

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-02-14

Les systèmes embarqués utilisent un ou plusieurs processeurs ou microcontrôleurs pour exécuter des opérations spécialisées dans un système plus complexe. Ces contrôleurs embarqués doivent communiquer avec d'autres composants, capteurs et même contrôleurs du système. Bien qu'ils soient courants, les protocoles et interfaces série complexes peuvent être très difficiles à programmer et à dépanner, surtout si le nombre de dispositifs avec lesquels ils communiquent est faible.

Les concepteurs ont besoin de microcontrôleurs, de périphériques et de capteurs dotés d'une interface numérique dispositif-à-dispositif simple, pouvant gérer des données de longueur arbitraire à haute vitesse et éliminer les tâches de programmation orientée protocole complexes.

La solution simple est de choisir des contrôleurs avec une interface périphérique série (SPI), pour interfacer le contrôleur avec quelques capteurs ou circuits intégrés périphériques locaux. Il s'agit d'une interface synchrone simple qui utilise un adressage matériel et fonctionne à une fréquence d'horloge atteignant 50 MHz. La SPI n'utilise pas de protocole compliqué nécessitant un adressage et une vérification d'état. Il s'agit plutôt d'une interface de base pour un transfert de données rapide, sans le traitement de programmation associé à un bus d'interface plus sophistiqué.

Cet article parle des principes de base de l'interface SPI, y compris ses nombreux modes de fonctionnement. Il présente ensuite des microcontrôleurs et d'autres dispositifs intégrant une interface SPI, et montre comment l'appliquer.

Présentation de l'interface SPI

L'interface SPI a été développée par Motorola (qui fait maintenant partie de NXP Semiconductors) vers 1985. Il s'agit d'une interface série synchrone conçue pour une communication à courte distance entre dispositifs. Depuis, elle est devenue une norme de facto utilisée par de nombreux fabricants de semi-conducteurs, surtout dans les microcontrôleurs et les microprocesseurs.

La raison de la popularité de la SPI réside dans ses nombreux avantages. D'abord, c'est une interface d'adressage matériel simple qui offre une totale flexibilité sur le nombre de bits transférés. Elle utilise un modèle maître-esclave à maître unique et peut gérer plusieurs dispositifs esclaves à l'aide de communications en duplex intégral fonctionnant à des fréquences d'horloge pouvant atteindre 50 MHz. Elle n'utilise pas de protocole standard et transfère uniquement des paquets de données, ce qui la rend idéale pour le transfert de longs flux de données.

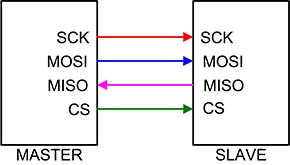

La SPI utilise un maximum de quatre lignes de signaux (Figure 1). Le dispositif maître, généralement un processeur ou un contrôleur, fournit et contrôle les lignes d'horloge (SCK) et de sélection de puce (CS). Le fonctionnement en multiplex intégral est géré par les lignes de données MOSI (maître sortant, esclave entrant) et MISO (maître entrant, esclave sortant). Dans une configuration simple à maître unique et esclave unique, la ligne de sélection de puce peut être éliminée et l'entrée CS vers l'esclave forcée à l'état logique actif. Si le dispositif esclave ne peut envoyer que des données (communication en semi-duplex), alors la ligne MOSI peut aussi être supprimée pour réduire davantage le nombre de signaux. Les données sont transférées par le signal d'horloge, de sorte que le transfert de données soit assimilé à un registre à décalage avec un bit décalé pour chaque horloge.

Figure 1 : La connexion SPI basique en duplex intégral utilise deux lignes de données (MOSI, MISO), une ligne d'horloge (SCK) et une ligne de sélection de puce (CS). La ligne MOSI d'un esclave est parfois appelée données esclaves entrantes (SDI). La ligne MISO peut être appelée données esclaves sortantes (SDO). (Source de l'image : DigiKey Electronics)

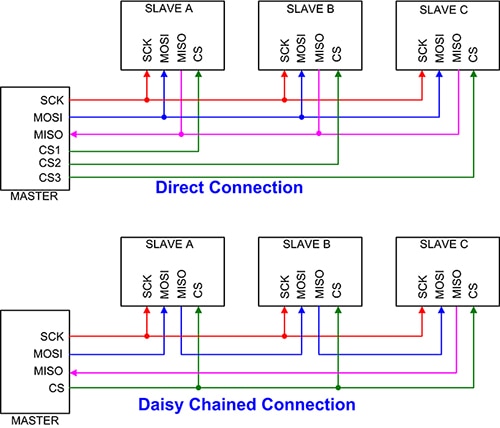

Il existe deux approches pour gérer plusieurs dispositifs esclaves (Figure 2).

Figure 2 : Deux configurations pour gérer un interfaçage multi-esclave. La connexion directe nécessite une sélection de puce pour chaque esclave. La connexion en chaîne utilise une sélection de puce unique et combine toutes les données dans une seule ligne. (Source de l'image : DigiKey Electronics)

La connexion directe utilise une ligne de sélection de puce pour chaque dispositif esclave. La plupart des microprocesseurs présentent trois ou quatre lignes de sélection de puce. Cela limite le nombre maximum d'esclaves au nombre de lignes de sélection de puce. Cela ne pose aucun problème dans la plupart des cas, mais si une conception requiert plus de dispositifs sur le bus, certains peuvent être configurés à l'aide de la méthode en chaîne. Cette dernière utilise une sélection de puce commune pour plusieurs dispositifs esclaves et les données sont diffusées dans une ligne de données commune. Encore une fois, en utilisant le modèle de dispositifs esclaves SPI comme registre à décalage, les données des esclaves sont propagées dans un flux série multiplexé.

Modes de cadencement SPI

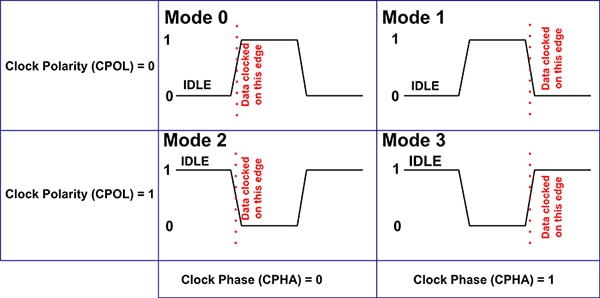

Le maître contrôle et génère l'horloge. Les deux attributs d'horloge sont la polarité d'horloge (CPOL) et la phase d'horloge (CPHA). Ils contrôlent le front d'horloge actif où le dispositif esclave est cadencé en fonction des données. CPOL = 0 définit l'horloge en veille à la logique 0. CPOL = 1 définit la mise en veille de l'horloge à la logique 1. CPHA = 0 définit le cadencement des données sur le front montant et CPHA = 1 définit le cadencement des données sur le front descendant (Figure 3).

Figure 3 : La sélection du mode de cadencement SPI fixe le front d'horloge actif sur lequel les données sont échantillonnées. (Source de l'image : DigiKey Electronics)

Les paramètres des lignes CPOL et CPHA du maître déterminent la polarité d'horloge et le front actif pour le cadencement des données. Le mode 1 est le plus couramment utilisé, mais les trois autres modes sont également accessibles au concepteur.

Les trois composants de signal d'un transfert SPI peuvent être observés sur un oscilloscope (Figure 4). Dans cet exemple, des paquets de données de 8 bits sont transférés. L'oscilloscope HDO4104A de Teledyne LeCroy, doté d'une option de décodage SPI série, est utilisé pour observer le transfert.

Figure 4 : Exemple d'un échange SPI affiché sur un oscilloscope HDO4104A de Teledyne LeCroy avec une option de décodage série. Les formes d'ondes sont les suivantes : le tracé supérieur désigne la ligne des données, le tracé du milieu l'horloge et le tracé inférieur, la sélection de puce. La bande bleue sur le tracé des données indique le contenu décodé au format hexadécimal. (Source de l'image : DigiKey Electronics)

L'horloge en mode 1 consiste en des groupes de huit impulsions avec une veille définie sur 0 (CPOL = 0) et des données cadencées sur le front descendant ou de descente (CPHA = 1). L'oscilloscope utilisé dans cet exemple présente une option de décodage série pour décoder le contenu des données. Le contenu des données est lu au format hexadécimal dans la bande colorée en bleu sur le tracé des données. Le décodage est associé uniquement aux données présentes durant l'assertion de la ligne de sélection de puce (niveau 0). Il y a 17 rafales d'horloge au total, mais seules 5 rafales correspondent aux états de sélection de puce actifs.

Le tableau sous les grilles d'affichage des formes d'ondes indique le contenu des données actives avec la durée de déclenchement de l'oscilloscope pour chaque paquet et la fréquence d'horloge mesurée, qui est de 100 kbps dans ce cas. Le nombre de cycles d'horloge dans chaque rafale définit le nombre de bits de données transférés du dispositif esclave.

Choix des E/S du microprocesseur

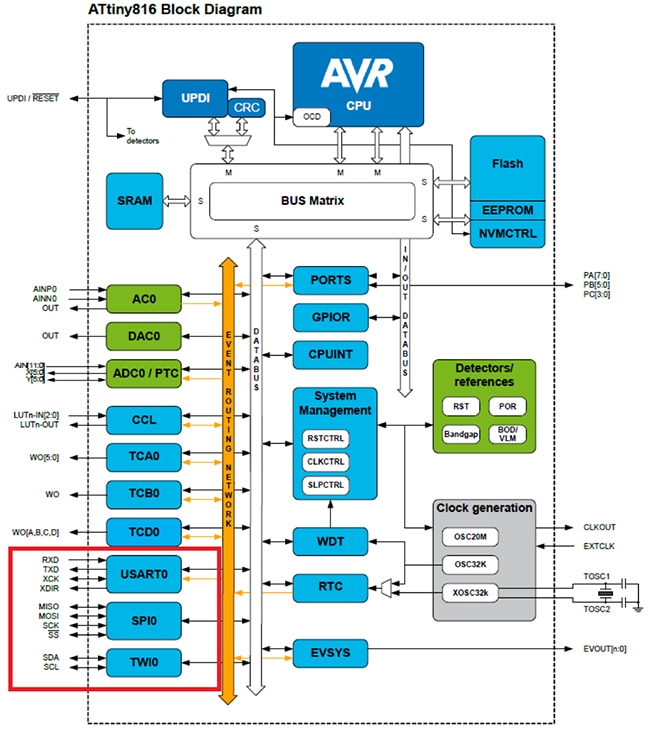

L'ATtiny816-MNR de Microchip Technology est un exemple typique de microcontrôleurs, car il prend en charge plusieurs interfaces E/S (Figure 5). Ce contrôleur utilise une architecture AVR® RISC basse consommation, hautes performances, et il peut fonctionner jusqu'à 20 MHz. Il est soutenu par jusqu'à 4 ou 8 Ko de mémoire Flash, 256 ou 512 octets de SRAM et 128 octets de mémoire EEPROM, dans un boîtier à 20 broches.

Figure 5 : Schéma fonctionnel du microcontrôleur ATtiny816 de Microchip Technology illustrant les ports E/S. Ce contrôleur inclut un port SPI et un port USART, ce dernier pouvant être configuré comme second SPI. (Source de l'image : Microchip Technology)

Côté interface, le microcontrôleur inclut un émetteur-récepteur synchrone et asynchrone universel (USART), une interface à deux fils (TWI) compatible I2C et l'interface SPI. L'USART peut être configuré comme un second port SPI.

L'interface SPI permet une communication en duplex intégral entre le dispositif AVR et les périphériques ou entre plusieurs microcontrôleurs. Le périphérique SPI peut être configuré comme maître ou esclave, ce qui active la communication entre les microcontrôleurs.

Capteurs basés SPI

En plus de la profusion de microprocesseurs et microcontrôleurs intégrant une SPI, de nombreux capteurs fournissent des données numériques via SPI. Par exemple, le capteur de température numérique accessible en série TC77-3.3MCTTR de Microchip Technology est conçu pour les applications compactes et économiques. Le TC77 couvre une plage de températures de -55°C à +125°C. Il fonctionne sur une alimentation de 2,7 V à 5,5 V, consomme 250 µA en fonctionnement et 1 µA avec le mode d'arrêt basse consommation disponible.

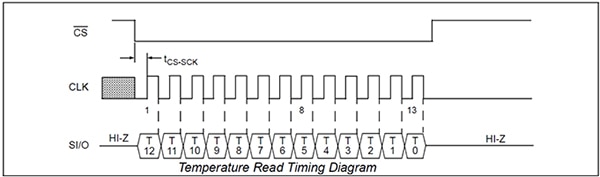

Dans une application typique, le capteur de température se connecte au processeur via une connexion SPI standard. Ses données de température sont formatées en mot numérique de 13 bits comme illustré dans la Figure 6.

Figure 6 : Le TC77 de Microchip Technology est un capteur de température compact, économique et simple à utiliser. Il peut être rapidement connecté au contrôleur ou au processeur pour transférer les lectures de température en mots numériques de 13 bits. Comme l'indique le schéma de temporisation, la communication est initiée par l'assertion de la ligne CS à une logique 0. (Source de l'image : Microchip Technology)

La Figure fournit un schéma de temporisation de l'opération de lecture du registre de température du TC77. La communication est initiée par l'assertion de la ligne CS à une logique 0. Le capteur transmet ensuite le premier bit de données. Le microcontrôleur lit les données entrantes sur le front de montée de SCK. Le front de descente de SCK est ensuite utilisé pour transférer le reste des données du capteur. Il s'agit d'un transfert en mode 1, comme dans l'exemple précédent, mais avec un mot de données plus long.

Extension de la portée de l'interface SPI

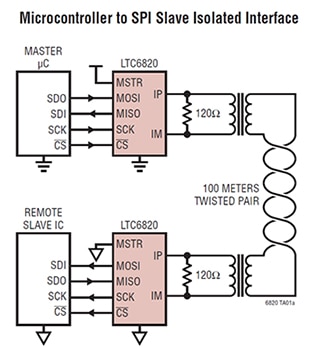

Outre l'inclusion de l'interface SPI dans de nombreux microprocesseurs et microcontrôleurs, plusieurs fabricants de circuits intégrés ont amélioré la fonctionnalité du bus. L'interface de communication isolée isoSPI LTC6820 d'Analog Devices constitue un bon exemple. Le circuit intégré fournit un isolement galvanique entre les deux dispositifs SPI communiquant via une seule connexion à paire torsadée à l'aide d'une signalisation différentielle (Figure 7). Ce mode de signalisation étend la portée utile de l'interface SPI du LTC6820 jusqu'à 100 mètres (m), quoique à une fréquence d'horloge réduite par rapport à la fréquence nominale de 1 Mbps sur une distance de 10 m.

Figure 7 : Deux isolateurs LTC6820 fournissent un isolement galvanique entre deux dispositifs SPI. Le circuit intégré prend en charge des transferts de données jusqu'à 1 Mbps à des distances de 10 m et à des fréquences d'horloge inférieures pour une distance jusqu'à 100 m. (Source de l'image : Analog Devices)

Les transformateurs d'impulsions fournissent l'isolement. Il s'agit d'une technique souvent utilisée dans les applications industrielles de mise en réseau et dans la lecture de capteurs distants.

Conclusion

L'interface SPI résout le besoin d'une interface simple, peu coûteuse et à faible surcharge dans les applications où la source peut être assimilée à un flux de données, par opposition à la lecture et à l'écriture des données pour adresser les emplacements. C'est pourquoi elle est idéale pour gérer les communications dispositif-à-dispositif entre microcontrôleurs et capteurs, numériseurs, dispositifs de traitement numérique des signaux, et d'autres processeurs.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.