Utiliser des FPGA pour créer des applications Edge AI écoénergétiques hautes performances

Avec la contribution de Rédacteurs nord-américains de DigiKey

2021-01-12

Les concepteurs cherchant à mettre en œuvre des algorithmes d'intelligence artificielle (IA) sur des processeurs d'inférence en périphérie réseau sont soumis à une pression constante pour réduire la consommation d'énergie et le temps de développement, même si les demandes de traitement augmentent. Les réseaux de portes programmables (FPGA) offrent une combinaison particulièrement efficace de vitesse et de rendement énergétique pour l'implémentation des moteurs d'inférence de réseaux neuronaux (NN) requis pour l'Edge AI. Cependant, pour les développeurs avec peu d'expertise en FPGA, les méthodes de développement FPGA conventionnelles peuvent sembler complexes, ce qui les conduit souvent à se tourner vers des solutions moins optimales.

Cet article décrit une approche plus simple de Microchip Technology qui permet aux développeurs de contourner le développement FPGA traditionnel pour créer des réseaux neuronaux entraînés à l'aide de FPGA et d'un kit de développement logiciel (SDK), ou d'utiliser un kit vidéo basé sur FPGA pour passer immédiatement au développement d'applications de vision embarquée intelligentes.

Pourquoi utiliser l'Edge AI

L'edge computing apporte un certain nombre d'avantages aux applications Internet des objets (IoT) dans des segments aussi divers que l'automatisation industrielle, les systèmes de sécurité, les maisons intelligentes, et plus. Dans une application Internet industriel des objets (IIoT) ciblant une usine, l'edge computing peut améliorer considérablement le temps de réponse dans les boucles de contrôle des processus en éliminant les délais de propagation aller-retour vers les applications basées sur le cloud. De même, un système de sécurité en périphérie ou un verrou de porte de maison intelligente peuvent continuer à fonctionner même si la connexion au cloud est perdue accidentellement ou intentionnellement. Dans de nombreux cas, l'utilisation de l'edge computing dans l'une de ces applications peut contribuer à réduire le coût d'exploitation global en diminuant la dépendance du produit aux ressources cloud. Plutôt que de devoir faire face à un besoin inattendu de ressources supplémentaires coûteuses dans le cloud à mesure que la demande pour leurs produits augmente, les développeurs peuvent compter sur les capacités de traitement local intégrées à leurs produits pour les aider à maintenir des dépenses de fonctionnement plus stables.

L'acceptation rapide et la demande accrue en matière de modèles d'inférence pour l'apprentissage automatique (ou Machine Learning, ML) amplifient considérablement l'importance de l'edge computing. Pour les développeurs, le traitement local des modèles d'inférence permet de réduire la latence des réponses et les coûts des ressources cloud nécessaires à l'inférence basée cloud. Pour les utilisateurs, l'utilisation de modèles d'inférence locaux renforce la confiance dans le fait que leurs produits continueront à fonctionner malgré la perte occasionnelle de la connectivité Internet ou les changements dans les offres basées cloud du fournisseur de produits. De plus, les préoccupations en matière de sécurité et de confidentialité peuvent accroître la nécessité d'un traitement et d'une inférence au niveau local pour limiter la quantité d'informations sensibles transférées dans le cloud via l'Internet public.

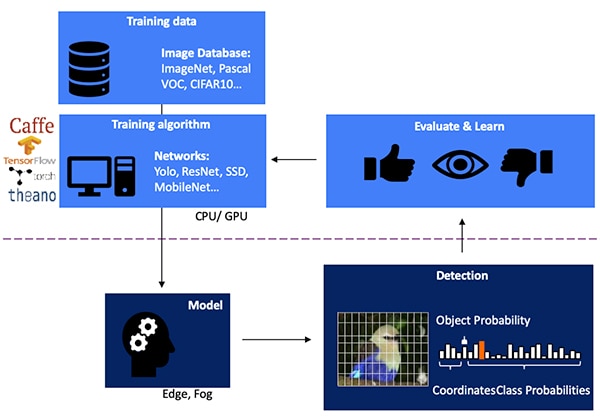

Le développement d'un modèle d'inférence NN pour la détection d'objets basée sur la vision est un processus en plusieurs étapes qui commence par l'entraînement du modèle, généralement effectué sur une structure ML telle que TensorFlow en utilisant des images étiquetées personnalisées ou publiques. En raison des exigences de traitement, l'entraînement des modèles est généralement effectué avec des processeurs graphiques (GPU) dans le cloud ou sur une autre plateforme de calcul hautes performances. Une fois l'entraînement terminé, le modèle est converti en un modèle d'inférence qui peut être exécuté sur des ressources edge computing ou fog computing et renvoyer les résultats d'inférence sous forme d'un ensemble de probabilités de classe d'objets (Figure 1).

Figure 1 : La mise en œuvre d'un modèle d'inférence pour l'Edge AI intervient à la fin d'un processus à plusieurs étapes nécessitant l'entraînement et l'optimisation des réseaux neuronaux sur des structures à l'aide de données d'entraînement disponibles ou personnalisées. (Source de l'image : Microchip Technology)

Figure 1 : La mise en œuvre d'un modèle d'inférence pour l'Edge AI intervient à la fin d'un processus à plusieurs étapes nécessitant l'entraînement et l'optimisation des réseaux neuronaux sur des structures à l'aide de données d'entraînement disponibles ou personnalisées. (Source de l'image : Microchip Technology)

Pourquoi les modèles d'inférence sont difficiles en termes de calcul

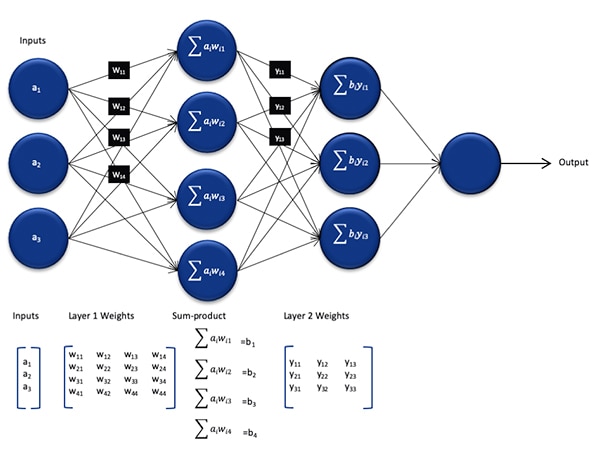

Bien qu'il soit réduit en termes de taille et de complexité par rapport au modèle utilisé pendant le processus d'entraînement, un modèle d'inférence NN constitue toujours un défi informatique pour les processeurs à usage général en raison du grand nombre de calculs qu'il requiert. Dans sa forme générique, un modèle NN profond comprend plusieurs couches d'ensembles de neurones. Dans chaque couche d'un réseau entièrement connecté, chaque neurone nij doit calculer la somme des produits de chaque entrée avec un poids wij associé (Figure 2).

Figure 2 : Le nombre de calculs requis pour l'inférence avec un réseau neuronal peut imposer une charge de travail de calcul importante. (Source de l'image : Microchip Technology)

Figure 2 : Le nombre de calculs requis pour l'inférence avec un réseau neuronal peut imposer une charge de travail de calcul importante. (Source de l'image : Microchip Technology)

La Figure 2 ne montre pas l'exigence de calcul supplémentaire imposée par la fonction d'activation qui modifie la sortie de chaque neurone en mappant les valeurs négatives sur zéro, les valeurs supérieures à 1 sur 1 et des fonctions similaires. La sortie de la fonction d'activation pour chaque neurone nij sert d'entrée à la couche suivante i+1, et ainsi de suite pour chaque couche. Enfin, la couche de sortie du modèle NN produit un vecteur de sortie représentant la probabilité que le vecteur d'entrée original (ou matrice) corresponde à l'une des classes (ou étiquettes) utilisées pendant le processus d'apprentissage supervisé.

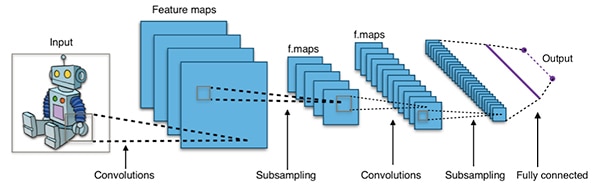

Les modèles NN efficaces sont construits avec des architectures qui sont beaucoup plus grandes et plus complexes que l'architecture NN générique représentative illustrée ci-dessus. Par exemple, un réseau neuronal convolutif (CNN) typique utilisé pour la détection d'objets images applique ces principes de manière fragmentaire, en balayant la largeur, la hauteur et la profondeur de couleur d'une image d'entrée pour produire une série de cartes de caractéristiques qui donnent finalement le vecteur de prédiction de sortie (Figure 3).

Figure 3 : Les CNN utilisés pour la détection d'objets images impliquent un grand nombre de neurones dans de nombreuses couches, ce qui impose une plus grande demande à la plateforme de calcul. (Source de l'image : Aphex34 CC BY-SA 4.0)

Figure 3 : Les CNN utilisés pour la détection d'objets images impliquent un grand nombre de neurones dans de nombreuses couches, ce qui impose une plus grande demande à la plateforme de calcul. (Source de l'image : Aphex34 CC BY-SA 4.0)

Utiliser des FPGA pour accélérer les mathématiques NN

Bien qu'un certain nombre d'options continuent d'émerger pour l'exécution de modèles d'inférence en périphérie, peu d'alternatives offrent le mélange optimal de flexibilité, de performances et de rendement énergétique requis pour l'inférence haute vitesse pratique en périphérie. Parmi les alternatives facilement disponibles pour l'Edge AI, les FPGA sont particulièrement efficaces car ils peuvent fournir une exécution matérielle hautes performances pour les opérations de calcul intensif tout en consommant relativement peu d'énergie.

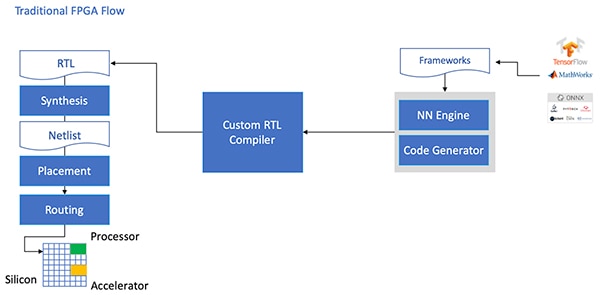

Malgré leurs avantages, les FPGA sont parfois délaissés en raison d'un flux de développement traditionnel qui peut être intimidant pour les développeurs sans grande expérience avec les FPGA. Pour créer une implémentation FPGA efficace d'un modèle NN généré par une structure NN, le développeur doit comprendre les nuances de la conversion du modèle en langage RTL, de la synthèse de la conception et du travail vers l'étape finale de conception physique pour produire une implémentation optimisée (Figure 4).

Figure 4 : Pour mettre en œuvre un modèle NN sur un FPGA, les développeurs devaient jusqu'à présent comprendre comment convertir leurs modèles en langage RTL et avancer dans le flux FPGA traditionnel. (Source de l'image : Microchip Technology)

Figure 4 : Pour mettre en œuvre un modèle NN sur un FPGA, les développeurs devaient jusqu'à présent comprendre comment convertir leurs modèles en langage RTL et avancer dans le flux FPGA traditionnel. (Source de l'image : Microchip Technology)

Avec ses FPGA PolarFire, ses logiciels spécialisés et la propriété intellectuelle (IP) associée, Microchip Technology fournit une solution qui rend l'inférence basse consommation et hautes performances en périphérie largement disponible pour les développeurs sans expérience FPGA.

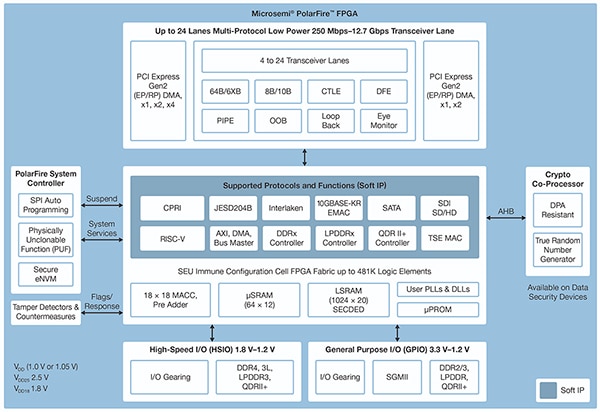

Fabriqués selon un procédé technologique non volatil avancé, les FPGA PolarFire sont conçus pour maximiser la flexibilité et les performances tout en minimisant la consommation d'énergie. Outre un large éventail d'interfaces haute vitesse pour les communications et les entrées/sorties (E/S), ils sont dotés d'une structure FPGA profonde capable de prendre en charge des fonctionnalités avancées à l'aide de cœurs IP logiciels, y compris des processeurs RISC-V, des contrôleurs de mémoire avancés et d'autres sous-systèmes d'interface standard (Figure 5).

Figure 5 : L'architecture PolarFire de Microchip Technology fournit une structure profonde conçue pour prendre en charge les exigences de conception hautes performances, y compris l'implémentation de modèles d'inférence à calcul intensif. (Source de l'image : Microchip Technology)

Figure 5 : L'architecture PolarFire de Microchip Technology fournit une structure profonde conçue pour prendre en charge les exigences de conception hautes performances, y compris l'implémentation de modèles d'inférence à calcul intensif. (Source de l'image : Microchip Technology)

La structure FPGA PolarFire fournit un ensemble complet d'éléments logiques et de blocs spécialisés, pris en charge dans une gamme de capacités par différents membres de la famille FPGA PolarFire, notamment les séries MPF100T, MPF200T, MPF300T et MPF500T (Tableau 1).

|

Tableau 1 : De nombreuses capacités et fonctionnalités de structure FPGA sont disponibles dans la série PolarFire. (Source du tableau : DigiKey, d'après la fiche technique PolarFire de Microchip Technology)

Parmi les caractéristiques particulièrement intéressantes pour l'accélération d'inférence, l'architecture PolarFire inclut un bloc mathématique dédié qui fournit une fonction MAC (multiplication-accumulation) signée de 18 bits × 18 bits avec un pré-additionneur. Un mode de produit scalaire intégré utilise un seul bloc mathématique pour effectuer deux opérations de multiplication 8 bits, fournissant un mécanisme pour augmenter la capacité en tirant parti de l'impact négligeable de la quantification du modèle sur la précision.

En plus d'accélérer les opérations mathématiques, l'architecture PolarFire contribue à réduire le type de surcharge mémoire qui se produit lors de la mise en œuvre de modèles d'inférence sur des architectures à usage général, comme les petites mémoires distribuées pour le stockage des résultats intermédiaires générés lors de l'exécution d'algorithmes NN. De plus, les poids et les valeurs de biais d'un modèle NN peuvent être stockés dans une mémoire morte (ROM) de 16 bits par 18 bits, construite à partir d'éléments logiques situés à proximité du bloc mathématique.

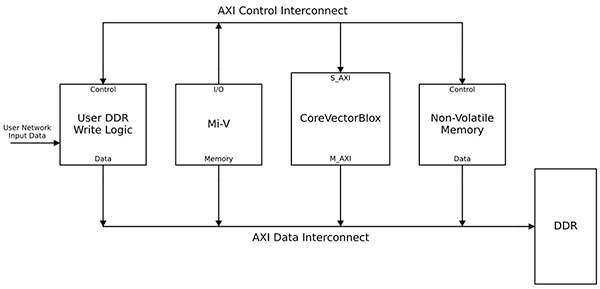

Combinés à d'autres fonctionnalités de la structure FPGA PolarFire, les blocs mathématiques constituent la base de l'IP CoreVectorBlox de niveau supérieur de Microchip Technology. Il s'agit d'un moteur NN flexible capable d'exécuter différents types de réseaux neuronaux. Outre un ensemble de registres de contrôle, l'IP CoreVectorBlox inclut trois blocs fonctionnels majeurs :

- Microcontrôleur : un simple processeur logiciel RISC-V qui lit le grand objet binaire (BLOB) du micrologiciel de Microchip et le fichier BLOB NN spécifique de l'utilisateur à partir d'un stockage externe. Il contrôle l'ensemble des opérations CoreVectorBlox en exécutant les instructions du micrologiciel BLOB.

- Processeur matriciel (MXP) : processeur logiciel comprenant huit unités arithmétiques logiques (ALU) de 32 bits, et conçu pour effectuer des opérations parallèles sur des vecteurs de données en utilisant des opérations de tenseur par élément, y compris add, sub, xor, shift, mul, dotprod, et plus, en utilisant une précision mixte de 8 bits, 16 bits et 32 bits, selon les besoins.

- Accélérateur CNN : accélère les opérations MXP en utilisant un réseau bidimensionnel de fonctions MAC implémentées à l'aide de blocs mathématiques et fonctionnant avec une précision de 8 bits.

Un système de traitement NN complet combine un bloc IP CoreVectorBlox, de la mémoire, un contrôleur de mémoire et un processeur hôte, tel que le cœur de processeur logiciel Microsoft RISC-V (Mi-V) (Figure 6).

Figure 6 : Le bloc IP CoreVectorBlox fonctionne avec un processeur hôte tel que le microcontrôleur RISC-V Mi-V de Microchip pour mettre en œuvre un modèle d'inférence NN. (Source de l'image : Microchip Technology)

Figure 6 : Le bloc IP CoreVectorBlox fonctionne avec un processeur hôte tel que le microcontrôleur RISC-V Mi-V de Microchip pour mettre en œuvre un modèle d'inférence NN. (Source de l'image : Microchip Technology)

Dans une implémentation de système vidéo, le processeur hôte charge le micrologiciel et les BLOB réseau à partir de la mémoire Flash du système, et les copie dans la mémoire vive (RAM) à double débit de données (DDR) pour une utilisation avec le bloc CoreVectorBlox. À l'arrivée des images vidéo, le processeur hôte les écrit dans la mémoire RAM DDR et signale au bloc CoreVectorBlox de commencer le traitement de l'image. Après avoir exécuté le modèle d'inférence défini dans le BLOB réseau, le bloc CoreVectorBlox réécrit les résultats, y compris la classification d'images, dans la RAM DDR pour une utilisation par l'application cible.

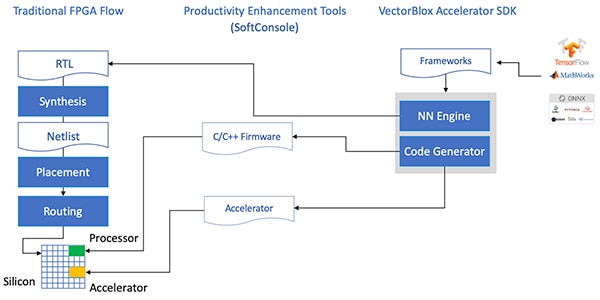

Le flux de développement simplifie l'implémentation FPGA NN

Microchip protège les développeurs de la complexité d'implémentation d'un modèle d'inférence NN sur les FPGA PolarFire. Au lieu de traiter les détails du flux FPGA traditionnel, les développeurs de modèles NN travaillent normalement avec leurs structures NN et chargent le modèle résultant dans le kit de développement logiciel (SDK) VectorBlox Accelerator de Microchip Technology. Le SDK génère le jeu de fichiers requis, y compris les fichiers nécessaires au flux de développement FPGA normal et les fichiers BLOB micrologiciels et réseau mentionnés précédemment (Figure 7).

Figure 7 : Le SDK VectorBlox Accelerator gère les détails d'implémentation d'un modèle NN sur un FPGA, en générant automatiquement les fichiers nécessaires à la conception et à l'exécution du modèle d'inférence basé FPGA. (Source de l'image : Microchip Technology)

Figure 7 : Le SDK VectorBlox Accelerator gère les détails d'implémentation d'un modèle NN sur un FPGA, en générant automatiquement les fichiers nécessaires à la conception et à l'exécution du modèle d'inférence basé FPGA. (Source de l'image : Microchip Technology)

Comme le flux du SDK VectorBlox Accelerator superpose la conception NN au moteur NN implémenté dans le FPGA, différents réseaux neuronaux peuvent fonctionner sur la même conception FPGA sans qu'il ne soit nécessaire de refaire le flux de synthèse de conception FPGA. Les développeurs créent du code C/C++ pour le système résultant et peuvent changer de modèle au sein du système à la volée, ou exécuter des modèles simultanément en utilisant le découpage temporel.

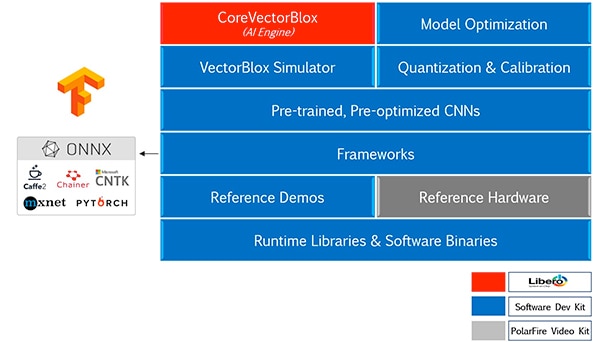

Le SDK VectorBlox Accelerator associe la suite de conception FPGA Libero de Microchip Technology à un ensemble complet de capacités pour le développement de modèles d'inférence NN. En plus des services d'optimisation, de quantification et d'étalonnage des modèles, le SDK fournit un simulateur NN qui permet aux développeurs d'utiliser les mêmes fichiers BLOB pour évaluer leur modèle avant leur utilisation dans l'implémentation matérielle FPGA (Figure 8).

Figure 8 : Le SDK VectorBlox Accelerator fournit un ensemble complet de services conçus pour optimiser l'implémentation FPGA des modèles d'inférence générés par la structure. (Source de l'image : Microchip Technology)

Figure 8 : Le SDK VectorBlox Accelerator fournit un ensemble complet de services conçus pour optimiser l'implémentation FPGA des modèles d'inférence générés par la structure. (Source de l'image : Microchip Technology)

Le SDK VectorBlox Accelerator prend en charge les modèles au format ONNX (Open Neural Network Exchange) ainsi que les modèles de plusieurs structures, notamment TensorFlow, Caffe, Chainer, PyTorch et MXNET. Les architectures CNN prises en charge incluent MNIST, les versions MobileNet, ResNet-50, Tiny Yolo V2 et Tiny Yolo V3. Microchip s'efforce d'étendre la prise en charge pour inclure la plupart des réseaux dans l'open model zoo OpenVINO Toolkit open-source de modèles pré-entraînés, notamment Yolo V3, Yolo V4, RetinaNet et SSD-MobileNet.

Le kit vidéo démontre l'inférence FPGA

Pour aider les développeurs à passer rapidement au développement d'applications de vision embarquée intelligentes, Microchip Technology fournit une application d'exemple complète, conçue pour fonctionner sur la conception de référence et le kit vidéo et d'imagerie FPGA PolarFire MPF300-VIDEO-KIT de la société.

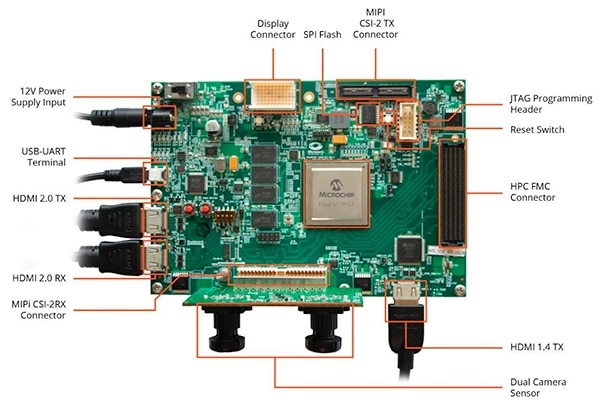

Basée sur le FPGA PolarFire MPF300T de Microchip, la carte du kit combine un capteur de caméra double, une mémoire RAM DDR4, une mémoire Flash, une gestion de l'alimentation et une variété d'interfaces (Figure 9).

Figure 9 : Le kit vidéo et d'imagerie FPGA PolarFire MPF300-VIDEO-KIT et les logiciels associés permettent aux développeurs de démarrer rapidement l'inférence basée FPGA dans les applications de vision embarquée intelligentes. (Source de l'image : Microchip Technology)

Figure 9 : Le kit vidéo et d'imagerie FPGA PolarFire MPF300-VIDEO-KIT et les logiciels associés permettent aux développeurs de démarrer rapidement l'inférence basée FPGA dans les applications de vision embarquée intelligentes. (Source de l'image : Microchip Technology)

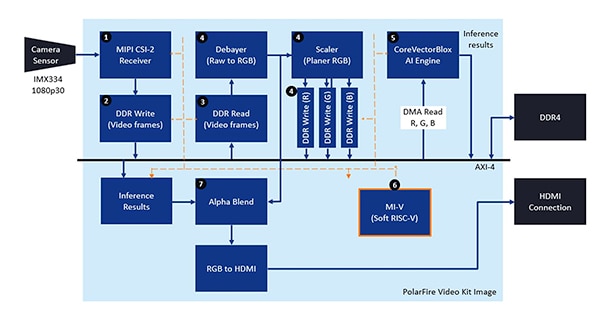

Le kit est fourni avec un projet de conception Libero complet, utilisé pour générer les fichiers BLOB micrologiciels et réseau. Après avoir programmé les fichiers BLOB dans la mémoire Flash embarquée, les développeurs cliquent sur le bouton d'exécution dans Libero pour démarrer la démonstration, qui traite les images vidéo du capteur de caméra et affiche les résultats de l'inférence sur un écran (Figure 10).

Figure 10 : Le kit vidéo et d'imagerie FPGA PolarFire de Microchip Technology montre comment concevoir et utiliser l'implémentation FPGA d'un système de vision embarquée intelligent architecturé autour du moteur NN CoreVectorBlox de Microchip. (Source de l'image : Microchip Technology)

Figure 10 : Le kit vidéo et d'imagerie FPGA PolarFire de Microchip Technology montre comment concevoir et utiliser l'implémentation FPGA d'un système de vision embarquée intelligent architecturé autour du moteur NN CoreVectorBlox de Microchip. (Source de l'image : Microchip Technology)

Pour chaque image vidéo d'entrée, le système basé sur FPGA exécute les étapes suivantes (avec les numéros d'étape en corrélation avec la Figure 10) :

- Chargement d'une image de la caméra

- Stockage de l'image en mémoire RAM

- Lecture de l'image depuis la mémoire RAM

- Conversion de l'image brute en RVB, nivelage RVB et stockage du résultat en mémoire RAM

- Le processeur logiciel RISC-V Mi-V démarre le moteur CoreVectorBlox, qui récupère l'image dans la RAM, effectue les inférences et stocke les résultats de la probabilité de classification dans la mémoire RAM

- Le Mi-V utilise les résultats pour créer une image de superposition avec des rectangles de délimitation, des résultats de classification et d'autres métadonnées, et stocke l'image dans la mémoire RAM

- L'image originale est fusionnée avec l'image de superposition et écrite sur l'écran HDMI

La démonstration prend en charge l'accélération des modèles Tiny Yolo V3 et MobileNet V2, mais les développeurs peuvent exécuter d'autres modèles pris en charge par le SDK en utilisant les méthodes décrites plus haut, en apportant une petite modification au code pour ajouter le nom du modèle et les métadonnées à la liste existante contenant les deux modèles par défaut.

Conclusion

Les algorithmes d'IA tels que les modèles NN imposent généralement des charges de travail à calcul intensif qui exigent des ressources de calcul plus robustes que celles disponibles avec les processeurs à usage général. Si les FPGA sont bien équipés pour répondre aux exigences de performances et de basse consommation pour l'exécution de modèles d'inférence, les méthodes de développement FPGA conventionnelles peuvent sembler complexes, ce qui pousse souvent les développeurs à se tourner vers des solutions moins optimales.

Comme illustré, grâce à l'IP et aux logiciels spécialisés de Microchip Technology, les développeurs sans expertise FPGA peuvent mettre en œuvre des conceptions basées sur l'inférence, mieux à même de répondre aux exigences de performances, de puissance et de planification de conception.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.