Utiliser des microcontrôleurs Flashless pour réduire les coûts et augmenter les performances des systèmes

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-08-22

Les réseaux Internet des objets (IoT) étant sollicités pour effectuer des tâches plus complexes, les besoins en mémoire des points d'extrémité IoT ont augmenté, en particulier pour les points d'extrémité qui effectuent désormais des niveaux de calcul plus élevés en périphérie. Cependant, la mémoire Flash intégrée à un microcontrôleur est limitée à environ 1 Mbit et de nombreux points d'extrémité IoT haut de gamme nécessitent beaucoup plus de mémoire.

La solution classique consiste à étendre la mémoire programme du microcontrôleur avec une puce Flash externe. Toutefois, lorsque les besoins en mémoire atteignent 8 Mbits ou plus, la majeure partie de la mémoire programme est hors puce.

Par conséquent, les concepteurs préfèrent souvent se passer de mémoire Flash intégrée et utiliser plutôt un microcontrôleur sans mémoire Flash (Flashless), également appelé ROMless, associé à une puce Flash XiP (exécution sur place) SPI octale externe et haute vitesse. Cela réduit considérablement le coût du microcontrôleur et offre une conception à l'épreuve du temps en permettant une plus grande évolutivité. L'émergence d'interfaces mémoire octales très haute vitesse permet de dissiper les inquiétudes concernant les temps d'accès à la mémoire.

Cet article traite des microcontrôleurs ROMless et des mémoires externes, ainsi que de leur évolution en une option viable pour les points d'extrémité IoT et les systèmes embarqués nécessitant d'importantes quantités de mémoire programme. Il explique ensuite comment appliquer ce concept à l'aide de microcontrôleurs ROMless de NXP Semiconductors et d'une puce Flash XiP SPI octale d'Adesto Technologies.

Extension de mémoire en périphérie IoT

La plupart des points d'extrémité IoT basses à moyennes performances utilisent un microcontrôleur pour gérer le point d'extrémité, stockant le micrologiciel dans la mémoire Flash intégrée. Le micrologiciel s'étend à mesure qu'il ajoute du code d'application, des piles de communication IP sans fil et du code de sécurité amélioré. Une extension de code peut se produire lors du développement et à la suite de mises à jour sur le terrain.

Certains de ces points d'extrémité IoT sont maintenant appelés à exécuter davantage de fonctions de calcul. Au lieu de transmettre des données de capteur brutes ou partiellement traitées via le réseau à un ordinateur central pour qu'il les traite, ces points d'extrémité IoT effectuent des tâches plus complexes pouvant inclure des algorithmes de fusion de capteurs, une interpolation de données, une reconnaissance des formes ou des images et des calculs de plus en plus complexes faisant appel à l'intelligence artificielle (IA).

L'ordinateur central ne reçoit donc que le résultat du traitement local du nœud IoT au lieu de chaque octet de données brutes des capteurs, ce qui peut réduire le trafic sur le réseau sans fil. Étant donné que l'émetteur RF peut représenter la consommation d'énergie la plus significative d'un point d'extrémité IoT, l'edge computing (informatique en périphérie) améliore souvent la durée de vie de la batterie pour les points d'extrémité alimentés par batterie.

Les systèmes qui nécessitent des mises à jour sur le terrain sont confrontés à d'autres défis liés à la mémoire. Les systèmes classiques nécessitent au moins deux fois l'espace de mémoire programme estimé pour pouvoir gérer ces mises à jour. Cela permet de gérer à la fois la mémoire programme existante et la taille de toutes les mises à jour sans fil (OTA). Certains systèmes peuvent nécessiter trois fois plus d'espace de mémoire programme que l'espace estimé, la mémoire supplémentaire étant allouée à une image du micrologiciel d'usine en lecture seule. Lorsque certains types de défaillances du système se produisent, notamment la détection d'un piratage ou d'une image de micrologiciel corrompue, le système peut charger l'image du micrologiciel d'usine d'origine pour récupérer le système.

Pour certaines applications, cette extension de mémoire peut rapidement dépasser la limite de 1 Mbit de la mémoire Flash intégrée, ce qui nécessite une extension de mémoire externe. Depuis toujours, la solution consiste à ajouter une puce de mémoire Flash parallèle externe. Cependant, cela présente l'inconvénient d'utiliser environ 36 broches externes au niveau du microcontrôleur, qui pourraient autrement servir pour les E/S de l'application. Cela gaspille également de l'espace sur la carte à circuit imprimé et augmente la probabilité d'interférences électromagnétiques (EMI) provenant de la carte.

Extension de mémoire programme SPI

Outre l'utilisation d'un bus parallèle, il est également possible d'étendre la mémoire programme à l'aide de l'interface SPI (Serial Peripheral Interface). Bien que l'interface SPI traditionnelle utilise une seule ligne de données pour les transmissions à un seul bit en semi-duplex, elle a évolué au fil des années et prend désormais en charge les lignes de données doubles et quadruples, ce qui a entraîné une augmentation correspondante du débit de données. Ce débit a atteint un niveau qui permet de créer une interface avec une puce Flash SPI externe de grande capacité.

Pour les applications de mémoire programme, une interface SPI double ou quadruple traditionnelle utilise une configuration Flash fantôme dans laquelle la mémoire de données Flash externe est copiée dans une mémoire vive statique (SRAM) intégrée, mappée avec un espace mémoire programmable. Bien que cette configuration présente l'avantage de pouvoir facilement étendre la mémoire programme tout en améliorant la vitesse d'exécution en réduisant la mémoire SRAM rapide, elle présente également de gros inconvénients. Étant donné que la quantité de mémoire SRAM interne est limitée, la mémoire est accessible en mode pagination : la mémoire Flash est transformée en mémoire SRAM interne en fonction des besoins. Il est possible de rendre les choses plus faciles en augmentant la mémoire SRAM intégrée, mais comme il s'agit de l'un des modules les plus coûteux de tous les semi-conducteurs, cela a pour inconvénient d'augmenter considérablement le coût du microcontrôleur.

La méthode XiP est une évolution plus récente de l'interface SPI. Elle permet au processeur du microcontrôleur d'exécuter le code micrologiciel directement à partir de la mémoire Flash SPI externe. Il est possible d'améliorer considérablement la vitesse d'exécution du programme en ajoutant un cache à l'interface XiP SPI.

La popularité XiP SPI a entraîné l'extension récente de l'interface, qui prend maintenant en charge huit lignes de données. Cette interface XiP SPI octale a augmenté le débit à un point tel qu'il est beaucoup plus élevé que la mémoire Flash intégrée — plus de 100 Mbits/s.

Révolution de la mémoire SPI

Cela a conduit à une curieuse évolution qui nous ramène 30 ans en arrière. Prenons un système intégrant 1 Mbit de mémoire Flash et 32 Mbits de mémoire programme Flash externe accessible via une interface XiP SPI octale. La mémoire programme intégrée est si minime que la question qui se pose est de savoir si l'on peut supprimer cette mémoire Flash intégrée au microcontrôleur tout en conservant un système rentable.

On a longtemps supposé qu'un système milieu de gamme doté d'un microcontrôleur à mémoire Flash était toujours plus rentable qu'un système doté d'un microcontrôleur sans mémoire Flash avec une puce Flash externe. Ce n'est que récemment que les choses ont changé.

Si la mémoire Flash intégrée est retirée, cela réduit bien entendu le coût du microcontrôleur. Toutefois, un examen plus approfondi montre que si la mémoire Flash n'est plus nécessaire, les fonctionnalités liées à technologie de traitement utilisées uniquement pour la mémoire Flash peuvent également être éliminées. Cela réduit le coût du processus de fabrication, entraînant ainsi une réduction considérable du coût du microcontrôleur. Cela a entraîné une réapparition de ce que l'on appelait le microcontrôleur « ROMless » il y a une trentaine d'années. Aujourd'hui, nous l'appelons Flashless.

(Re)découvrez les microcontrôleurs Flashless

Le MIMXRT1052DVL6B (RT1052) de NXP Semiconductors est un microcontrôleur Flashless hautes performances pouvant tirer parti de la vitesse de la mémoire Flash. Le RT1052 fait partie de la gamme de processeurs i.MX RT1050 de NXP et est basé sur un processeur Arm® Cortex®-M7 de 600 mégahertz (MHz) avec un cache d'instructions de 32 Ko et un cache de données de 32 Ko. La fréquence d'horloge de 600 MHz est obtenue en retirant la mémoire Flash et en utilisant une technologie de fabrication CMOS haute vitesse qui n'est pas limitée par la mémoire Flash interne. Le RT1052 possède une grande quantité de mémoire SRAM (512 Ko) pouvant être partitionnée pour une utilisation en tant que mémoire programme ou mémoire de données.

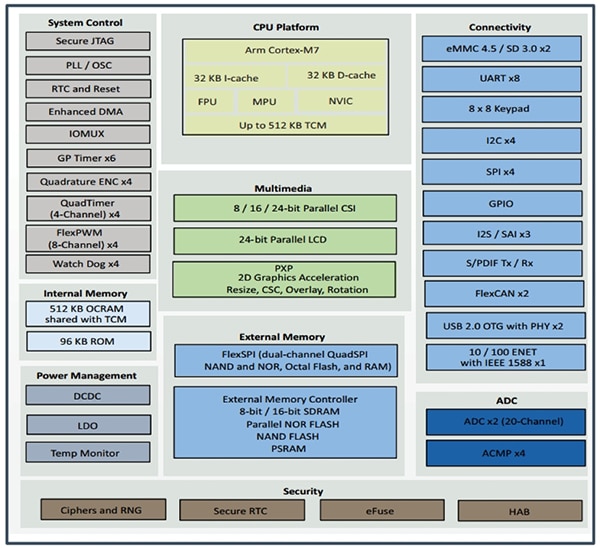

Le microcontrôleur inclut une variété de périphériques haut de gamme, notamment une interface LCD, une interface de capteur de caméra numérique (CSI) et un moteur PXP (Pixel Processing Pipeline) pour la prise en charge des caméras haut de gamme, une interface SPDIF pour l'audio numérique, deux interfaces USB OTG, deux interfaces de cartes Flash eMMC/SD, deux convertisseurs analogique-numérique (CAN) à 20 canaux et un module de cryptage. Une liste complète des périphériques est disponible dans le schéma fonctionnel (Figure 1).

Figure 1 : Le RT1052 de NXP offre une grande variété de périphériques haut de gamme, notamment une interface série XiP SPI et une prise en charge du cryptage des données. (Source de l'image : NXP)

Figure 1 : Le RT1052 de NXP offre une grande variété de périphériques haut de gamme, notamment une interface série XiP SPI et une prise en charge du cryptage des données. (Source de l'image : NXP)

Le MIMXRT1051DVL6B (RT1051) de NXP constitue une autre option. Il présente les mêmes fonctionnalités que le RT1052, à l'exception des caractéristiques LCD, CSI et PXP.

Le RT1052 possède une interface FlexSPI, capable d'exécuter du code à l'aide d'interfaces Flash XiP SPI doubles, quadruples ou octales. Pour renforcer la sécurité du micrologiciel, le microcontrôleur prend en charge la mémoire programme cryptée via l'interface XiP SPI, comme l'ATXP032-CCUE-T d'Adesto Technologies.

Fonctionnement d'une mémoire Flash XiP moderne

L'ATXP032-CCUE-T d'Adesto est une puce Flash octale de 32 Mbits qui prend en charge les transferts de données jusqu'à 266 Mo par seconde en mode DTR (débit de transfert double) octal, ce qui est bien plus rapide qu'une mémoire Flash intégrée au microcontrôleur. Elle requiert une alimentation simple de 1,8 V et présente un courant de veille en mode octal typique de 35 microampères (µA). Elle prendre en charge une horloge SPI de 133 MHz maximum.

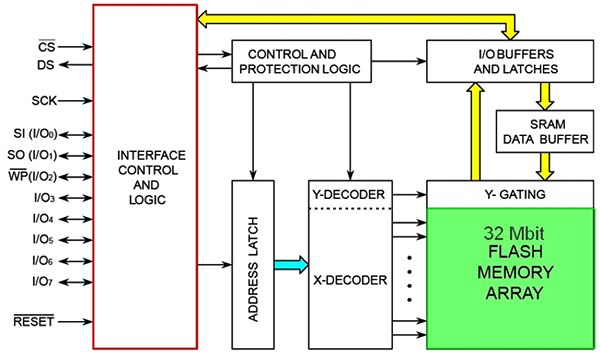

Figure 2 : La mémoire Flash ATXP032-CCUE-T d'Adesto utilise une interface SPI octale, I/O0 à I/O7, pour créer une interface vers un microcontrôleur. Un tampon de données d'écriture SRAM améliore les performances des opérations d'écriture dans la mémoire Flash. (Source de l'image : Adesto Technologies)

Figure 2 : La mémoire Flash ATXP032-CCUE-T d'Adesto utilise une interface SPI octale, I/O0 à I/O7, pour créer une interface vers un microcontrôleur. Un tampon de données d'écriture SRAM améliore les performances des opérations d'écriture dans la mémoire Flash. (Source de l'image : Adesto Technologies)

Lors d'une lecture Flash active, la consommation de courant de l'ATXP32 est de 142 µA/MHz, plus une surcharge de 1 mA (typique). À sa fréquence d'horloge SPI maximale de 133 MHz en mode octal, le système ne consomme que 19,9 mA.

L'ATXP032-CCUE-T prend également en charge les modes SPI 0 et 3 standard, ainsi que le mode SPI quadruple. Un registre de sécurité de 256 octets possède un identifiant unique programmé en usine de 128 octets, ainsi que 128 octets de mémoire programmable une seule fois (OTP) pouvant être utilisés pour stocker des informations sur le dispositif, comme une adresse MAC Ethernet ou une clé de sécurité.

La configuration de la mémoire de l'ATXP032-CCUE-T est remarquable. Elle est partitionnée en quatre rangées de 8 Mbits chacune. La logique interne est configurée de sorte qu'un microcontrôleur hôte peut exécuter le code d'une rangée tout en programmant ou en effaçant celui d'une autre ligne. Le fonctionnement est transparent pour le microcontrôleur hôte et ne nécessite aucun paramètre de configuration particulier.

L'ATXP032-CCUE-T dispose également de trois registres d'état et de contrôle permettant de configurer les paramètres de fonctionnement du dispositif, comme le mode basse consommation, l'activation ou la désactivation du mode DTR et le paramétrage des modes SPI standard, quadruple ou octal (le mode par défaut étant le mode SPI standard). La lecture à partir des registres d'état peut indiquer l'état d'un programme ou une opération d'effacement, l'état basse consommation et si une partie de la mémoire est protégée en écriture.

Association de microcontrôleurs Flashless et de XiP externe

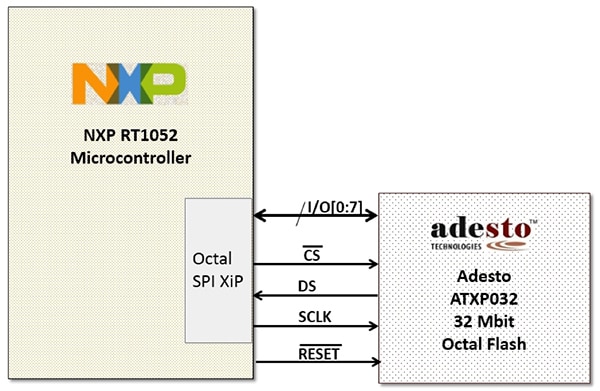

L'assemblage du RT1052 et de l'ATXP032-CCUE-T est simple (Figure 3). À la mise sous tension, le RT1052 commence à exécuter le code grâce aux 96 Ko de la mémoire ROM intégrée dédiée au démarrage. Cette mémoire ROM dédiée au démarrage lit l'état des 14 broches de configuration du mode de démarrage qui sélectionnent l'une des nombreuses interfaces de mémoire externe du RT1052 à utiliser en tant que mémoire programme. Les options incluent une carte eMMC externe, une carte micro SD, une interface parallèle externe traditionnelle ou l'interface XiP SPI (dans cet exemple, l'ATXP032-CCUE-T d'Adesto).

Figure 3 : Le microcontrôleur RT1052 Flashless de NXP possède une interface XiP SPI octale qui peut facilement communiquer avec l'ATXP032-CCUE-T d'Adesto. Le fonctionnement de l'interface XiP SPI octale est transparent pour le cœur Arm. (Source de l'image : DigiKey Electronics)

Figure 3 : Le microcontrôleur RT1052 Flashless de NXP possède une interface XiP SPI octale qui peut facilement communiquer avec l'ATXP032-CCUE-T d'Adesto. Le fonctionnement de l'interface XiP SPI octale est transparent pour le cœur Arm. (Source de l'image : DigiKey Electronics)

Les options de démarrage du RT1052 incluent également le téléchargement du code à partir d'USB OTG ou d'un UART à exécuter depuis la mémoire SRAM. Les options du mode de démarrage peuvent également être définies lors de la fabrication dans le RT1052 au lieu d'utiliser les broches de configuration du mode de démarrage. Une fois que l'interface XiP SPI octale est activée pour l'exécution de la mémoire programme par la mémoire ROM de démarrage du RT1052, l'exécution du programme est immédiate. Le cœur Arm exécute ensuite le micrologiciel à partir de l'ATXP032-CCUE-T d'Adesto de la même manière que depuis un dispositif Flash externe parallèle ou une mémoire Flash interne.

En raison des transferts de données haut débit concernés, la mémoire Flash série octale doit être installée sur le circuit imprimé le plus près possible du port XiP SPI octal du microcontrôleur. Pour réduire les interférences, aucune des pistes du circuit imprimé ne doit dépasser 120 millimètres (mm). Le signal d'horloge doit se situer à une distance correspondant à au moins trois fois la largeur des pistes du circuit imprimé par rapport aux autres signaux pour éviter les interférences. Les signaux de données bidirectionnels I/O [0:7] doivent tous se situer à moins de 10 mm les uns des autres pour éviter tout décalage.

Conclusion

Les points d'extrémité IoT ont des besoins en mémoire croissants en raison de la transition vers l'edge computing, de la nécessité d'effectuer des mises à jour sans fil et des besoins associés en matière d'évolutivité de la mémoire. À un moment donné, les concepteurs de ces dispositifs d'extrémité peuvent juger utile d'utiliser un microcontrôleur Flashless.

Comme indiqué ici, les améliorations apportées aux microcontrôleurs Flashless, aux interfaces haut débit et aux puces Flash XiP SPI octales offrent aux développeurs la possibilité de créer des systèmes embarqués ou des points d'extrémité IoT rentables et hautes performances au lieu d'utiliser des approches avec microcontrôleur Flash traditionnel.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.