Utiliser une mémoire ferroélectrique pour améliorer la fiabilité des applications automobiles

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-06-28

La mémoire non volatile (NVM) joue un rôle essentiel dans presque toutes les conceptions de systèmes embarqués. De nombreuses conceptions présentent des exigences de plus en plus strictes liées à la mémoire non volatile, notamment en termes de vitesse d'accès et d'écriture des données, de conservation des données et de basse consommation. Cette tendance s'accentue dans les applications automobiles, pour lesquelles les concepteurs cherchent à intégrer davantage de fonctionnalités toujours plus poussées, comme les systèmes d'aide à la conduite (ADAS) qui sont indispensables.

Afin de garantir un fonctionnement sûr et fiable de ces systèmes, les concepteurs doivent étudier de plus près la mémoire vive ferroélectrique (F-RAM) en tant qu'option NVM de grade automobile fiable, basse consommation et plus rapide que les solutions NVM actuelles.

Cet article traite des caractéristiques clés de la technologie F-RAM et décrit la manière dont les développeurs peuvent utiliser deux solutions F-RAM de Cypress Semiconductor pour améliorer la fiabilité des systèmes d'aide à la conduite et utiliser ces systèmes pour implémenter la mémoire F-RAM dans d'autres applications vitales.

Exigences NVM dans le secteur automobile

Les applications de sécurité automobile illustrent parfaitement la tendance du secteur à l'intégration de capteurs plus avancés présentant une résolution et un taux de rafraîchissement plus élevés. Les sous-systèmes automobiles comme les systèmes d'aide à la conduite, les calculateurs (ECU) et les enregistreurs de données d'événements (EDR) continuent d'évoluer, en s'appuyant sur de nombreuses données approfondies recueillies par un large éventail de capteurs. Une éventuelle perte de données, ou même un accès lent aux données, peut compromettre la sécurité du système, du véhicule et de ses passagers.

Dans les conceptions ADAS, par exemple, le temps nécessaire pour écrire dans une mémoire EEPROM peut entraîner un décalage potentiellement désastreux dans les manœuvres automatiques conçues pour éviter les risques détectés. Dans les conceptions EDR, des performances d'écriture lentes peuvent entraîner, en cas de panne d'alimentation lors d'un accident de la circulation, la perte de données de capteur essentielles, supprimant ainsi très probablement les données nécessaires à la compréhension de l'origine de l'accident.

Caractéristiques NVM de la technologie F-RAM

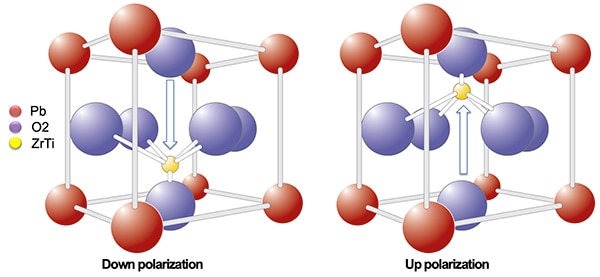

Les dispositifs de mémoire qui intègrent la technologie F-RAM offrent une alternative NVM efficace pouvant répondre à la demande croissante et aux exigences de performances liées au stockage fiable des données et à l'accès haute vitesse. Les dispositifs sont fabriqués en titano-zirconate de plomb (Pb[ZrxTi1−x]O3), également appelé plus simplement « PZT ». Le PZT possède la caractéristique unique de permettre à la lacune métallique (cation) intégrée au quartz PZT d'atteindre l'un des deux états possibles de polarisation, haut ou bas, selon le sens du champ électrique appliqué (Figure 1).

Figure 1 : La technologie F-RAM exploite deux états énergétiques de même stabilité manifestés par des matériaux PZT soumis à un champ électrique. (Source de l'image : Cypress Semiconductor)

Figure 1 : La technologie F-RAM exploite deux états énergétiques de même stabilité manifestés par des matériaux PZT soumis à un champ électrique. (Source de l'image : Cypress Semiconductor)

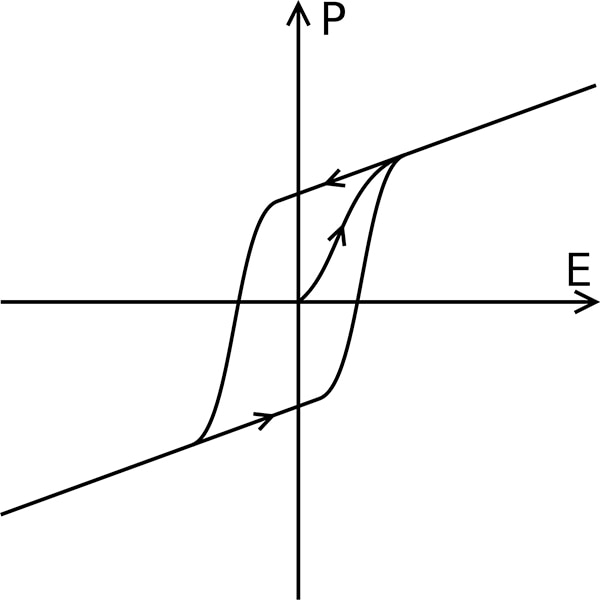

Ces deux états basse consommation étant identiques, le cation reste dans son état de polarisation le plus récent lorsque le champ électrique est supprimé (Figure 2). Lors de l'application d'un champ électrique positif ou négatif, le cation passe, une fois de plus, rapidement à l'état de polarisation approprié en suivant une boucle d'hystérésis caractéristique, semblable à celle présente dans les matériaux ferromagnétiques.

Figure 2 : Les matériaux PZT suivent une boucle d'hystérésis caractéristique lorsqu'ils basculent entre deux états de polarisation stables suite à l'application d'un champ électrique. (Source de l'image : WikiMedia Commons/CC-BY-SA-3.0)

Figure 2 : Les matériaux PZT suivent une boucle d'hystérésis caractéristique lorsqu'ils basculent entre deux états de polarisation stables suite à l'application d'un champ électrique. (Source de l'image : WikiMedia Commons/CC-BY-SA-3.0)

Les caractéristiques de la technologie F-RAM se traduisent directement en divers avantages pour les dispositifs NVM fabriqués avec cette technologie. Étant donné que les deux états énergétiques du PZT ont la même stabilité, le cation reste à sa dernière position pendant des dizaines d'années voire des siècles, ce qui entraîne des taux de conservation des données hors pair dans les dispositifs NVM qui exploitent la technologie F-RAM et sont basés sur le PZT. En outre, comme cette technologie est basée sur la position du cation plutôt que sur les mécanismes de stockage de la charge d'autres technologies NVM, les dispositifs F-RAM sont intrinsèquement tolérants aux radiations et résistants aux perturbations isolées provenant du rayonnement ionisant.

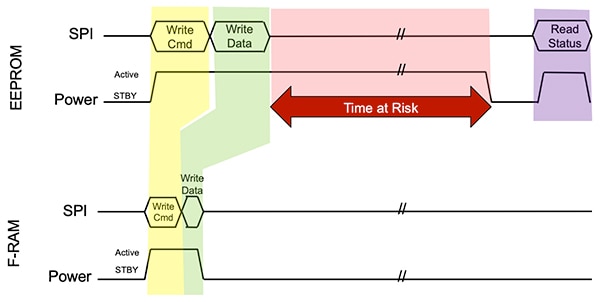

Au-delà de ses avantages pour le stockage à long terme, la technologie F-RAM améliore les performances dynamiques des dispositifs NVM. La transition d'état est très rapide et ne requiert que peu d'énergie, remédiant ainsi à une limite fondamentale associée à l'utilisation d'une mémoire EEPROM ou Flash dans les applications critiques. Les dispositifs EEPROM et Flash nécessitent un « temps d'immersion » important associé à la mise en tampon des données durant leurs cycles d'écriture relativement lents. Ce délai supplémentaire dans le cycle d'écriture entraîne une période pendant laquelle les données peuvent être menacées et complètement perdues si l'alimentation électrique est coupée avant que l'opération ne soit terminée avec la vérification finale de l'état de lecture (Figure 3).

Figure 3 : La nécessité d'un temps d'immersion étendu (en rouge) lors des opérations d'écriture EEPROM ou Flash se traduit par une longue période durant laquelle les données sont exposées à des risques par rapport aux dispositifs F-RAM. (Source de l'image : Cypress Semiconductor)

Figure 3 : La nécessité d'un temps d'immersion étendu (en rouge) lors des opérations d'écriture EEPROM ou Flash se traduit par une longue période durant laquelle les données sont exposées à des risques par rapport aux dispositifs F-RAM. (Source de l'image : Cypress Semiconductor)

Pour tenir compte des cycles d'écriture plus lents dans une mémoire EEPROM ou Flash, les développeurs espérant atténuer les effets des pannes d'alimentation ont ajouté de grands condensateurs ou des batteries, ainsi que des régulateurs de tension appropriés, afin de maintenir la tension d'alimentation NVM suffisamment longtemps pour terminer les opérations d'écriture. À l'inverse, les dispositifs F-RAM comme les dispositifs Excelon-Auto de Cypress Semiconductor fonctionnent à la vitesse du bus durant les opérations d'écriture, réduisant ainsi grandement la perte de données essentielles et éliminant la nécessité de sources d’alimentation supplémentaires dans la conception.

Dispositifs F-RAM de grade automobile

Similaire aux mémoires EEPROM et Flash série sur le plan fonctionnel, les dispositifs F-RAM Excelon™-Auto sont conçus pour répondre aux exigences des applications critiques en matière de mémoire non volatile fiable et hautes performances. Les concepteurs de systèmes automobiles peuvent utiliser ces dispositifs qualifiés AEC-Q100 pour remplacer d'autres types de mémoire, en choisissant le CY15V102QN pour les alimentations de 1,71 V à 1,89 V ou le CY15B102QN pour les alimentations de 1,8 V à 3,6 V. Les deux modèles sont des dispositifs de 2 mégabits (Mbit), organisés logiquement sous la forme 256 kbits x 8.

Dans leur plage de températures de fonctionnement de -40°C à +125°C, les dispositifs F-RAM Excelon disposent d'un taux de conservation des données nettement supérieur à celui proposé par d'autres technologies NVM. Par exemple, le CY15x102QN peut conserver des données pendant 121 ans (durée estimée) tout en fonctionnant à 85°C. Étant donné que la conservation des données est inversement proportionnelle à la température, s'ils sont contraints de fonctionner aux températures typiques plus élevées d'un moteur (à 95°C par exemple), les dispositifs F-RAM présentent un taux de conservation des données estimé à 35 ans.

En matière de fiabilité, les dispositifs F-RAM présentent une endurance de cycles de lecture/écriture de 1013, soit sept ordres de grandeur de plus qu'une mémoire EEPROM ou Flash typique. Ainsi, les développeurs qui utilisent des dispositifs F-RAM n'ont pas besoin d'implémenter des techniques comme la répartition de l'usure, qui distribue les écritures entre les secteurs afin de tenir compte des cycles d'écriture limités associés à d'autres technologies NVM.

Une conception simplifiée grâce à la technologie F-RAM

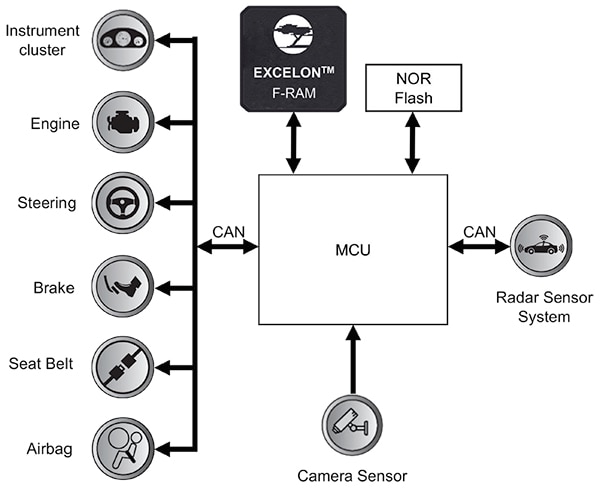

Dans une conception typique, les développeurs peuvent utiliser ces dispositifs pour remplacer directement ou compléter d'autres types de dispositifs NVM, tels qu'une mémoire Flash NOR. Dans une conception ADAS, par exemple, les développeurs peuvent associer une mémoire Flash NOR, utilisée pour stocker le micrologiciel, à un dispositif F-RAM Excelon capable de gérer en toute fiabilité plusieurs flux de données provenant de divers sous-systèmes automobiles qui fournissent des données aux applications ADAS (Figure 4).

Figure 4 : Les développeurs ADAS pour le secteur automobile peuvent associer des dispositifs F-RAM Excelon, destinés au stockage des données critiques, à des dispositifs Flash NOR généralement utilisés pour stocker les micrologiciels ou des données de configuration dans des conceptions basées sur microcontrôleurs (MCU). (Source de l'image : Cypress Semiconductor)

Figure 4 : Les développeurs ADAS pour le secteur automobile peuvent associer des dispositifs F-RAM Excelon, destinés au stockage des données critiques, à des dispositifs Flash NOR généralement utilisés pour stocker les micrologiciels ou des données de configuration dans des conceptions basées sur microcontrôleurs (MCU). (Source de l'image : Cypress Semiconductor)

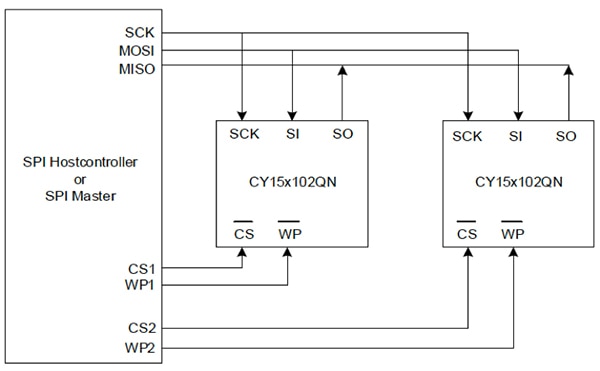

Les développeurs peuvent facilement intégrer des dispositifs F-RAM Excelon à une conception en les connectant simplement au bus SPI du processeur hôte. Conçu pour fonctionner en tant que dispositif SPI secondaire, le dispositif F-RAM CY15x102QN peut prendre en charge des fréquences d'horloge SPI jusqu'à 50 mégahertz (MHz). Dans une configuration matérielle typique, les développeurs connectent respectivement les bornes SI (entrée série) et SO (sortie série) du dispositif F-RAM aux lignes MOSI (sortie maître, entrée esclave) et MISO (entrée maître, sortie esclave) du dispositif SPI principal. Les connexions aux lignes SCK (horloge série) et /CS (sélection de puce) respectives finalisent l'interface matérielle. Les développeurs peuvent combiner plusieurs dispositifs de manière à ce qu'ils partagent le bus SPI de l'hôte (Figure 5).

Figure 5 : Les développeurs peuvent utiliser un bus SPI partagé pour se connecter à un processeur hôte à l'aide d'un ou de plusieurs dispositifs F-RAM CY15x102QN. (Source de l'image : Cypress Semiconductor)

Figure 5 : Les développeurs peuvent utiliser un bus SPI partagé pour se connecter à un processeur hôte à l'aide d'un ou de plusieurs dispositifs F-RAM CY15x102QN. (Source de l'image : Cypress Semiconductor)

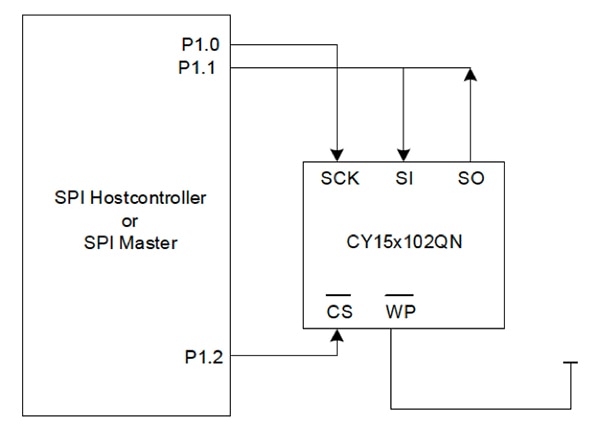

Pour les microcontrôleurs ne disposant pas de capacités SPI, les dispositifs CY15x102QN prennent en charge une alternative simple permettant d'émuler l'interface matérielle SPI à l'aide des E/S à usage général (GPIO) du microcontrôleur afin de se connecter au dispositif F-RAM. Les développeurs peuvent implémenter cette interface à l'aide de seulement trois GPIO en utilisant la même broche pour les lignes de données SI et SO du dispositif F-RAM (Figure 6).

Figure 6 : Pour un microcontrôleur ne disposant pas de capacités SPI natives, les développeurs peuvent simplement utiliser les E/S à usage général du microcontrôleur pour émuler le protocole SPI afin d'accéder à un dispositif F-RAM série CY15x102QN. (Source de l'image : Cypress Semiconductor)

Figure 6 : Pour un microcontrôleur ne disposant pas de capacités SPI natives, les développeurs peuvent simplement utiliser les E/S à usage général du microcontrôleur pour émuler le protocole SPI afin d'accéder à un dispositif F-RAM série CY15x102QN. (Source de l'image : Cypress Semiconductor)

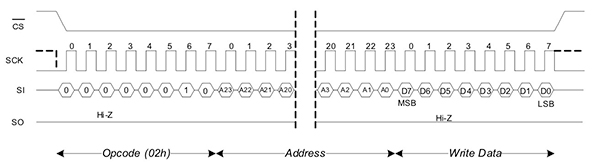

Dans le protocole SPI standard, un dispositif principal initie une transaction en abaissant la broche /CS. Lorsque /CS passe à l'état bas, le dispositif F-RAM interprète l'octet suivant en tant que code opération. Par exemple, une opération d'écriture suit le code opération d'écriture standard (02h) SPI avec l'adresse à trois octets et les octets de données (Figure 7).

Figure 7 : Les dispositifs F-RAM CY15x102QN de Cypress prennent en charge les codes opération et protocoles SPI standard, permettant ainsi aux développeurs d'effectuer facilement des écritures à retard nul en envoyant le code opération d'écriture (02h), l'adresse et les données dans l'ordre. (Source de l'image : Cypress Semiconductor)

Figure 7 : Les dispositifs F-RAM CY15x102QN de Cypress prennent en charge les codes opération et protocoles SPI standard, permettant ainsi aux développeurs d'effectuer facilement des écritures à retard nul en envoyant le code opération d'écriture (02h), l'adresse et les données dans l'ordre. (Source de l'image : Cypress Semiconductor)

Pour les dispositifs F-RAM CY15x102QN de 2 Mbits, l'adresse est une séquence de trois octets, dont les six bits supérieurs sont ignorés. Cypress recommande de définir ces six bits supérieurs sur zéro afin de favoriser une transition aisée vers des dispositifs F-RAM de capacités supérieures.

Une opération de lecture suit le même protocole. Après réception du code opération de lecture standard (03h) et de l'adresse, le dispositif F-RAM transmet successivement des octets de données à la broche SO, ce qui augmente automatiquement l'adresse mémoire tandis que /CS reste à l'état bas et que les signaux d'horloge continuent. Par conséquent, les développeurs peuvent réaliser une lecture en bloc simplement en laissant /CS à l'état bas et en continuant d'émettre des signaux d'horloge SCK jusqu'à ce que le nombre requis d'octets de données soit lu.

Les dispositifs F-RAM CY15x102QN prennent également en charge une fonction de lecture rapide compatible avec la mémoire Flash série. Après le code opération de lecture rapide (0Bh) et l'adresse, l'hôte SPI envoie un octet fictif afin d'émuler la latence de lecture Flash. Après réception de l'octet fictif, le dispositif F-RAM répond en envoyant les données demandées. Les opérations de lecture rapide peuvent également réaliser des lectures en bloc à l'aide du même mécanisme que les lectures standard.

Protection en écriture

En plus d'une logique de commande d'interface SPI, les dispositifs F-RAM CY15x102QN offrent des mécanismes supplémentaires afin d'identifier le dispositif et de protéger en écriture le réseau F-RAM.

Les développeurs peuvent émettre des codes opération afin d'accéder à un identifiant unique en lecture seule et à l'identifiant de dispositif du CY15x102QN qui fournissent tous deux des informations comme le fabricant, la densité de mémoire et la révision des composants. Les développeurs peuvent également établir un registre de numéro de série de lecture/écriture de 8 octets afin d'associer une mémoire F-RAM à un système ou une configuration spécifique.

Pour protéger la mémoire F-RAM, le dispositif fournit à la fois des mécanismes logiciels et matériels. Pour la protection des données durant la fabrication, un secteur spécial dédié de 256 octets est conçu pour conserver l'intégrité des données pendant un maximum de trois cycles standard de soudage par refusion. Pour la protection durant le fonctionnement normal, le dispositif utilise un verrouillage WEL (write-enable latch) afin de protéger le réseau F-RAM de toute écriture accidentelle. Au démarrage, le verrouillage WEL est désactivé par défaut, exigeant du développeur qu'il émette un code opération WREN (write-enable) (06h) avant de réaliser des opérations d'écriture.

Dans le registre d'état du dispositif, une paire de bits de protection du bloc (BP), BP0 et BP1, permet aux développeurs de protéger la mémoire sur la plage d'adresses complète (BP1=1, BP0=1), dans la moitié supérieure de la mémoire uniquement (BP1=1, BP0=0) ou dans le quart supérieur de la mémoire uniquement (BP1=0, BP0=1).

Les développeurs peuvent utiliser la broche de protection en écriture (/WP) du matériel afin d'éviter toute modification des bits BP par un logiciel durant le fonctionnement normal. Ici, les développeurs définissent le bit WPEN (Write Protect Enable) dans le registre d'état et placent la broche /WP à l'état bas afin de verrouiller le registre d'état.

Gestion de l'alimentation

Pendant le fonctionnement normal, le rendement énergétique inhérent à la technologie F-RAM entraîne généralement une consommation électrique du CY15V102QN (VDD de 1,71 V à 1,89 V) de seulement 5,0 milliampères (mA) pour un fonctionnement à la fréquence d'horloge maximale de 50 MHz. Les développeurs peuvent réduire la fréquence d'horloge pour économiser davantage d'énergie. La consommation électrique peut alors descendre à 0,4 mA à 1 MHz pour le CY15V102QN. La consommation électrique avec le CY15B102QN (VDD de 1,8 V à 3,6 V) n'est que légèrement plus élevée : 6,0 mA à 50 MHz et 0,5 mA à 1 MHz.

Pour les longues périodes d'inactivité, les développeurs peuvent réduire sensiblement la consommation en utilisant des codes opération SPI afin de définir les dispositifs CY15x102QN sur l'un des trois modes basse consommation suivants :

- Mode veille avec consommation électrique typique de 2,7 microampères (μA) pour le CY15V102QN ou 3,2 μA pour le CY15B102QN

- Mode veille profonde à 1,1 μA pour le CY15V102QN ou 1,3 μA pour le CY15B102QN

- Mode hibernation à 0,1 μA pour les deux modèles

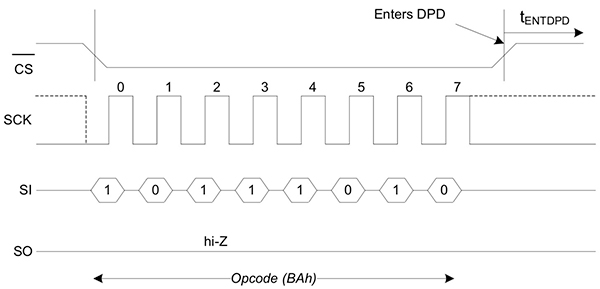

Les dispositifs CY15x102QN basculent automatiquement en mode veille lorsque l'hôte SPI définit /CS à l'état haut à la fin d'une séquence de codes opération. Pour faire basculer le dispositif en mode de veille profonde ou d'hibernation, l'hôte SPI utilise le protocole de code opération SPI. Plus spécifiquement, l'hôte SPI bascule vers l'un des deux modes à la plus basse consommation en commençant par définir /CS à l'état bas, puis en envoyant un code opération spécial correspondant à la veille profonde (BAh) ou à l'hibernation (B9h), avant de définir /CS à l'état haut (Figure 8).

Figure 8 : Les dispositifs F-RAM CY15x102QN basculent automatiquement en mode veille après une séquence de codes opération, mais les développeurs peuvent les placer dans un mode à la consommation encore plus basse, comme le mode de veille profonde (DPD), grâce à la procédure de code opération SPI normale. (Source de l'image : Cypress Semiconductor)

Figure 8 : Les dispositifs F-RAM CY15x102QN basculent automatiquement en mode veille après une séquence de codes opération, mais les développeurs peuvent les placer dans un mode à la consommation encore plus basse, comme le mode de veille profonde (DPD), grâce à la procédure de code opération SPI normale. (Source de l'image : Cypress Semiconductor)

Lorsque l'hôte SPI définit /CS à l'état haut après l'envoi du code opération de basse consommation approprié, le dispositif F-RAM CY15x102QN bascule sur le mode basse consommation demandé en environ 3 μs.

Depuis le mode veille, les dispositifs F-RAM de Cypress repassent immédiatement en mode actif lorsque /CS passe à l'état bas pour initialiser la séquence de codes opération suivante. Depuis le mode de veille profonde ou d'hibernation, les dispositifs F-RAM repassent également en mode actif lorsque /CS passe à l'état bas, mais après un petit décalage d'environ 10 μs pour le mode de veille profonde ou de 450 μs pour le mode d'hibernation.

Conclusion

La demande liée à la mémoire non volatile fiable, rapide, basse consommation et hautes performances a augmenté pour un large éventail d'applications qui dépendent des données provenant de capteurs toujours plus nombreux. Dans les domaines stratégiques comme les applications ADAS automobiles, la perte de données peut considérablement nuire aux mécanismes de sécurité conçus pour protéger le véhicule et ses occupants.

Grâce aux dispositifs F-RAM de Cypress Semiconductor, les développeurs peuvent facilement ajouter une mémoire non volatile capable de stocker de façon fiable des données essentielles pendant des dizaines d'années sans sacrifier les performances ni les exigences de basse consommation.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.