Utiliser un processeur multicœur efficace pour créer des produits à commande vocale plus intelligents

Avec la contribution de Rédacteurs nord-américains de DigiKey

2020-02-14

La demande en matière de produits plus intelligents est devenue omniprésente dans presque tous les domaines d'application, à mesure que les utilisateurs se familiarisent avec les assistants numériques virtuels comme Amazon Alexa, Assistant Google, Apple Siri et Microsoft Cortana, notamment, et leur font confiance. En plus d'offrir un côté pratique, ces assistants jouent un rôle grandissant dans l'amélioration de la sûreté et de la sécurité dans un large éventail de produits destinés aux systèmes industriels et aux applications de santé. Pour les développeurs, cependant, les conceptions sous-jacentes de ces produits entraînent parfois des demandes contradictoires pour des processeurs capables d'offrir des performances accrues, un coût et une empreinte optimisés et un fonctionnement efficace.

Cet article montre comment les développeurs peuvent utiliser un processeur multicœur — le processeur i.MX 8M Nano de NXP — pour répondre aux exigences très diverses de traitement et d'interface des produits intelligents émergents dans des segments d'application allant de la maison connectée et de l'automatisation industrielle aux systèmes médicaux. Cet article montre notamment comment les développeurs peuvent utiliser ce processeur pour mettre en œuvre plus facilement des solutions vocales nouvelle génération avec des capacités de traitement audio avancées.

Évolution des produits intelligents

L'essor rapide des technologies d'assistants vocaux a conduit les utilisateurs à rechercher davantage de fonctionnalités dans les produits intelligents. Les produits émergents doivent non seulement répondre aux commandes vocales, mais aussi embarquer davantage d'intelligence, en utilisant une plus grande variété de données d'entrée provenant de capteurs, de caméras et d'autres produits. Il ne suffit pas que les interrupteurs intelligents allument et éteignent les lumières ou que les lave-vaisselle fonctionnent en réponse à des commandes vocales. À mesure que les applications se perfectionnent, leurs dispositifs sous-jacents doivent prendre en charge des combinaisons de capteurs plus diversifiées, des capacités de traitement améliorées utilisant des méthodes d'intelligence artificielle (IA) et des affichages graphiques 3D.

Le besoin en matière de produits plus intelligents s'étend au-delà d'un désir de plus grande facilité. Dans des domaines d'application critiques tels que l'automatisation industrielle et les soins de santé, la capacité d'un dispositif à alerter de manière proactive les utilisateurs sur les dangers ou les conditions pathologiques peut s'avérer essentielle. Un ouvrier d'usine portant un casque de protection capable de surveiller l'environnement immédiat peut plus facilement éviter les dangers ; un patient à risque portant un minuscule moniteur de santé qui surveille en permanence les signes vitaux peut bénéficier de l'intervention nécessaire bien avant une crise.

Ces produits et d'autres produits intelligents imposent des exigences de conception spécifiques qui sont aussi variées que leurs applications cibles, mais la plupart partagent le besoin d'un traitement hautes performances, de capacités multimédias et d'un fonctionnement sécurisé. Pour les développeurs, ces exigences fonctionnelles se combinent avec le besoin fondamental de solutions capables d'évoluer pour servir des applications plus robustes, tout en offrant un format physique plus compact pour répondre aux attentes des utilisateurs en matière de réduction de la taille, des coûts et de la consommation d'énergie. Basée sur une architecture multicœur hétérogène, la gamme de processeurs d'applications i.MX 8M Nano de NXP répond aux exigences larges et diverses des conceptions de produits intelligents émergents.

Cœurs hautes performances

Le processeur i.MX 8M Nano de NXP est le tout dernier membre de la gamme de processeurs i.MX 8M de NXP, conçus pour fournir une plateforme de traitement multicœur évolutive. Pour les applications vidéo haut de gamme, les processeurs phares i.MX 8M de NXP tels que le MIMX8MQ5DVAJZAB offrent une résolution d'affichage allant jusqu'à 4K avec un décodage matériel de vidéo HDR (High Dynamic Range, grande gamme dynamique) 4K. Pour la vidéo 1080p, les processeurs i.MX 8M Mini de NXP tels que le MIMX8MM6CVTKZAA offrent une prise en charge du décodage matériel 1080p. Les séries i.MX 8M et 8M Mini combinent jusqu'à quatre cœurs de processeur d'application Arm® Cortex®-A53 avec un cœur de microcontrôleur Arm Cortex-M4F.

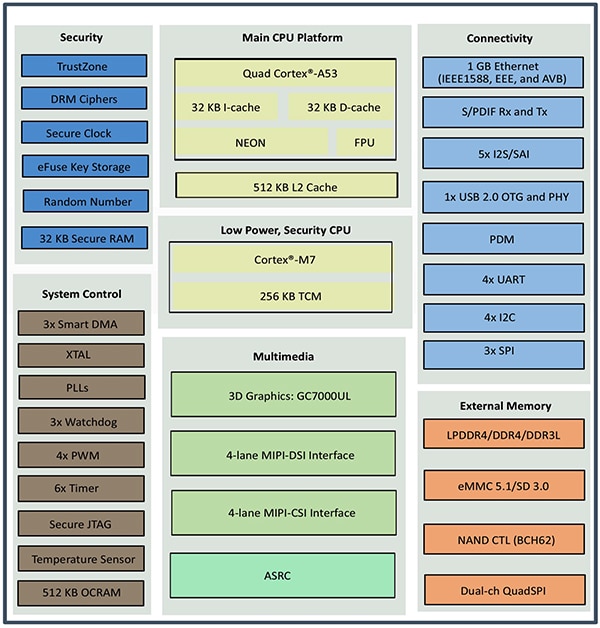

En revanche, le processeur i.MX 8M Nano MIMX8MN6CVTIZAA de NXP combine quatre cœurs Arm Cortex-A53 avec un cœur Arm Cortex-M7, offrant les meilleures performances parmi les autres cœurs de la série Arm Cortex-M, y compris le Cortex-M4F.

Outre leur complément de cœurs de processeur, les processeurs i.MX 8M Nano prennent en charge une grande variété de dispositifs de mémoire externes et fournissent une gamme complète d'interfaces périphériques externes typiquement requises dans les applications grand public et industrielles (Figure 1).

Figure 1 : Le processeur i.MX 8M Nano de NXP combine jusqu'à quatre processeurs d'application Arm Cortex-A53, un microcontrôleur Arm Cortex-M7, des sous-systèmes matériels spécialisés, et des interfaces périphériques externes complètes typiquement utilisées dans les applications grand public et industrielles. (Source de l'image : NXP)

Figure 1 : Le processeur i.MX 8M Nano de NXP combine jusqu'à quatre processeurs d'application Arm Cortex-A53, un microcontrôleur Arm Cortex-M7, des sous-systèmes matériels spécialisés, et des interfaces périphériques externes complètes typiquement utilisées dans les applications grand public et industrielles. (Source de l'image : NXP)

Les différentes variantes disponibles de la série de processeurs i.MX 8M Nano permettent aux développeurs de répondre facilement à leurs exigences spécifiques en matière de coût et de performances. Par exemple, les membres hautes performances intègrent un large éventail de sous-systèmes spécialisés pour la sécurité, les affichages graphiques 3D, le traitement audio, et plus. D'autres membres de la série i.MX 8M Nano offrent des options avec moins de cœurs Cortex-A53, et des versions simplifiées qui présentent des capacités graphiques réduites.

Tous les membres de la série de processeurs i.MX 8M Nano offrent néanmoins la possibilité de combiner les performances applicatives et les capacités en temps réel requises dans les produits intelligents émergents.

Conçu pour fournir une exécution hautes performances des logiciels d'application, chaque cœur de processeur d'application Arm Cortex-A53 peut fonctionner à des fréquences d'horloge jusqu'à 1,5 gigahertz (GHz) tout en travaillant à partir d'un cache d'instructions (cache I) de 32 kilo-octets (Ko) de niveau 1 (L1) dédié, d'un cache de données (cache D) de 32 Ko et d'un cache unifié L2 partagé de 512 Ko. Avec leur unité en virgule flottante (FPU) intégrée, ces cœurs prennent en charge la technologie Arm Neon pour les opérations SIMD (instruction unique, données multiples) avancées, utilisées dans le traitement des signaux numériques et d'autres algorithmes avancés dans les applications à données intensives.

Pour les besoins des systèmes embarqués, le cœur du microcontrôleur Arm Cortex-M7 fonctionne à des fréquences jusqu'à 750 mégahertz (MHz) tout en assurant une exécution hautes performances des processus en temps réel qui nécessitent une faible latence et un fonctionnement déterministe. Pour accélérer encore le traitement, le cœur comprend une unité en virgule flottante intégrée et 256 Ko de mémoire à couplage étroit (TCM) utilisée pour les instructions et le cache de données.

Cependant, pour les tâches complexes de traitement en temps réel, la capacité à reconnaître rapidement les sources d'interruption séparées peut être aussi critique que la puissance de traitement brute. Dans les processeurs i.MX 8M Nano, un contrôleur d'interruption global (GIC) intégré dans chaque cœur Arm Cortex-A53 et un contrôleur d'interruption vectoriel imbriqué (NVIC) dans le cœur Arm Cortex-M7 permettent la gestion fine des interruptions de presque 128 sources de demande d'interruption distinctes correspondant à des états du cœur, des temporisateurs, des événements d'interface périphérique, des opérations d'accès direct à la mémoire (DMA), des processus matériels spécialisés, et plus.

Traitement multicœur hétérogène

Séparément, chaque cœur de processeur i.MX 8M Nano fournit une ressource de calcul robuste. Utilisés ensemble, les multiples cœurs de processeur offrent une plateforme de calcul puissante, capable de gérer les exigences contradictoires à la fois pour les performances en temps réel et l'exécution des logiciels d'application pouvant perturber la conception de produits intelligents. Un produit intelligent basé sur ce processeur peut par exemple utiliser le cœur Cortex-M7 pour traiter les flux audio en temps réel, tout en utilisant des algorithmes s'exécutant sur un ou plusieurs cœurs Cortex-A53 pour analyser les données résultantes et fournir aux utilisateurs un affichage graphique 3D des résultats.

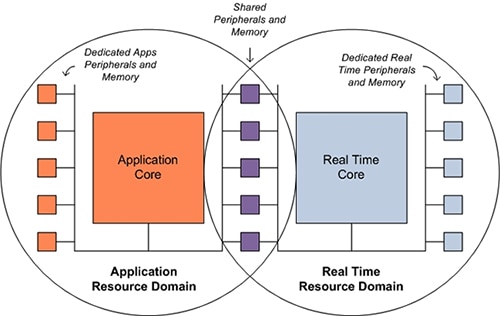

Cependant, pour effectuer de manière fiable ce type de traitement multicœur hétérogène coordonné, un système multicœur requiert l'orchestration minutieuse des opérations de traitement et l'échange de données entre les différents cœurs, les blocs matériels spécialisés et les périphériques. Dans le processeur i.MX 8M Nano, cette orchestration est intégrée dans les mécanismes matériels pour les sémaphores et la messagerie généralement utilisés par les services logiciels de bas niveau dans des environnements multiprocesseurs.

Dans les systèmes embarqués, cette exécution orchestrée s'étend également aux ressources matérielles telles que la mémoire et les périphériques. Pour cette tâche, le processeur intègre un contrôleur de domaine de ressources (RDC) dédié, conçu pour garantir un partage sûr des ressources, le cas échéant, ou une isolation fiable si nécessaire. Ainsi, les logiciels d'application et le code en temps réel peuvent chacun contrôler les ressources dédiées à leur domaine tout en partageant un ensemble de ressources communes (Figure 2).

Figure 2 : Les mécanismes matériels du processeur i.MX 8M Nano de NXP garantissent l'isolation des ressources dédiées au domaine d'application Cortex-A53 ou au domaine en temps réel Cortex-M7, tout en permettant un partage sûr des ressources si nécessaire. (Source de l'image : NXP)

Figure 2 : Les mécanismes matériels du processeur i.MX 8M Nano de NXP garantissent l'isolation des ressources dédiées au domaine d'application Cortex-A53 ou au domaine en temps réel Cortex-M7, tout en permettant un partage sûr des ressources si nécessaire. (Source de l'image : NXP)

Support spécialisé pour les produits intelligents

En utilisant uniquement les multiples cœurs du processeur i.MX 8M Nano et les capacités de partage des ressources, les développeurs peuvent créer des applications sophistiquées pour les produits intelligents émergents construits avec des assistants vocaux et des graphiques 3D. Ces applications gagnent encore en performances tout en réduisant leur empreinte logicielle grâce à un support matériel spécialisé pour les produits intelligents, intégré dans les processeurs i.MX 8M Nano.

Pour les graphiques, le processeur graphique (GPU) intégré du processeur fournit une accélération graphique 2D et 3D, et prend en charge les bibliothèques graphiques standard, notamment Vulkan, Open Computing Language (OpenCL) et Open Graphics Library (OpenGL). Un contrôleur d'interface d'affichage à cristaux liquides (LCDIF) intégré prend en charge les affichages à 1080p60.

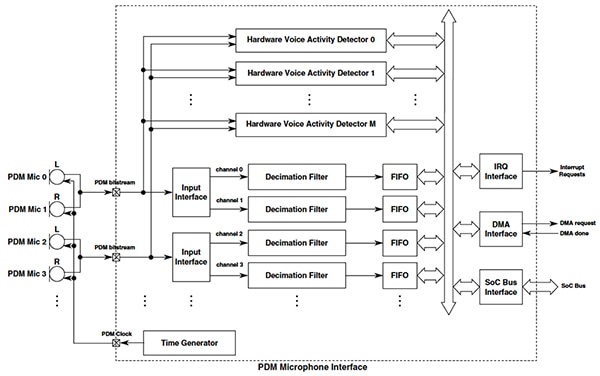

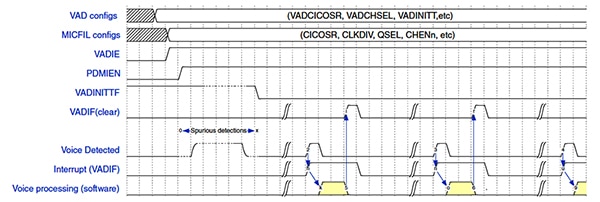

Alors que le processeur graphique intégré décharge le traitement de l'affichage des cœurs, un autre ensemble de sous-systèmes matériels décharge une variété de tâches de traitement audio qui ralentissent généralement les systèmes basés sur des processeurs classiques. Pour le traitement des entrées de microphone, l'interface de microphone à modulation d'impulsion-densité (PDM) (MICFIL) du processeur fournit un pipeline à plusieurs étages conçu pour générer des données PCM 16 bits filtrées à partir de l'entrée 1 bit reçue des microphones PDM (Figure 3).

Figure 3 : Le sous-système d'interface du processeur i.MX 8M Nano de NXP pour entrée de microphone PDM combine des pipelines matériels séparés pour le traitement du signal audio et la détection d'activité vocale. (Source de l'image : NXP)

Figure 3 : Le sous-système d'interface du processeur i.MX 8M Nano de NXP pour entrée de microphone PDM combine des pipelines matériels séparés pour le traitement du signal audio et la détection d'activité vocale. (Source de l'image : NXP)

Pour une application vocale typique, les concepteurs doivent juste connecter un microphone PDM à l'un des huit canaux PDM pris en charge par le processeur. Dans le sous-système d'interface de microphone PDM, une interface d'entrée combine les données PDM multiplexées dans le temps provenant d'une paire de microphones pour former une voie comprenant des canaux gauche et droit.

À l'étape suivante pour chaque canal, un filtre de décimation programmable dédié fournit différentes bandes passantes en fonction du débit de sortie souhaité et l'un des six paramètres de sélection de la qualité (QSEL), y compris des niveaux haut, moyen et bas, ainsi que trois niveaux de très faible qualité supplémentaires. Par exemple, à un taux de sortie de 48 kilohertz (kHz), les modes de très faible qualité fixent la bande passante du filtre de 10,5 Hz à 11,25 kHz, par rapport à une bande passante de 21 Hz à 22,5 kHz pour les modes de haute, moyenne et basse qualité. Enfin, les résultats de chaque canal sont mis à disposition dans des tampons séparés de type premier entré, premier sorti (FIFO) pour chaque canal afin de générer des interruptions, un transfert par DMA ou un accès au bus.

Détection de l'activité vocale basée sur le matériel

Parallèlement à ce pipeline de mise en forme des signaux audio, l'interface de microphone PDM fournit un ensemble de détecteurs matériels d'activité vocale (HWVAD) qui surveillent les canaux d'entrée des microphones souhaités. (Remarque : la Figure ci-dessus suggère que chaque détecteur HWVAD est associé à une voie, mais la documentation indique des voies, et le nom d'un registre, VADCHSEL, le confirme). Pour prendre en charge le fonctionnement du détecteur HWVAD, le processeur fournit un riche ensemble de registres de périphériques qui permet aux développeurs de définir la configuration HWVAD spécifique requise pour leur application (Tableau 1).

|

Tableau 1 : Registres du processeur i.MX 8M Nano de NXP typiquement utilisés pour configurer les détecteurs d'activité vocale matériels intégrés dans l'interface de microphone PDM (MICFIL) du processeur. (Source du tableau : DigiKey, d'après des données de NXP)

Sur la base de ces paramètres de registre, le détecteur HWVAD utilise des algorithmes de détection vocale intégrés pour identifier l'activité vocale. Lors de la détection, le détecteur HWVAD génère une interruption pour activer un cœur, généralement le Cortex-M7, pour un traitement supplémentaire (Figure 4).

Figure 4 : En utilisant les paramètres de configuration programmés par le développeur, les détecteurs matériels d'activité vocale du processeur i.MX 8M Nano de NXP permettent aux cœurs de processeur de se mettre en veille ou d'effectuer d'autres traitements jusqu'à ce qu'une voix soit détectée et qu'un traitement vocal supplémentaire soit requis. (Source de l'image : NXP)

Figure 4 : En utilisant les paramètres de configuration programmés par le développeur, les détecteurs matériels d'activité vocale du processeur i.MX 8M Nano de NXP permettent aux cœurs de processeur de se mettre en veille ou d'effectuer d'autres traitements jusqu'à ce qu'une voix soit détectée et qu'un traitement vocal supplémentaire soit requis. (Source de l'image : NXP)

Dans une application d'assistant vocal, le cœur vérifie le flux audio pour trouver le mot d'activation approprié. Si le mot d'activation est détecté, le cœur fournit le flux audio aux services d'assistant vocal basés cloud pris en charge par l'application.

Outre le sous-système d'interface de microphone PDM, le processeur i.MX 8M Nano fournit également cinq modules d'interface audio synchrone (SAI) qui prennent en charge un certain nombre de formats audio standard, y compris Inter-IC Sound (I2S), audio codec 97 (AC97), audio TDM et Direct Stream Digital (DSD), ainsi que les données de codec ou DSP.

Pour répondre aux besoins spécifiques de leurs applications, les développeurs doivent souvent convertir des échantillons d'entrée audio à une autre fréquence d'échantillonnage et une autre résolution. Plutôt que d'utiliser des cycles de processeur pour accomplir cette tâche courante, le processeur i.MX 8M Nano intègre un sous-système de convertisseur de fréquence d'échantillonnage asynchrone (ASRC) dédié.

Capable de traiter simultanément jusqu'à 32 canaux audio, l'ASRC convertit automatiquement les échantillons sources au taux d'échantillonnage (entre 8 kHz et 384 kHz) et à la résolution désirés (virgule flottante de précision simple IEEE ou point fixe à 16, 20, 24 ou 32 bits par échantillon). Au cours du processus, l'ASRC convertit toutes les données d'entrée en un format IEEE 64 bits à virgule flottante afin d'assurer une conversion ascendante ou descendante précise des données d'échantillons audio, selon les besoins, pour obtenir le résultat souhaité.

Gestion de l'alimentation à l'aide d'un contrôleur général de puissance

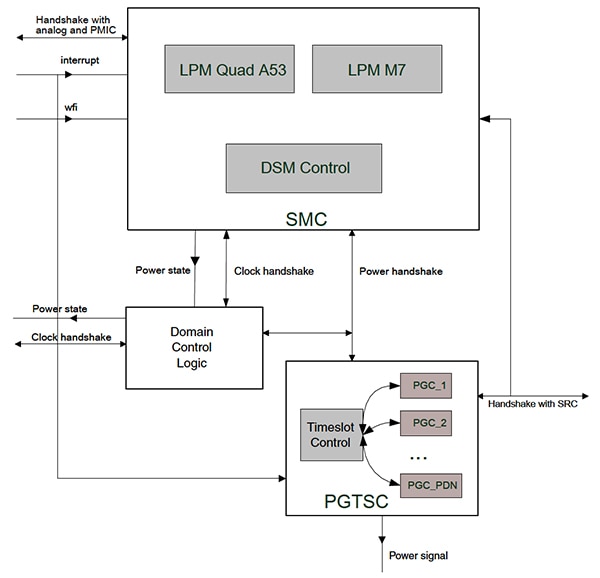

Avec son intégration étendue de cœurs de processeur et de sous-systèmes matériels, l'architecture du processeur i.MX 8M Nano de NXP combine un certain nombre de domaines de puissance et de modes d'alimentation distincts, intégrés dans les cœurs et les sous-systèmes individuels. Pour gérer l'alimentation de cette collection de cœurs et de blocs spécialisés, le processeur i.MX 8M Nano inclut un contrôleur général de puissance (GPC) sophistiqué conçu pour coordonner plusieurs fonctions de gestion de l'alimentation. Dans le GPC, le contrôleur de mode système (SMC) gère le mode basse consommation (LPM) et le mode de veille profonde (DSM) de chaque cœur, tandis qu'un contrôleur de créneau temporel de déclenchement de l'alimentation (PGTSC) gère les fonctions de déclenchement de l'horloge utilisées pour réduire l'alimentation du système en désactivant l'alimentation des sous-systèmes inactifs (Figure 5).

Figure 5 : Pour optimiser l'alimentation niveau système, le processeur i.MX 8M Nano de NXP intègre un contrôleur de puissance complet qui gère les fonctions de déclenchement de l'alimentation et les modes basse consommation intégrés aux cœurs de processeur. (Source de l'image : NXP)

Figure 5 : Pour optimiser l'alimentation niveau système, le processeur i.MX 8M Nano de NXP intègre un contrôleur de puissance complet qui gère les fonctions de déclenchement de l'alimentation et les modes basse consommation intégrés aux cœurs de processeur. (Source de l'image : NXP)

Sous contrôle logiciel ou matériel, le GPC utilise 20 intervalles de temps différents dans le contrôleur PGTSC pour mettre sous tension ou hors tension l'un des multiples domaines de puissance à déclenchement par horloge du processeur. Ici, le contrôleur de créneau temporel fonctionne de manière séquentielle à travers ces créneaux, en activant toute demande de mise sous tension ou hors tension avant de passer au créneau suivant. En plus de répondre à des exigences spécifiques en matière de séquencement de l'alimentation, cette approche permet aux développeurs de réduire l'augmentation du courant lors de la mise sous tension du système, ou lors de l'activation du système depuis un mode basse consommation ou de veille profonde.

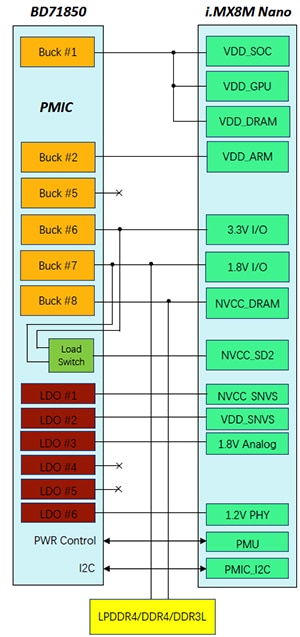

L'alimentation des multiples domaines de puissance du processeur i.MX 8M Nano est simple. Conçu spécifiquement pour prendre en charge le processeur i.MX 8M Nano de NXP, le circuit intégré de gestion de l'alimentation (PMIC) BD71850MWV de ROHM Semiconductor fournit tous les rails d'alimentation requis par le processeur et par d'autres périphériques du système. En fait, le PMIC BD71850MWV intègre son propre séquenceur d'alimentation, ce qui simplifie davantage l'exécution sécurisée de la mise sous tension et hors tension, non seulement pour le processeur mais également pour la mémoire externe, les capteurs ou les autres dispositifs du système (Figure 6). Pour les développeurs, l'intégration du PMIC BD71850MWV dans une conception ne nécessite aucun composant supplémentaire, en dehors des condensateurs de découplage habituels (non illustrés).

Figure 6 : Les multiples sous-systèmes matériels et cœurs du processeur i.MX 8M Nano de NXP exigent l'utilisation de plusieurs rails d'alimentation, mais le circuit intégré de gestion de l'alimentation (PMIC) BD71850MWV de ROHM fournit une solution prête à l'emploi. (Source de l'image : NXP)

Figure 6 : Les multiples sous-systèmes matériels et cœurs du processeur i.MX 8M Nano de NXP exigent l'utilisation de plusieurs rails d'alimentation, mais le circuit intégré de gestion de l'alimentation (PMIC) BD71850MWV de ROHM fournit une solution prête à l'emploi. (Source de l'image : NXP)

Support de développement

Bien que les exigences d'interface matérielle pour les conceptions basées sur le processeur i.MX 8M Nano soient relativement simples, NXP permet aux développeurs d'éviter cette tâche de conception relativement simple pour évaluer le processeur ou prototyper de nouveaux produits intelligents. Fournissant une conception de référence et un kit de développement entièrement mis en œuvre pour le processeur i.MX 8M Nano, le kit d'évaluation 8MNANOD4-EVK combine le processeur i.MX 8M Nano et le PMIC BD71850MWV avec le module d'émetteur-récepteur Wi-Fi/Bluetooth LBEE5HY1MW de Murata Electronics afin de fournir une plateforme pour l'évaluation et le développement de prototype immédiats. En plus des multiples options d'interface et des connecteurs associés, le kit d'évaluation inclut un ensemble complet de dispositifs de mémoire externe, notamment une mémoire SDRAM, une mémoire Flash NOR et une mémoire Flash NAND. Grâce au kit d'évaluation, les développeurs peuvent explorer différents modes de fonctionnement et différentes configurations, y compris le démarrage à partir d'une mémoire Flash externe ou le démarrage sécurisé à l'aide d'images de démarrage signées.

Lorsque les développeurs sont prêts à procéder à leur propre développement de logiciel personnalisé, NXP fournit des pilotes, des packs BSP (Board Support Package) et des intergiciels conçus pour fonctionner avec son propre environnement de développement intégré (IDE) MCUXpresso, ainsi qu'avec des IDE tiers. Pour créer des applications conçues pour exploiter les méthodes d'apprentissage automatique, les développeurs peuvent se tourner vers l'environnement de développement logiciel d'apprentissage automatique eIQ de NXP et les bibliothèques d'inférences optimisées i.MX telles que eIQ pour TensorFlow Lite pour inférence basée sur Cortex-M7, ou le port du kit de développement logiciel de réseau neuronal Arm (NN SDK) de NXP pour inférence basée sur Cortex-A53.

Conclusion

Dynamisés par l'acceptation rapide des produits d'assistants vocaux, les produits intelligents de nouvelle génération doivent faire face à des attentes croissantes, non seulement pour une meilleure prise en charge audio, mais également pour des performances supérieures, des graphiques améliorés et un fonctionnement écoénergétique. Pour les développeurs, cependant, la conception de systèmes efficaces pour ces produits exige une combinaison d'exécution logicielle d'applications hautes performances et de capacités en temps réel à faible latence, qui a été difficile à atteindre compte tenu des contraintes de taille, de coût et de puissance associées. Grâce à la disponibilité d'une gamme évolutive de processeurs multicœurs de NXP, les développeurs peuvent facilement répondre aux exigences de conception de produits intelligents dans un large éventail de segments d'application, notamment les secteurs grand public, industriels et médicaux.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.