Utiliser un seul processeur HMP ultrabasse consommation pour les charges de travail de traitement des applications et en temps réel

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-08-06

Les consommateurs s'attendent à ce que les appareils électroniques personnels et autres dispositifs mobiles offrent à la fois une réponse plus rapide et de meilleures fonctionnalités, tout en prolongeant la durée de vie de la batterie. Pour les développeurs, toutefois, les exigences en matière de réponse en temps réel et de performances élevées dans de nombreuses applications ont imposé l'utilisation de processeurs distincts pour répondre à ces demandes contradictoires. Cela augmente les coûts, la puissance et l'espace, ainsi que la complexité du logiciel et de la disposition du matériel.

Une meilleure approche consisterait à intégrer le matériel requis dans une seule puce. Intégrez des dispositifs de traitement multicœur hétérogène (HMP). Contenant plusieurs cœurs de types différents, ces processeurs peuvent offrir des avantages en termes d'optimisation des performances, de réduction de la consommation d'énergie et d'amélioration de la sécurité et de la fiabilité du système.

Cet article explique comment les développeurs peuvent utiliser un processeur multicœur hétérogène de NXP Semiconductors pour répondre à la demande de ces charges de travail mixtes, sans compromettre les exigences de basse consommation et de complexité de conception réduite.

Des exigences changeantes

Les avancées dans les technologies de capteurs et les algorithmes de traitement des données ont offert aux développeurs de nombreuses opportunités de gérer les demandes contradictoires liées à l'acquisition des données en temps réel et à l'exécution d'algorithmes gourmands en ressources informatiques. Dans le passé, les développeurs ont généralement partitionné ces charges de travail en systèmes distincts.

Au niveau le plus bas de la hiérarchie du réseau, les processeurs embarqués, tels que ceux basés sur le cœur Arm® Cortex®-M4, collectaient des données en exécutant un code optimisé sur un système d'exploitation en temps réel (RTOS) ou un système sans système d'exploitation. À un niveau plus élevé de la hiérarchie, les processeurs d'applications hautes performances, tels que ceux basés sur le cœur Arm Cortex-A7, exécutaient à leur tour des algorithmes d'analyse de données, exécutant du code d'application sur des systèmes d'exploitation connus, tels que Linux ou Android.

L'essor des systèmes informatiques de pointe a rapproché l'exécution du code d'application de la source de données. En effet, la demande pour une réponse plus rapide d'algorithmes d'analyse plus complexes a maintenant poussé les exigences de traitement des applications vers les dispositifs terminaux eux-mêmes. Les consommateurs attendent de plus en plus de capacités d'analyse sophistiquées, notamment avec des méthodes d'intelligence artificielle intégrées à des dispositifs tels que des capteurs Internet des objets (IoT), des dispositifs corporels et d'autres produits basse consommation.

Le rôle du traitement multicœur hétérogène

L'émergence de dispositifs HMP combinant des cœurs de processeur d'applications et embarqués a permis aux développeurs de gérer plus efficacement les charges de travail mixtes dans de nombreuses applications. Les processeurs HMP intègrent différents cœurs, chacun optimisé pour répondre aux différentes exigences associées à la charge de travail du produit cible. Avec la gamme de processeurs i.MX 7ULP (ultrabasse consommation) de NXP, les développeurs peuvent exploiter les capacités de performances d'une architecture HMP pour répondre à la demande sans compromis des consommateurs en matière de hautes performances et de durée de vie étendue des batteries dans les produits ultrabasse consommation nouvelle génération.

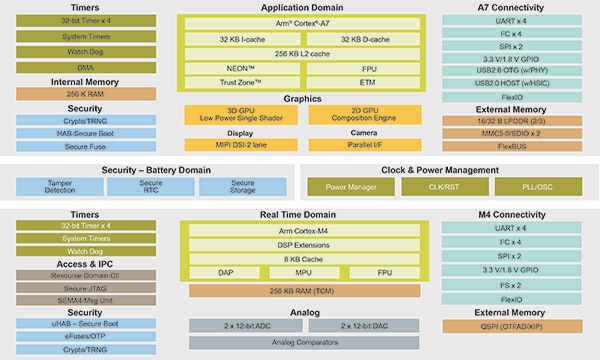

Disponibles en versions grand public (MCIMX7U5DVP07SC) et industrielles (MCIMX7U5CVP06SC), les processeurs i.MX 7ULP intègrent leurs cœurs hétérogènes à des unités de traitement graphiques, des accélérateurs de sécurité, des contrôleurs de mémoire et un ensemble complet d'interfaces périphériques (Figure 1).

Figure 1 : Outre un large éventail de modules et de périphériques, la gamme de processeurs d'applications i.MX 7ULP de NXP combine un cœur Arm Cortex-M4 pour le traitement en temps réel et un cœur Arm Cortex-A7 pour le traitement des applications. Elle utilise des domaines de puissance distincts pour optimiser la puissance et les performances. (Source de l'image : NXP)

Figure 1 : Outre un large éventail de modules et de périphériques, la gamme de processeurs d'applications i.MX 7ULP de NXP combine un cœur Arm Cortex-M4 pour le traitement en temps réel et un cœur Arm Cortex-A7 pour le traitement des applications. Elle utilise des domaines de puissance distincts pour optimiser la puissance et les performances. (Source de l'image : NXP)

Conçue spécialement pour les conceptions portables exposées à des contraintes de puissance, la gamme i.MX 7ULP de NXP répond aux nouvelles exigences en combinant un cœur Arm Cortex-A7 et un cœur Cortex-M4, chacun alimenté par un domaine de puissance distinct. De plus, l'utilisation de différents îlots de puissance permet d'éteindre différents modules de manière sélective lorsqu'ils ne sont pas nécessaires. Comme décrit ci-dessous, les fonctionnalités sophistiquées de gestion de la puissance intégrées aux dispositifs i.MX 7ULP permettent aux développeurs d'utiliser ces domaines et îlots de puissance pour optimiser les performances et la consommation énergétique en fonction de leurs applications.

Optimisation de la puissance

Lors de la conception de la gamme i.MX 7ULP, NXP a intégré des fonctionnalités d'optimisation de la puissance et des performances dans les dispositifs, en commençant au niveau de conception de la puce et s'étendant à l'ensemble de l'architecture.

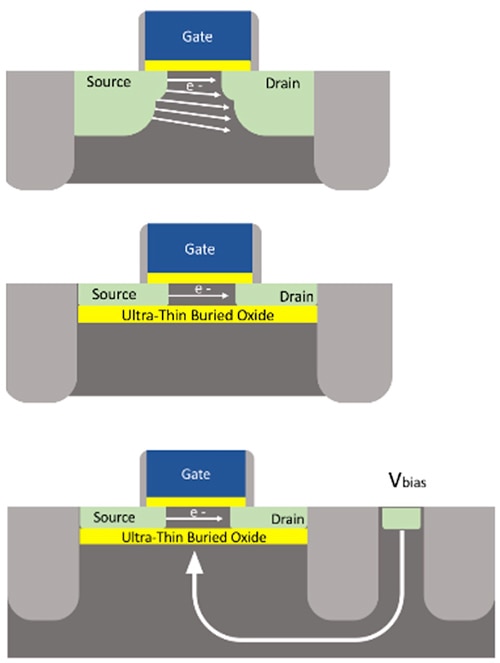

Au niveau le plus fondamental, la gamme i.MX 7ULP combine des méthodes de fabrication permettant de réduire les courants de fuite et des géométries de transistors diminuant les parasites, réduisant ainsi la consommation énergétique dynamique. Contrairement aux structures de transistor classiques (Figure 2, en haut), les dispositifs i.MX 7ULP sont fabriqués avec un oxyde enfoui ultramince (Figure 2, au milieu) qui réduit le flux d'électrons de la source vers le drain, réduisant ainsi le courant de fuite ; une amélioration supplémentaire permet aux concepteurs d'ajouter une polarisation de substrat directe (FBB) ou une polarisation de substrat inverse (RBB) (Figure 2, en bas).

Figure 2 : Un transistor conventionnel peut présenter des fuites considérables lorsque les électrons circulent de la source vers le drain (en haut), mais la gamme i.MX 7ULP de NXP est fabriquée avec un oxyde enfoui ultramince bloquant le flux d'électrons (au centre), et avec une structure qui accélère ou ralentit davantage le flux d'électrons avec une polarisation de substrat directe (FBB) ou une polarisation de substrat inverse (RBB) (en bas). (Source de l'image : NXP)

Figure 2 : Un transistor conventionnel peut présenter des fuites considérables lorsque les électrons circulent de la source vers le drain (en haut), mais la gamme i.MX 7ULP de NXP est fabriquée avec un oxyde enfoui ultramince bloquant le flux d'électrons (au centre), et avec une structure qui accélère ou ralentit davantage le flux d'électrons avec une polarisation de substrat directe (FBB) ou une polarisation de substrat inverse (RBB) (en bas). (Source de l'image : NXP)

Lorsque le rendement énergétique est une priorité absolue, les développeurs peuvent utiliser la polarisation RBB pour réduire le flux d'électrons et réduire davantage le courant de fuite et la consommation énergétique globale du dispositif, au détriment des performances. Inversement, les développeurs peuvent utiliser la polarisation FBB, qui améliore le flux d'électrons, pour améliorer les performances au détriment de la consommation énergétique, et ce, en raison d'un courant de fuite plus élevé.

Au niveau de la conception de la puce, la gamme i.MX 7ULP intègre de nombreuses techniques, notamment l'échelonnement dynamique de la fréquence (DFS) et l'échelonnement dynamique de la tension (DVS), une porte d'horloge basée sur logiciel et le déclenchement de puissance (power gating) basé sur logiciel. Outre la réduction de la consommation énergétique de différents périphériques, les développeurs peuvent utiliser ces fonctionnalités pour arrêter, de manière sélective, des blocs de mémoire interne ou pour placer la mémoire dans différents modes d'économie d'énergie.

Au niveau de l'architecture, la capacité d'ajustement de la puissance et des performances est encore étendue avec l'utilisation de plusieurs domaines de puissance, y compris les domaines de puissance distincts mentionnés précédemment, pour les sous-systèmes Cortex-A7 et Cortex-M4.

Chacun des domaines de puissance de base du processeur inclut des circuits d'attaque FBB et RBB, des régulateurs à faible chute de tension (LDO) dédiés et des moniteurs de détecteur de niveau haut (HVD) et de détecteur de niveau bas (LVD) conçus pour signaler les excursions d'alimentation au-dessus ou en dessous des seuils désignés. Un moniteur distinct de réinitialisation à la mise sous tension (PoR) suit le niveau de tension dans le domaine de puissance toujours actif.

Outre les domaines de puissance de base distincts, des domaines de puissance individuels contrôlent également des fonctions système telles que le matériel toujours actif, tandis qu'un domaine sur batterie gère l'alimentation des fonctions critiques, notamment l'horloge temps réel et un module de stockage non volatil sécurisé, entre autres. Comme pour les domaines de puissance de base, chacun de ces domaines de puissance spécialisés prend en charge un ensemble complet de fonctionnalités d'économie d'énergie spécialisées (trop nombreuses pour être traitées individuellement dans un seul article).

À titre d'exemple, le domaine de puissance pour la fonctionnalité toujours active comprend un module LLWU (Low-Leakage Wake-Up Unit) qui permet aux développeurs d'utiliser plusieurs broches externes ou modules internes comme source d'activation pour les modes d'alimentation spéciaux à faible fuite décrits ci-dessous.

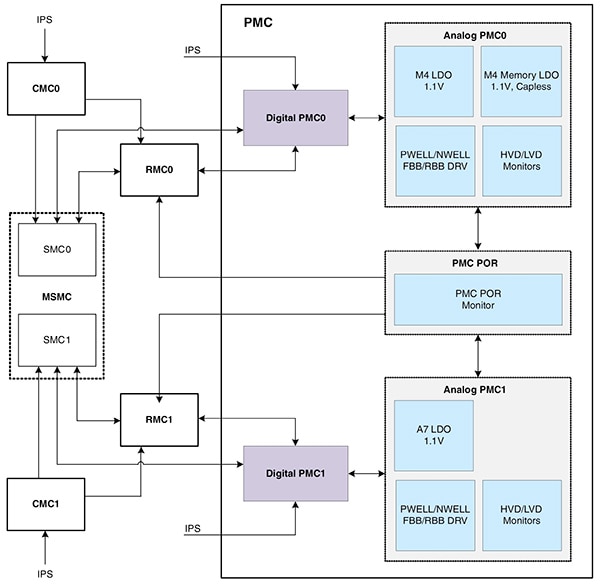

Ces fonctionnalités architecturales sont liées dans le contrôleur de gestion de l'alimentation intégré au dispositif, qui gère ces domaines de puissance distincts et les îlots de puissance du dispositif (Figure 3).

Figure 3 : La gamme i.MX 7ULP de NXP intègre une fonctionnalité de contrôle sophistiquée qui permet aux développeurs de configurer par programme les domaines de puissance et les îlots de puissance pour adapter la puissance et les performances à la demande en constante évolution. (Source de l'image : NXP)

Figure 3 : La gamme i.MX 7ULP de NXP intègre une fonctionnalité de contrôle sophistiquée qui permet aux développeurs de configurer par programme les domaines de puissance et les îlots de puissance pour adapter la puissance et les performances à la demande en constante évolution. (Source de l'image : NXP)

Dans cette approche, les développeurs initient des transitions de mode de puissance en envoyant des commandes via le bus du sous-système périphérique intelligent (IPS) normal vers un complexe de contrôle comprenant trois modules étroitement couplés :

- CMC (Core Mode Controller), qui prend en charge plusieurs fonctions principales

- MSMC (Multicore System Mode Controller), comprenant SMC0 (System Mode Controller 0) pour le domaine de puissance Cortex-M4 et SMC1 pour le domaine de puissance Cortex-A7, qui gère le séquencement entre différents modes de puissance, surveille les événements utilisés pour initier les transitions de mode de puissance et contrôle généralement les fonctionnalités de puissance, d'horloge et de mémoire associées à l'optimisation de la puissance

- RMC (Reset Mode Controller), qui gère les fonctions de réinitialisation de la puce

Ajustement de la puissance et des performances

Pour toutes ses capacités de gestion de la puissance, la gamme i.MX 7ULP présente un modèle de programmation bien connu des développeurs. Comme avec les autres processeurs avancés, les dispositifs i.MX 7ULP atteignent différents états de fonctionnement basse consommation grâce à une série de modes basse consommation programmables. En effet, les cœurs de processeur i.MX 7ULP prennent en charge plusieurs modes basse consommation contrôlés par logiciel, ce qui permet aux développeurs de réduire la consommation énergétique au niveau le plus bas possible, conformément aux fonctionnalités requises.

À l'aide de ces différents modes basse consommation, les développeurs peuvent définir un cœur ou les deux cœurs et leurs sous-systèmes dans différentes variantes d'un mode RUN normal, d'un mode WAIT et d'un mode STOP.

Le mode RUN normal et le mode HSRUN haute vitesse fournissent un fonctionnement hautes performances pour prendre en charge des parties d'une application nécessitant énormément de calculs. En mode HSRUN, le sous-système principal fonctionne à sa fréquence la plus élevée. Si l'application peut tolérer des performances inférieures, les développeurs peuvent définir le cœur en mode VLPR (Very Low Power Run) pour un fonctionnement à une fréquence maximum de 48 MHz avec une consommation plus basse correspondante.

En mode WAIT normal, les périphériques fonctionnent pleinement, mais le cœur fonctionne avec une porte d'horloge, attendant dans un état statique, mais prêt à être activé dès réception du signal WFI (Wait-For-Interrupt). Avec ce mode, les développeurs peuvent laisser des opérations périphériques autonomes remplir des mémoires tampons ou utiliser des transactions DMA (accès direct à la mémoire) pour remplir la mémoire système avant d'émettre une interruption qui sort le cœur de son état WAIT. Le mode VLPW (Very Low Power Wait) permet aux périphériques de continuer à fonctionner à la fréquence réduite, mais déclenche l'horloge principale.

Dans des applications telles que les dispositifs corporels ou portables, le système peut être soumis à de longues périodes d'inactivité, éventuellement interrompues périodiquement par des pics d'activité. Dans ce genre de situations, la capacité à économiser de l'énergie est essentielle pour l'autonomie de la batterie. Lorsque l'application peut tolérer un délai d'activation plus lent pour le cœur, la possibilité de placer le dispositif dans des états de veille encore plus profonds que les variations RUN, WAIT ou très basse consommation constitue une option particulièrement efficace. Pour prendre en charge cette approche, les développeurs peuvent placer chaque sous-système principal i.MX 7ULP dans un état de veille plus profond entraînant différents délais d'activation :

- À l'état STOP, certains périphériques peuvent fonctionner de manière asynchrone, mais le cœur reste dans un état statique avec des délais d'activation de 7 µs pour Cortex-A7 ou de 7 µs pour Cortex-M4.

- En mode VLPS (Very Low Power Stop), les opérations sur les périphériques sont encore limitées, mais le cœur reste dans un état statique avec des délais d'activation de 21,5 µs (Cortex-A7) ou 9 µs (Cortex-M4).

Pour les applications dont les exigences en matière de puissance sont encore plus strictes, les développeurs peuvent définir chaque cœur dans les modes spéciaux suivants à faible fuite qui arrêtent davantage de sous-systèmes de dispositifs :

- LLS (Low Leakage Stop), qui applique une porte d'horloge au niveau du cœur, du bus et des périphériques, laissant le cœur dans un état WFI, avec des délais d'activation de 40 µs (Cortex-A7) ou 58 µs (Cortex-M4)

- VLLS (Very Low Leakage Stop), qui applique une porte d'horloge à l'ensemble du domaine de puissance, entraînant des délais d'activation plus longs, notamment 60 μs pour Cortex-A7 ou 375 μs pour Cortex-M4

Pour encore plus d'économies d'énergie, les développeurs peuvent utiliser la fonction RBB dans certains modes de puissance, notamment VLPS et LLS, avec une réduction correspondante des performances et une augmentation incrémentielle du délai d'activation d'environ 2 à 4 μs.

À l'inverse, lorsqu'ils doivent gérer des charges de travail gourmandes en ressources de calcul, les développeurs peuvent exécuter les cœurs dans un mode spécial d'exécution haute vitesse (HSRUN). Le mode HSRUN fait passer le cœur Cortex-A7 de sa fréquence de fonctionnement normale de 500 MHz à un mode surmultiplié fonctionnant à 720 MHz.

Avec ce niveau de contrôle précis, les développeurs peuvent configurer l'i.MX 7ULP pour répondre aux exigences les plus extrêmes en matière de puissance, sans pour autant sacrifier les fonctionnalités essentielles. Par exemple, une application peut nécessiter la consommation énergétique la plus faible possible, mais également les fonctionnalités en temps réel du cœur Cortex-M4, ainsi que l'utilisation de périphériques ou de la mémoire spécifiques au sous-système Cortex-A7. Dans ce cas, le développeur peut placer le sous-système Cortex-A7 à l'état STOP ou VLPS, en accédant à sa mémoire ou à ses périphériques à partir du Cortex-M4 lorsque ce cœur effectue ses opérations en temps réel. Pour une économie d'énergie supplémentaire, les développeurs peuvent utiliser l'horloge Cortex-M4 pour commander les périphériques du Cortex-A7.

Une implémentation simple du système

Pour implémenter un système basse consommation avec l'i.MX 7ULP, les développeurs peuvent choisir parmi les modes de puissance et les configurations programmables par logiciel disponibles pour répondre aux exigences en matière de puissance et de performances. Du côté du matériel, la conception du système est encore plus simple.

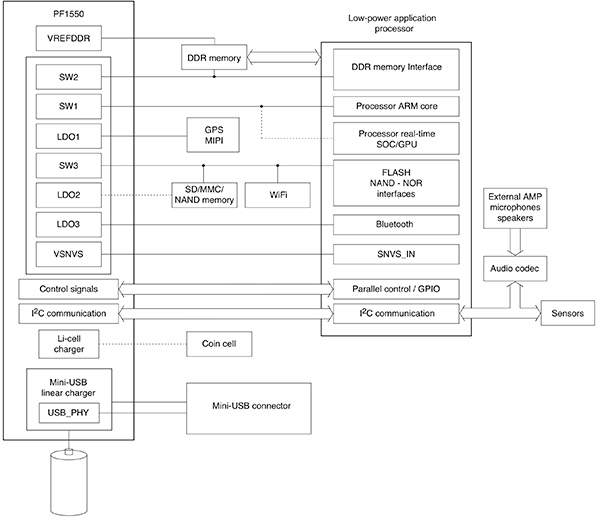

Pour les applications typiques, les développeurs peuvent simplement associer un processeur i.MX 7ULP avec le circuit intégré de gestion de l'alimentation (PMIC) MC32PF1550A3EPR2 de NXP pour réaliser une conception permettant de gérer des charges de travail mixtes, sans compromettre les budgets énergétiques limités (Figure 4).

Figure 4: Le circuit intégré de gestion de l'alimentation MC32PF1550A3EPR2 de NXP fournit l'ensemble complet de sources d'alimentation requises par le processeur i.MX 7ULP de NXP, réduisant la conception matérielle à une combinaison directe de ces deux dispositifs et de quelques composants passifs. (Source de l'image : NXP)

Figure 4: Le circuit intégré de gestion de l'alimentation MC32PF1550A3EPR2 de NXP fournit l'ensemble complet de sources d'alimentation requises par le processeur i.MX 7ULP de NXP, réduisant la conception matérielle à une combinaison directe de ces deux dispositifs et de quelques composants passifs. (Source de l'image : NXP)

Conçu spécifiquement pour prendre en charge les besoins en alimentation des processeurs NXP, comme la gamme i.MX 7ULP, le MC32PF1550A3EPR2 intègre trois régulateurs abaisseurs à découpage (SW1, SW2, SW3), trois régulateurs LDO (LDO1, LDO2, LDO3), une source de tension de référence mémoire, un chargeur de batterie lithium à une cellule complet et une mémoire OTP (One-Time Programmable) pour la configuration du dispositif.

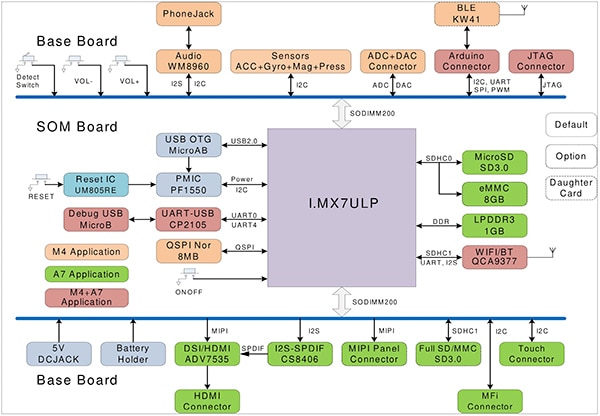

Avec son kit d'évaluation MCIMX7ULP-EVK, NXP démontre l'interface matérielle simple nécessaire pour combiner les dispositifs PMIC MC32PF1550A3EPR2 et i.MX 7ULP. Outre une carte de système sur module (SOM) contenant le processeur i.MX 7ULP et le PMIC MC32PF1550A3EPR2, le kit comprend une carte mère avec plusieurs capteurs, une capacité sans fil, un codec audio, un connecteur SD et de nombreux autres connecteurs, notamment JTAG et Arduino (Figure 5).

Figure 5 : Le kit d'évaluation MCIMX7ULP-EVK combine une carte de système sur module contenant un processeur i.MX 7ULP et un PMIC MC32PF1550A3EPR2 avec une carte mère contenant des capteurs, des connecteurs et d'autres composants nécessaires pour accélérer le développement logiciel avec les dispositifs i.MX 7ULP. (Source de l'image : NXP)

Figure 5 : Le kit d'évaluation MCIMX7ULP-EVK combine une carte de système sur module contenant un processeur i.MX 7ULP et un PMIC MC32PF1550A3EPR2 avec une carte mère contenant des capteurs, des connecteurs et d'autres composants nécessaires pour accélérer le développement logiciel avec les dispositifs i.MX 7ULP. (Source de l'image : NXP)

Tandis que le kit d'évaluation offre des fonctionnalités prêtes à l'emploi, NXP fournit également aux développeurs des outils, des packs de support de carte et des fichiers de conception téléchargeables pour les logiciels personnalisés utilisant FreeRTOS pour le code en temps réel, et Linux ou Android pour le code d'applications.

Conclusion

La demande en matière de fonctionnalités plus sophistiquées et de plus longue durée de vie de la batterie dans les produits mobiles a toujours contraint les développeurs à un certain niveau de compromis entre puissance et performances. De plus, les attentes croissantes en données actualisées provenant de davantage de capteurs dans les dispositifs IoT, les dispositifs corporels et d'autres produits portables ont imposé un compromis supplémentaire entre les capacités en temps réel et les performances au niveau des applications.

Toutefois, comme illustré ici, les développeurs peuvent se tourner vers des architectures HMP telles que celles utilisées dans la gamme de processeurs i.MX 7ULP de NXP pour répondre aux exigences strictes en matière de consommation énergétique ultrabasse, sans sacrifier les capacités.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.