Utiliser un processeur multicœur pour concevoir des produits multimédias intelligents basse consommation

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-03-26

Les produits intelligents associent de plus en plus les exigences traditionnelles de conception intégrée en temps réel à des logiciels plus exigeants au niveau de l'application. En plus d'une charge de calcul plus importante, ces produits doivent prendre en charge l'interaction utilisateur sur des services de médias avancés, tels que des écrans tactiles, des graphismes 3D haute résolution et des capteurs d'image.

Alors même que les exigences augmentent, les développeurs sont confrontés à une pression accrue pour réduire la consommation énergétique, les coûts et la taille du système, ce qui les oblige à trouver des alternatives plus efficaces aux conceptions traditionnelles à sous-systèmes multiples.

Cet article aborde l'évolution des exigences de conception et la manière dont les processeurs ont, à ce jour, satisfait à ces exigences. Il présente ensuite les nouveaux processeurs de NXP Semiconductors et leur utilisation. Ces processeurs offrent aux développeurs une solution plus simple pour répondre à la demande croissante de conceptions capables de répondre à la fois aux besoins en temps réel et aux exigences de l'informatique applicative.

Adapter les processeurs pour préserver l'investissement dans le code

Il est courant chez les développeurs de faire évoluer la puissance de calcul de leurs conceptions à l'aide de microprocesseurs constitués de cœurs supplémentaires adaptés à des exigences spécifiques de traitement des applications. Grâce à cette méthode, les développeurs peuvent obtenir de meilleures performances tout en conservant la compatibilité avec la base existante de leur code et leur expérience avec cette gamme de dispositifs.

Avec la série de processeurs d'applications i.MX 6 de NXP, par exemple, les concepteurs peuvent conserver la compatibilité du code tout en ajustant les performances à l'aide d'un microprocesseur i.MX 6Solo équipé d'un seul cœur de processeur d'application Arm® Cortex®-A9, d'un i.MX 6Dual doté de deux cœurs ou d'un i.MX 6Quad à quatre cœurs.

Le même besoin de traitement adaptatif des applications évolue rapidement dans les conceptions autrefois considérées comme des systèmes intégrés traditionnels. Pour ces conceptions, les fabricants de produits cherchent à ajouter de l'intelligence aux appareils électroménagers, aux contrôleurs industriels, aux instruments médicaux et bien plus encore. Les fournisseurs de semi-conducteurs ont réagi en proposant des dispositifs HMP (traitement multicœur hétérogène) qui intègrent à la fois des cœurs de processeur d'application et des cœurs de processeur embarqué. À titre d'exemple, la gamme i.MX 8M de NXP associe jusqu'à quatre cœurs de processeur d'application Arm Cortex-A53 à un cœur de processeur embarqué Arm Cortex-M4.

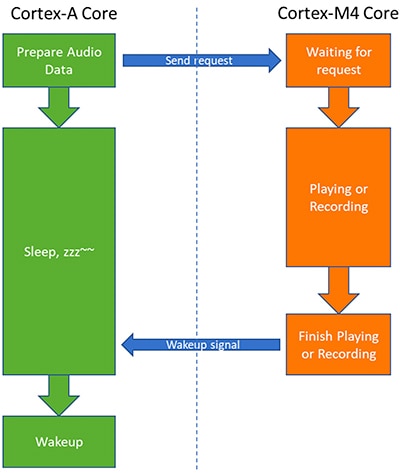

Grâce à ce dispositif unique, les développeurs peuvent élaborer des produits audio intelligents. Ces produits tirent pleinement parti du processeur d'application pour améliorer, filtrer ou manipuler les données audio. Le système audio repose alors sur le cœur de processeur embarqué pour exécuter les fonctions en temps réel nécessaires à la lecture (Figure 1). Tandis que les opérations en temps réel se déroulent sur le processeur embarqué, le processeur d'application peut être réglé en mode basse consommation afin de réduire la consommation énergétique globale. Lorsque les opérations en temps réel sont terminées, le processeur embarqué envoie simplement un signal d'activation au processeur d'application.

Figure 1 : Les processeurs multicœurs hétérogènes sont particulièrement efficaces pour les conceptions de produits intelligents, offrant à la fois des capacités de calcul hautes performances et en temps réel, sans compromettre les budgets énergétiques serrés. (Source de l'image : NXP Semiconductors)

En plus de ses cœurs hétérogènes, la gamme i.MX 8M de NXP intègre un ensemble complet de ressources multimédias, notamment une unité de traitement vidéo (VPU) 4K et une unité de traitement graphique (GPU) 3D hautes performances. La gamme peut ainsi représenter une solution efficace pour une catégorie croissante de produits vidéo et graphiques 3D intelligents.

Les développeurs qui élaborent des systèmes hautes performances doivent néanmoins faire face à une demande croissante de réduction de la consommation énergétique, aussi bien pour les systèmes alimentés par batterie que pour ceux alimentés par le réseau. Pour répondre à cette demande, la gamme de processeurs i.MX 8M Mini de NXP est fabriquée à l'aide d'une technologie avancée de traitement des semi-conducteurs qui répond aux besoins contradictoires de traitement hautes performances de charges mixtes et de réduction de la consommation énergétique.

Calcul hautes performances et basse consommation

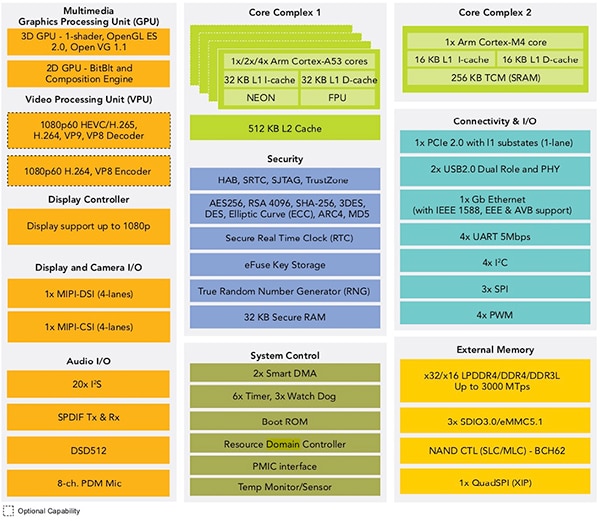

En tant que première gamme de dispositifs HMP de NXP fabriquée avec une technologie FinFET de 14 nanomètres (nm), les processeurs i.MX 8M Mini de NXP sont conçus pour les systèmes industriels émergents et ceux de l'Internet des objets (IoT) qui associent des exigences de performances élevées, de sécurité renforcée et de faible consommation. Tout comme la gamme i.MX 8M de NXP, l'i.MX 8M Mini de NXP intègre un cœur Arm Cortex-M4 pour le traitement embarqué et jusqu'à quatre cœurs Arm Cortex-A53 pour le traitement d'applications, ainsi qu'un sous-système complet de sécurité et diverses options de connectivité et d'E/S (Figure 2).

Figure 2 : Le processeur i.MX 8M Mini de NXP associe jusqu'à quatre cœurs de processeur d'application Arm Cortex-A53 et un cœur embarqué Arm Cortex-M4 à un éventail complet de fonctionnalités de sécurité, d'options multimédias, de fonctions système et d'interfaces d'E/S nécessaires dans les nouveaux produits intelligents. (Source de l'image : NXP Semiconductors)

Pour jouer son rôle dans les conceptions embarquées, l'i.MX 8M Mini limite le nombre de certains canaux d'E/S et les capacités haute résolution de son sous-système multimédia par rapport au précédent modèle i.MX 8M de NXP. À titre d'exemple, certains dispositifs i.MX 8M Mini, à savoir la version commerciale (MIMX8MM6DVTLZAA) et la version industrielle (MIMX8MM6CVTKZAAA), proposent une unité GPU à un nuanceur et une unité VPU de 1080p et 60 Hz, tandis que la gamme i.MX 8M de NXP propose une unité GPU à quatre nuanceurs et une unité VPU 4K. D'autres produits de la gamme i.MX 8M Mini, à savoir les dispositifs commerciaux (MIMX8MM5DVTLZAA) et industriels (MIMX8MM5CVTKZAA), éliminent complètement l'unité VPU. Comme pour le modèle i.MX 8M précédent de NXP, l'i.MX 8M Mini permet aux développeurs d'équilibrer davantage les performances et les coûts en profitant de la prise en charge par le processeur de plusieurs types de mémoire, notamment DDR3L (double débit de données version 3 basse tension), DDR4 et LPDDR4 (DDR4 basse consommation).

Consommation énergétique réduite

Pour améliorer davantage les performances et la consommation énergétique, les développeurs peuvent profiter de la capacité du modèle i.MX 8M Mini de NXP à basculer, de façon automatique ou programmée, vers des modes de fonctionnement basse consommation. Dans certaines conditions, les cœurs d'application peuvent automatiquement basculer en mode inactif, désactivant ainsi les unités GPU et VPU, ainsi que les cœurs en question, tout en utilisant la méthode de synchronisation d'horloge pour la majeure partie de la logique interne, mais en continuant d'alimenter le cache de données L2. Dans ce mode, le cœur Arm Cortex-M4 peut également continuer de fonctionner afin de réaliser plus de tâches de traitement embarqué traditionnelles, comme l'acquisition de données de capteur.

Le mode de suspension est le mode le plus économe en énergie, accentuant la réduction de consommation appliquée en mode inactif en désactivant également le contrôleur à double débit de données (DDRC) qui gère les interfaces mémoire. Enfin, le mode SNVS (stockage non volatile sécurisé) alimente uniquement la logique SNVS et l'horloge temps réel.

Les caractéristiques de réduction de la consommation d'énergie de la technologie FinFET de 14 nm utilisée sur l'i.MX 8M sont particulièrement perceptibles en modes de suspension et SNVS. Sur le modèle i.MX 8M Mini avec FinFET, le mode de suspension consomme environ 7,81 mW. Sur le modèle i.MX 8M précédent, le mode au fonctionnement similaire (appelé mode de veille prolongée) consomme 197 mW. Une réduction similaire de la consommation d'énergie s'applique au mode SNVS, dans lequel l'i.MX 8M Mini consomme environ 0,11 mW, contre environ 17 mW pour le modèle i.MX 8M précédent.

Avec tous les blocs fonctionnels et les modes de fonctionnement parfaitement réglés sur des dispositifs complexes comme l'i.MX 8M Mini, les ingénieurs sont confrontés à de nombreuses exigences strictes en matière de mise en œuvre. Comme d'autres dispositifs de cette catégorie, l'i.MX 8M Mini s'appuie sur divers domaines de puissance pour optimiser la gestion et l'efficacité énergétiques. Pour démarrer et arrêter ces dispositifs, il convient de respecter scrupuleusement des séquences spécifiques à la mise sous tension et hors tension.

La mise sous tension de l'i.MX 8M Mini commence par l'application d'une puissance, généralement de 1,8 V, au circuit de pré-attaque GPIO dans le banc SNVS. En 2 millisecondes (ms) (2,4 ms max.), 0,8 V (valeur typique) doit être appliqué à la logique fondamentale SNVS. Ce processus se poursuit par des signaux spécifiques ou par l'application d'une puissance aux broches de l'i.MX 8M Mini en suivant 12 étapes supplémentaires, chacune programmée pour se dérouler à des intervalles compris entre 0,015 ms et 20 ms.

La mise hors tension du dispositif suit la séquence en sens inverse, mais avec un délai constant de 10 ms entre les étapes successives. Dans les deux cas, le non-respect de ces consignes peut empêcher le démarrage du dispositif, entraîner un courant excessif lors de la mise sous tension ou, dans le pire des cas, causer des dommages irréversibles au dispositif.

La conception physique d'une carte à circuit imprimé destinée au processeur s'accompagne de ses propres exigences strictes. Pour l'installation du boîtier 486 billes de 14 mm x 14 mm du processeur, NXP recommande l'utilisation d'un empilage de cartes à circuit imprimé d'au moins huit couches, avec suffisamment de couches dédiées aux rails d'alimentation afin de respecter les consignes relatives à la chute de résistance au courant (IR). En même temps, les ingénieurs chargés de la configuration doivent veiller à une diaphonie minimale sur les lignes haute vitesse, notamment celles destinées aux dispositifs de mémoire pris en charge et fonctionnant à des vitesses de 1,5 GHz et 3000 MT/s.

Développement rapide

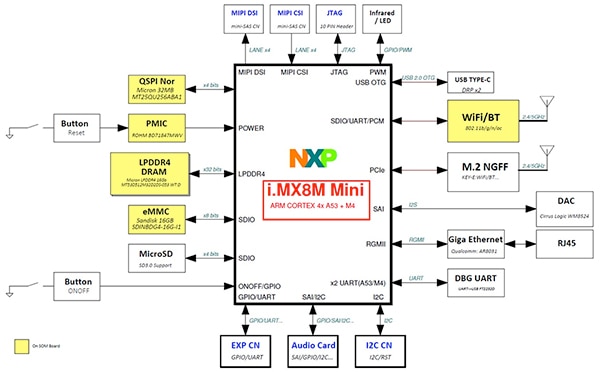

Afin d'aider les ingénieurs à rapidement lancer le développement d'une application ou à accélérer le développement de conceptions matérielles personnalisées, NXP propose le kit d'évaluation i.MX 8M Mini EVK et sa conception de référence associée (Figure 3). Fourni sous la forme d'une carte de base et d'une carte SOM (système sur module), ce kit d'évaluation offre un système complet comprenant une mémoire LPDDR4 externe et Flash, ainsi que des interfaces USB et autres.

Figure 3 : L'ensemble de cartes du kit i.MX 8M Mini EVK de NXP fournit une plateforme système complète pour une évaluation immédiate des processeurs i.MX 8M Mini et un développement rapide d'applications de processeurs multicœurs hétérogènes. (Source de l'image : NXP Semiconductors)

Outre Gigabit Ethernet, le kit inclut des options de connectivité Wi-Fi et Bluetooth. Des cartes d'extension comprenant le module de caméra MINISASTOCSI et l'écran tactile à diode électroluminescente organique (OLED) MX8-DSI-OLED1 peuvent compléter la conception pour les applications vidéo et d'affichage.

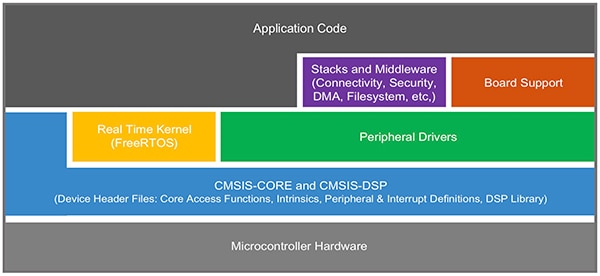

Grâce aux images pré-construites destinées aux environnements d'exploitation Embedded Linux® et Embedded Android®, les développeurs peuvent immédiatement utiliser le kit pour évaluer le processeur i.MX 8M Mini et exécuter des applications d'exemple. Pour les développeurs qui créent leurs propres applications logicielles, NXP propose son kit de développement logiciel (SDK) MCUXpresso gratuit, qui offre un ensemble complet de composants logiciels afin de créer une application embarquée hautes performances type (Figure 4).

Figure 4 : L'architecture du kit de développement logiciel (SDK) MCUXpresso comprend l'ensemble complet de couches logicielles, notamment les pilotes, un BSP (board support package) et des composants facultatifs nécessaires au développement de la plupart des applications embarquées. (Source de l'image : NXP Semiconductors)

Grâce au tableau de bord SDK MCUXpresso en ligne de NXP, les développeurs peuvent définir une configuration SDK pour la chaîne d'outils GCC Arm Embedded ou IAR Embedded Workbench for Arm. Le tableau de bord permet également aux développeurs d'ajouter des composants intergiciels facultatifs, notamment la bibliothèque DSP CMSIS (norme relative à l'interface logicielle des microcontrôleurs ARM Cortex) et Amazon FreeRTOS. La distribution SDK configurée comprend des bibliothèques standard Arm, des pilotes périphériques, des wrappers de pilotes périphériques pour FreeRTOS et un ensemble complet d'exemples logiciels. Parmi les exemples logiciels de la distribution SDK, des applications présentent un modèle de conception pour l'échange de messages clés, essentiel à l'informatique hétérogène.

Dans tout environnement informatique multicœur, les processeurs distincts nécessitent des mécanismes efficaces afin de transmettre les demandes et de partager les données. Pour les applications du kit i.MX 8M Mini EVK, NXP utilise RPMsg-Lite, une version légère du protocole RPMsg (Remote Processor Messaging). Ce protocole a été créé dans le cadre du projet OpenAMP (Open Asymmetric Multi Processing) afin de fournir une interface standard destinée à la communication entre plusieurs cœurs dans un système multicœur hétérogène. RPMsg-Lite de NXP répond au manque de ressources dans les systèmes embarqués plus petits, en offrant une empreinte réduite et en éliminant les fonctionnalités qui ne correspondent pas à ces systèmes.

Dans la distribution SDK, une application d'exemple, rpmsg_lite_pingpong_rtos, présente un échange rudimentaire, en utilisant RPMsg-Lite pour implémenter une interaction simple de type « ping-pong » entre différents processeurs (Liste 1). Après la création d'une file d'attente RPMsg (my_queue) et d'un point final (my_ept) pour l'autre processeur « distant », le processeur d'application « hôte » envoie un signal au cœur distant. Après la réception d'une réponse de mise en liaison de la part du cœur distant, l'hôte entame une boucle utilisant une attente de blocage pour tout message « ping » de la part du cœur distant, avant d'envoyer sa propre réponse « pong ».

Copier void app_task(void *param) { .

.

.

my_rpmsg = rpmsg_lite_remote_init((void *)RPMSG_LITE_SHMEM_BASE, RPMSG_LITE_LINK_ID, RL_NO_FLAGS); while (!rpmsg_lite_is_link_up(my_rpmsg)) ; PRINTF("Link is up!\r\n"); my_queue = rpmsg_queue_create(my_rpmsg); my_ept = rpmsg_lite_create_ept(my_rpmsg, LOCAL_EPT_ADDR, rpmsg_queue_rx_cb, my_queue); ns_handle = rpmsg_ns_bind(my_rpmsg, app_nameservice_isr_cb, NULL); rpmsg_ns_announce(my_rpmsg, my_ept, RPMSG_LITE_NS_ANNOUNCE_STRING, RL_NS_CREATE); PRINTF("Nameservice announce sent.\r\n"); /* Wait Hello handshake message from Remote Core. */ rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, helloMsg, sizeof(helloMsg), NULL, RL_BLOCK); while (msg.DATA <= 100) { PRINTF("Waiting for ping...\r\n"); rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, (char *)&msg, sizeof(THE_MESSAGE), NULL, RL_BLOCK); msg.DATA++; PRINTF("Sending pong...\r\n"); rpmsg_lite_send(my_rpmsg, my_ept, remote_addr, (char *)&msg, sizeof(THE_MESSAGE), RL_BLOCK); } PRINTF("Ping pong done, deinitializing...\r\n"); rpmsg_lite_destroy_ept(my_rpmsg, my_ept); my_ept = NULL; rpmsg_queue_destroy(my_rpmsg, my_queue); my_queue = NULL; rpmsg_ns_unbind(my_rpmsg, ns_handle); rpmsg_lite_deinit(my_rpmsg); msg.DATA = 0; .

.

.

}

Liste 1 : Cet extrait de code d'exemple fourni dans le kit de développement logiciel MCUXpresso présente le modèle de conception de base pour mettre en place des interactions entre différents processeurs dans un processeur multicœur hétérogène. (Source du code : NXP Semiconductors)

Les développeurs peuvent facilement se baser sur cet échange simple pour créer des opérations complètes conçues pour répartir l'exécution des tâches entre plusieurs processeurs. Une autre application d'exemple, sai_low_power_audio, utilise RPMsg-Lite essentiellement en tant que couche liaison de données de niveau inférieur pour un protocole d'application SRTM (Simplified Real Time Messaging) de niveau supérieur. Dans cette application, un processeur Arm Cortex-A53 utilise ce protocole SRTM pour demander au processeur Arm Cortex-M4 de lire un fichier audio situé en mémoire partagée. Après la prise de contrôle du tampon partagé, le processeur M4 réalise plusieurs opérations, pour terminer par l'exécution d'une transaction SDMA (accès intelligent direct à la mémoire) afin de transférer les données vers le code approprié et, finalement, vers l'interface audio série (SAI) pour la sortie audio. Lors de l'opération, le cœur A53 peut passer en mode basse consommation. Bien que de conception plus complexe que l'application de type ping-pong, l'application d'exemple sai_low_power_audio démontre comment les développeurs peuvent utiliser des processeurs multicœurs hétérogènes pour optimiser les performances tout en réduisant la consommation énergétique des produits intelligents.

Conclusion

Les produits intelligents associent des systèmes traditionnels de traitement embarqué en temps réel à une capacité considérable de traitement d'applications. Pour autant, les développeurs doivent satisfaire à ces exigences de traitement tout en répondant aux attentes constantes liées aux produits basse consommation, qu'il s'agisse de systèmes alimentés par batterie ou par réseau.

Fabriqué à l'aide d'un processus à semi-conducteurs avancé, le processeur d'applications i.MX 8M Mini de NXP offre l'équilibre parfait entre basse consommation et capacité de traitement multicœur hétérogène hautes performances. Grâce aux dispositifs i.MX 8M Mini de NXP, les développeurs peuvent répondre plus efficacement aux nouvelles exigences en matière de calcul hautes performances dans des conceptions de systèmes embarqués, nécessaires à des produits intelligents de plus en plus sophistiqués.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.