Principes fondamentaux des synthétiseurs de fréquences à boucle à verrouillage de phase

Avec la contribution de Rédacteurs nord-américains de DigiKey

2021-02-03

L'augmentation des débits de données dans les bus de communications série haute vitesse requiert des horloges systèmes avec des fréquences plus élevées, une stabilité supérieure, une plus haute résolution en fréquence et une plus grande pureté du signal. Les synthétiseurs numériques directs offrent ces caractéristiques, mais uniquement à des fréquences inférieures à 2 gigahertz (GHz) ou 3 GHz. Une solution est requise pour les fréquences atteignant plusieurs dizaines de gigahertz.

Cette solution commence avec des synthétiseurs de fréquences analogiques à boucle à verrouillage de phase (PLL) qui génèrent des fréquences d'horloge jusqu'à 30 GHz. Ensuite, les synthétiseurs entier-N (qui multiplient la fréquence de référence par une valeur entière) et les synthétiseurs fraction-N (qui multiplient la fréquence de référence par des valeurs fractionnaires non entières) utilisent des techniques spéciales qui réduisent le bruit de phase et les impuretés de signaux similaires.

Cet article décrit la conception des synthétiseurs de fréquences entier-N et fraction-N en utilisant des exemples de dispositifs d'Analog Devices. L'article souligne également les innovations qui permettent d'utiliser ces dispositifs à la fois pour les liaisons de données série haute vitesse et les radars à agilité de fréquence.

Synthétiseurs à boucle à verrouillage de phase entier-N

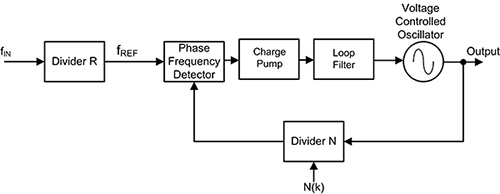

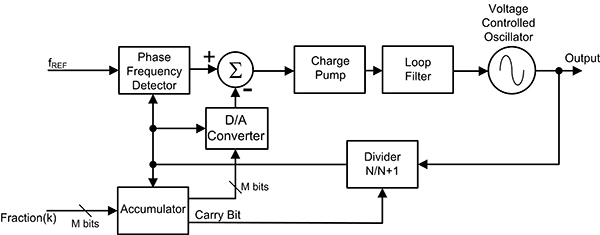

Les circuits PLL sont utilisés pour le contrôle de la fréquence et de la phase. Ils peuvent être configurés comme sources d'horloge, multiplicateurs de fréquence, démodulateurs, générateurs de suivi ou circuits d'extraction du signal d'horloge. Chacune de ces applications exige des caractéristiques différentes mais elles utilisent toutes le même concept de circuit de base. La Figure 1 montre le schéma fonctionnel d'une PLL de base configurée comme multiplicateur de fréquence.

Figure 1 : Schéma fonctionnel d'un synthétiseur de fréquences à boucle à verrouillage de phase entier-N classique. (Source de l'image : DigiKey Electronics)

Figure 1 : Schéma fonctionnel d'un synthétiseur de fréquences à boucle à verrouillage de phase entier-N classique. (Source de l'image : DigiKey Electronics)

Le fonctionnement de ce circuit est typique de toutes les boucles à verrouillage de phase. Il s'agit en fait d'un système de commande à rétroaction qui contrôle la phase d'un oscillateur commandé en tension (VCO). Le signal d'entrée est appliqué à un prédiviseur, qui divise la fréquence d'entrée par un facteur R. La sortie du prédiviseur est la fréquence de référence, qui constitue l'une des entrées d'un détecteur de phase-fréquence (PFD).

L'autre entrée PFD est un signal de retour provenant de la sortie d'un compteur de division par N. Normalement, si la PLL est verrouillée, les fréquences des deux signaux sont pratiquement identiques. La sortie du détecteur de phase est une tension proportionnelle à la différence de phase entre les deux entrées. Si la boucle est déverrouillée, comme cela se produit au démarrage, ou s'il y a un grand décalage instantané de la fréquence d'entrée, alors le détecteur de phase-fréquence fonctionne pour commander la fréquence de fonctionnement PLL au réglage souhaité. Lorsque cette fréquence est atteinte, le PFD repasse en mode de détecteur de phase et a une sortie proportionnelle à la différence de phase entre la fréquence de référence et le signal de retour.

Le détecteur de phase-fréquence actionne une pompe à charge, qui est une source de courant bipolaire commutée. Cela signifie qu'il peut émettre des impulsions de courant positives et négatives dans le filtre à boucle de la PLL.

Le filtre à boucle lisse le signal d'erreur de phase et détermine également les caractéristiques dynamiques de la PLL. Le signal filtré contrôle le VCO. Notez que la sortie du VCO présente une fréquence qui est égale à N fois l'entrée fournie à l'entrée de référence de fréquence du détecteur de phase-fréquence et est N/R fois l'entrée de fréquence. Le signal de sortie est renvoyé au détecteur de phase via le compteur de division par N.

Normalement, le filtre à boucle est conçu pour correspondre aux caractéristiques requises par l'application de la PLL. Si la PLL doit acquérir et suivre un signal, la bande passante du filtre à boucle est supérieure à celle nécessaire avec une fréquence d'entrée fixe. La gamme de fréquences que la PLL accepte et sur laquelle elle se verrouille est appelée la gamme de capture. Une fois que la PLL est verrouillée et suit un signal, la gamme de fréquences qu'elle suit est appelée la gamme de suivi. Généralement, la gamme de suivi est plus étendue que la gamme de capture. Le filtre à boucle de la PLL détermine également la vitesse à laquelle la fréquence du signal peut changer tout en maintenant le verrouillage, c'est-à-dire la vitesse de balayage maximum. Plus la bande passante du filtre à boucle est étroite, plus l'erreur de phase pouvant être générée est petite. Cela se fait aux dépens d'une réponse plus lente et d'une gamme de capture réduite. Les PLL utilisées dans les applications d'horloge fonctionnent essentiellement à des fréquences fixes. En général, la bande passante du filtre à boucle doit être bien inférieure à la fréquence de référence.

Comme la fréquence de sortie de la PLL est un multiple entier de la fréquence de référence, sa résolution en fréquence est égale à la fréquence de référence. Pour obtenir une résolution en fréquence plus fine, il faut diminuer la fréquence de référence, ce qui est fait avec le compteur prédiviseur R.

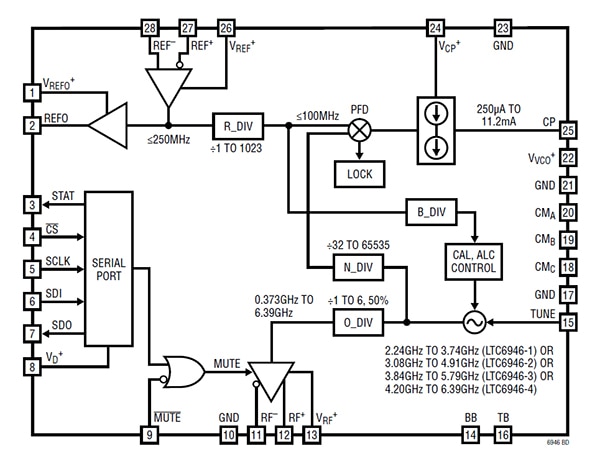

Un exemple commercial de synthétiseur de fréquences entier-N est le LTC6946IUFD-3#PBF d'Analog Devices, un synthétiseur à faible bruit de 0,64 GHz à 5,790 GHz avec un VCO intégré et d'excellentes performances parasites (Figure 2). Il fait partie d'une famille de quatre circuits intégrés de synthétiseurs, chacun présentant une gamme de fréquences différente, couvrant une gamme totale de 0,373 GHz à 6,390 GHz.

Figure 2 : Schéma fonctionnel du synthétiseur de fréquences entier-N LTC6946IUFD-3#PBF d'Analog Devices avec VCO intégré. (Source de l'image : Analog Devices)

Figure 2 : Schéma fonctionnel du synthétiseur de fréquences entier-N LTC6946IUFD-3#PBF d'Analog Devices avec VCO intégré. (Source de l'image : Analog Devices)

Ce synthétiseur requiert un filtre à boucle externe fourni par l'utilisateur, pouvant être optimisé pour l'application spécifique. Il y a un compteur prédiviseur interne avec une gamme de division de 1 à 1023. Le diviseur de boucle a une gamme de 32 à 65535. Le courant de la pompe à charge est ajustable de 250 microampères (μA) à 11,2 milliampères (mA) pour s'adapter aux exigences du filtre à boucle.

Synthétiseurs à boucle à verrouillage de phase fraction-N

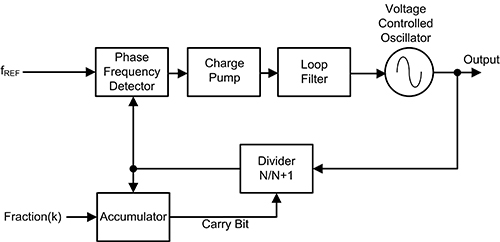

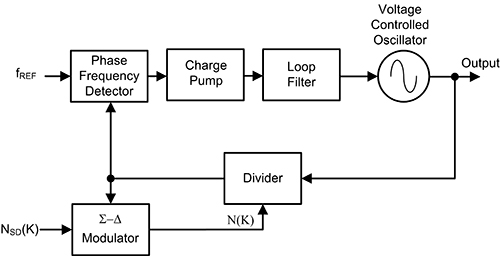

La résolution en fréquence du synthétiseur PLL peut être améliorée en réduisant la taille des pas en dessous de valeurs entières, c'est-à-dire en effectuant des pas fractionnaires dans le diviseur de boucle (N). Cela est accompli en variant (« dithering ») de manière dynamique la valeur de décompte. Cela signifie que le réglage du diviseur conserve la valeur N pendant un nombre fixe de cycles de la fréquence de sortie de la PLL et est périodiquement incrémenté sur une valeur différente, comme N+1. Par exemple, si le réglage du diviseur est de 4 pour trois périodes de référence et de 5 pour le quatrième cycle de référence, alors le décompte effectif est de 4,25. Une façon d'y parvenir est d'utiliser un accumulateur comme illustré à la Figure 3.

Figure 3 : Schéma fonctionnel d'un synthétiseur PLL fraction-N utilisant un accumulateur pour moduler le nombre de diviseurs. (Source de l'image : DigiKey Electronics)

Figure 3 : Schéma fonctionnel d'un synthétiseur PLL fraction-N utilisant un accumulateur pour moduler le nombre de diviseurs. (Source de l'image : DigiKey Electronics)

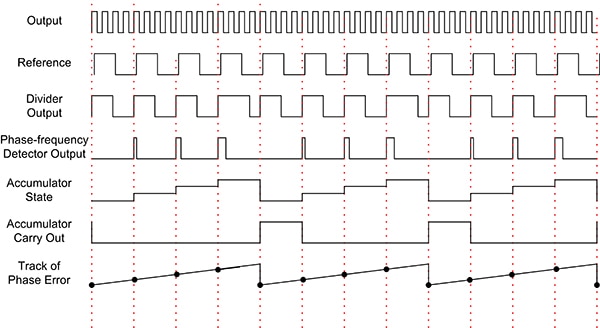

L'accumulateur compte les impulsions de sortie du diviseur, et à chaque M, où M est le module de l'accumulateur, il émet un bit de retenue qui modifie l'entrée du diviseur. La Figure 4 reprend l'exemple de la définition d'un réglage de diviseur fractionnaire à 4,25.

Figure 4 : Schéma de temporisation d'un synthétiseur fraction-N utilisant un accumulateur. (Source de l'image : DigiKey Electronics)

Figure 4 : Schéma de temporisation d'un synthétiseur fraction-N utilisant un accumulateur. (Source de l'image : DigiKey Electronics)

L'accumulateur est commandé par la sortie divisée et compte modulo quatre, c'est-à-dire que M est égal à quatre. Toutes les quatre impulsions, il génère une sortie de retenue, qui incrémente le nombre de diviseurs de 1. L'accumulateur se réinitialise et recommence à compter. L'augmentation du réglage du diviseur décale la fréquence de sortie, ce qui entraîne une erreur de décalage de phase cumulée. Le suivi de l'erreur de phase montre la valeur d'impulsion comme fonction du temps.

Le réglage moyen du diviseur est 4,25, mais la sortie du synthétiseur est modulée en phase, ce qui entraîne des tonalités parasites dans la sortie. En regardant l'état de l'accumulateur, il est évident qu'il suit l'erreur de phase. Cela peut être utilisé pour supprimer la modulation, comme illustré à la Figure 5.

Figure 5 : Utilisation de l'état de l'accumulateur converti N/A pour annuler la modulation de phase due à la variation fraction-N. (Source de l'image : DigiKey Electronics)

Figure 5 : Utilisation de l'état de l'accumulateur converti N/A pour annuler la modulation de phase due à la variation fraction-N. (Source de l'image : DigiKey Electronics)

L'état de l'accumulateur est converti en analogique par un convertisseur numérique-analogique (N/A), puis mis à l'échelle et soustrait de la sortie du détecteur de phase-fréquence pour annuler la modulation de phase due à la variation fraction-N. Cela demande une grande attention ; si le signal de correction ne correspond pas exactement à l'erreur de phase, des tonalités parasites se produiront à la sortie.

Modulateur sigma-delta

La périodicité dans l'accumulateur est la cause des sorties parasites du synthétiseur. Si l'accumulateur est remplacé par un modulateur sigma-delta, des techniques numériques peuvent alors être appliquées pour moduler le nombre de diviseurs de manière à minimiser les réponses parasites et le bruit. Ce remplacement est illustré à la Figure 6.

Figure 6 : Le remplacement de l'accumulateur par un modulateur sigma-delta permet d'appliquer des techniques numériques pour faire varier le nombre de diviseurs afin de réduire les réponses parasites. (Source de l'image : DigiKey Electronics)

Figure 6 : Le remplacement de l'accumulateur par un modulateur sigma-delta permet d'appliquer des techniques numériques pour faire varier le nombre de diviseurs afin de réduire les réponses parasites. (Source de l'image : DigiKey Electronics)

Il existe en fait deux techniques numériques courantes qui sont employées dans la topologie de modulation sigma-delta. La première consiste à augmenter le nombre de diviseurs N sur une plus large gamme de valeurs de sorte que le facteur de division moyen produise la valeur de diviseur fractionnaire souhaitée. Cela permet de réduire les parasites fractionnaires primaires. Le synthétiseur basé sur un accumulateur fait varier le nombre entre deux états. Il s'agit d'une méthode de modulation de premier ordre. Une PLL fractionnaire sigma-delta de n ordre module le compteur N entre 2n valeurs différentes. Par exemple, un modulateur de troisième ordre alternerait entre huit valeurs de diviseur différentes, et un modulateur de quatrième ordre alternerait entre 16 valeurs de diviseur différentes.

La deuxième technique numérique — également appelée « dithering » — consiste à randomiser la séquence 2N de manière à ce qu'elle soit pseudo-aléatoire. Tout en maintenant un rapport de diviseur fractionnaire moyen, elle convertit les parasites fractionnaires en un bruit aléatoire formé de sorte qu'il puisse être filtré par la PLL.

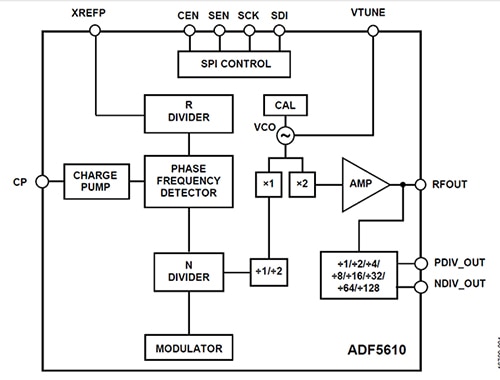

Une version commerciale d'un synthétiseur fraction-N sigma-delta est l'ADF5610BCCZ d'Analog Devices, un synthétiseur fraction-N à faible bruit de 0,57 mégahertz (MHz) à 14,6 GHz avec un VCO intégré (Figure 7).

Figure 7 : Schéma fonctionnel de l'ADF5610BCCZ d'Analog Devices qui prend en charge les configurations de synthétiseurs entier ou fraction-N. (Source de l'image : Analog Devices)

Figure 7 : Schéma fonctionnel de l'ADF5610BCCZ d'Analog Devices qui prend en charge les configurations de synthétiseurs entier ou fraction-N. (Source de l'image : Analog Devices)

L'ADF5610 requiert un oscillateur de référence et un filtre à boucle externes. Il est doté d'un VCO intégré avec une fréquence fondamentale de 3650 MHz à 7300 MHz. Ces fréquences sont doublées en interne et routées vers la broche RFOUT. Il existe une sortie différentielle qui permet de diviser la fréquence du VCO doublée par des facteurs de 1, 2, 4, 8, 16, 32, 64 ou 128, ce qui permet de générer des fréquences de sortie RF de seulement 57 MHz.

L'ADF5610 utilise un modulateur sigma-delta avancé avec un module fractionnaire de 24 bits permettant d'obtenir des niveaux de parasites exceptionnellement bas. Comme dans tous les synthétiseurs utilisant un modulateur sigma-delta, ce dispositif utilise des techniques de traitement des signaux numériques pour trouver le rapport de diviseur fractionnaire moyen souhaité. Ce processus, cadencé à la fréquence PFD, produit un bruit de modulation de sortie appelé distorsion de quantification avec une réponse en fréquence passe-haut. Le filtre à boucle passe-bas externe est utilisé pour filtrer cette distorsion de quantification à un niveau inférieur au bruit de phase du VCO, ce qui empêche le bruit de contribuer au bruit de phase global du système.

L'ADF5610 inclut également un mode de fréquence exacte pour l'erreur de fréquence 0 hertz (Hz). Ce mode est capable de générer des fréquences exactes entre des pas limites entier-N adjacents tout en utilisant le module d'accumulateur de phase 24 bits complet. Il atteint des pas en fréquence exacte avec un taux de comparaison de détecteur de phase élevé, ce qui permet à la PLL de maintenir un excellent bruit de phase et d'excellentes performances parasites dans ce mode.

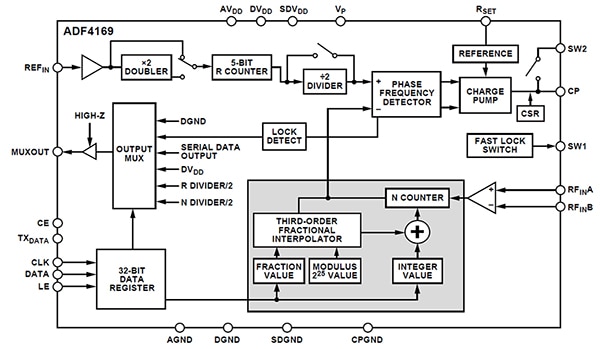

L'ADF4169CCPZ-RL7 d'Analog Devices est un autre exemple de synthétiseur PLL pouvant être configuré comme un dispositif entier-N ou fraction-N. Il fonctionne avec une bande passante RF jusqu'à 13,5 GHz, avec modulation et génération de formes d'ondes. Il utilise une entrée de fréquence de référence externe, un VCO et un filtre à boucle. Il est doté d'un modulateur sigma-delta du troisième ordre pour la synthèse fraction-N qui peut être désactivé, permettant au dispositif de fonctionner en mode entier-N (Figure 8).

Figure 8 : L'ADF4169CCPZ-RL7 d'Analog Devices utilise un modulateur sigma-delta de troisième ordre. (Source de l'image : Analog Devices)

Figure 8 : L'ADF4169CCPZ-RL7 d'Analog Devices utilise un modulateur sigma-delta de troisième ordre. (Source de l'image : Analog Devices)

Le synthétiseur ADF4158WCCPZ-RL7 est destiné à être utilisé dans les radars à ondes continues modulées en fréquence (FMCW). Il permet différents types de formes d'ondes modulées dans le domaine fréquentiel, y compris des rampes en dents de scie et triangulaires. Il s'agit d'une caractéristique particulière requise dans les applications radar.

Conclusion

L'augmentation des débits de données dans les bus de communications série haute vitesse contraint les concepteurs à se projeter au-delà des synthétiseurs numériques directs — qui fonctionnent mieux en dessous de 3 GHz — pour trouver des solutions d'horloge système. Les synthétiseurs de fréquences basés sur des PLL utilisant des topologies entier-N et fraction-N fournissent des signaux stables et à faible bruit pour les horloges haute fréquence, les communications de données série et les applications radar pour des fréquences atteignant des dizaines de gigahertz.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.