Amplificateurs logarithmiques : principes de base et mode de gestion des signaux à vaste plage dynamique

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-03-21

Le fait de devoir travailler avec des signaux à vaste plage dynamique constitue un problème majeur pour les concepteurs. Comment appliquer des signaux dont les variations d'amplitude dépassent les 100 dB à des amplificateurs linéaires ou des convertisseurs analogique-numérique (CAN) avec des plages dynamiques typiques de 60 à 100 dB ? Les signaux de ce type se produisent dans les dispositifs de télémétrie par écho comme les radars et les sonars, les systèmes de communication, ainsi que les systèmes à fibre optique. Dans ces systèmes, un gain élevé est nécessaire pour les signaux à faible amplitude, et un gain faible est nécessaire pour les signaux à amplitude élevée.

Existe-t-il un moyen d'effectuer une mise à l'échelle dynamique de ces signaux afin d'éviter la perte de signal à l'extrémité inférieure et la limitation ou l'écrêtage à l'extrémité supérieure de la plage d'amplitudes ?

L'amplificateur logarithmique, également appelé convertisseur logarithmique, permet de résoudre ce problème en fournissant un gain élevé pour les signaux de faible niveau et en réduisant progressivement le gain pour les signaux plus élevés.

Cet article présente et décrit plusieurs types d'amplificateurs logarithmiques, à la fois pour des applications basse fréquence et haute fréquence. Il aborde ensuite les spécifications et applications typiques de ces amplificateurs non linéaires très utiles.

Rôle des amplificateurs logarithmiques

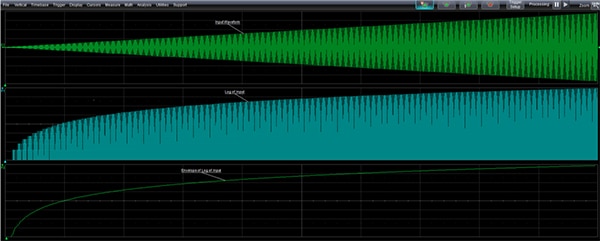

Les amplificateurs logarithmiques sont des amplificateurs analogiques non linéaires qui produisent une sortie représentant le logarithme du signal d'entrée ou l'enveloppe du signal. Ils compressent les signaux d'entrée présentant une vaste plage dynamique en signaux de sortie avec une plage d'amplitudes fixe. Cette opération est réalisée en fournissant un gain élevé pour les faibles niveaux de signal d'entrée et un gain progressivement réduit pour les signaux de niveau plus élevé (Figure 1).

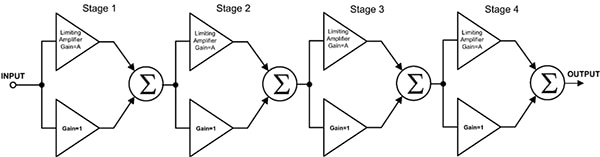

Figure 1 : L'amplificateur logarithmique compresse le signal d'entrée (tracé du haut) en appliquant un gain plus élevé aux signaux présentant la plus faible amplitude, et un gain progressivement réduit aux signaux de niveau plus élevé. Le tracé du milieu montre le logarithme de l'entrée, tandis que le tracé du bas correspond à l'enveloppe de la sortie de l'amplificateur logarithmique. (Source de l'image : DigiKey Electronics)

Le signal d'entrée (tracé du haut) est un porteur modulé en amplitude. Le signal de modulation est une rampe linéaire. La sortie de l'amplificateur logarithmique (tracé du milieu) fournit un gain plus élevé pour les signaux de faible niveau et un gain progressivement réduit à mesure que le niveau du signal augmente, ce qui produit un signal de sortie pondéré de façon logarithmique. Le tracé du bas correspond à l'enveloppe de la sortie de l'amplificateur logarithmique, qui est une option de sortie pour un amplificateur logarithmique de type détecteur. Un amplificateur logarithmique appliqué avant un CAN compresse le signal d'entrée pour l'adapter à la plage d'entrée fixe du CAN.

Topologies d'amplificateur logarithmique

Il existe deux topologies d'amplificateur logarithmique distinctes : l'amplificateur logarithmique à plusieurs étages et l'amplificateur logarithmique CC. L'amplificateur logarithmique à plusieurs étages dépend d'une limitation séquentielle dans une série d'amplificateurs. Cette topologie est utilisée le plus souvent avec des signaux haute fréquence jusqu'à plusieurs gigahertz et se trouve généralement dans les radars et les applications de communication.

L'amplificateur logarithmique CC utilise une diode ou un transistor monté en diode dans la boucle de rétroaction d'un amplificateur opérationnel. Ce type d'amplificateur logarithmique est limité à des fréquences inférieures à 20 MHz. Les amplificateurs utilisant cette technologie sont généralement utilisés avec des capteurs dans les applications de commande.

Amplificateur logarithmique à plusieurs étages

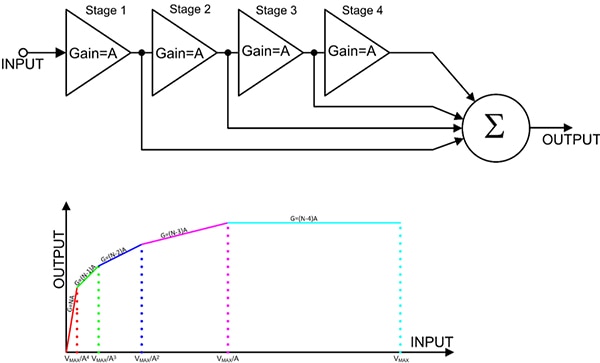

Avec les amplificateurs logarithmiques à plusieurs étages, une réponse d'amplitude logarithmique est obtenue à l'aide d'une série d'amplificateurs linéaires avec des caractéristiques de limitation de surcharge adaptées, la sortie de chacun d'eux actionnant l'étage suivant ainsi qu'un circuit sommateur (Figure 2).

Figure 2 : Modèle conceptuel simple de plusieurs amplificateurs linéaires connecté en série, avec sommation des sorties individuelles (en haut). Cette approche génère une réponse d'amplitude logarithmique comme le montre le tracé de la fonction de transfert (en bas). (Source de l'image : DigiKey Electronics)

La chaîne d'amplificateurs illustrée à la Figure 2 utilise quatre amplificateurs, présentant chacun le même gain A. Les signaux de faible amplitude (en dessous du niveau entraînant une limitation à n'importe quel étage) montrent un gain de N × A (soit 4 × A dans le cas présent). Ce résultat est illustré dans la fonction de transfert en bas de la Figure, où le segment le plus à gauche (en rouge) présente un gain égal à N × A tel qu'indiqué par la pente du segment de ligne pour des amplitudes entre zéro et VMAX/A4, où VMAX correspond à la tension d'entrée maximale.

À mesure de l'augmentation du niveau d'entrée, le dernier amplificateur (étage 4) commence à un certain moment à procéder à une limitation. Le gain global chute alors à (N-1) × A, soit ici 3 × A. La pente du segment vert, entre les niveaux d'entrée VMAX/A3 et VMAX/A4, représente cette plage de gains. De même, à mesure que le niveau d'entrée continue à augmenter, les amplificateurs des étages précédents commencent successivement à procéder à une limitation. Le gain du segment bleu foncé équivaut à (N-2) × A, le segment magenta présente un gain de (N-3) × A et le gain du segment bleu clair est de (N-4) ×A donc zéro.

Si ce modèle conceptuel est utile pour expliquer la façon dont une réponse logarithmique est développée à l'aide d'une série d'amplificateurs, il présente tout de même un problème. Il existe un temps de propagation inhérent associé à chaque étage d'amplificateur. Les composants du signal provenant du premier étage atteignent le circuit sommateur avant ceux des étages ultérieurs, ce qui provoque une distorsion de la forme d'onde de sortie. Cela peut être corrigé en modifiant le circuit de base (Figure 3).

Figure 3 : La topologie d'amplificateurs logarithmiques en série peut être modifiée afin d'éliminer le décalage à l'aide d'une architecture en cascade avec des paires d'amplificateurs. Chaque paire est constituée d'un amplificateur limiteur pour fournir un gain si nécessaire, et d'un tampon gain unité pour les cas où aucune amplification n'est requise. La sommation se produit à chaque étage, ce qui élimine les décalages. (Source de l'image : DigiKey Electronics)

Cette topologie remplace les amplificateurs à un seul étage par des paires d'amplificateurs. Chaque paire est constituée d'un amplificateur limiteur pour fournir un gain si nécessaire, et d'un tampon gain unité si aucun gain n'est requis. La sommation se produit à chaque étage, ce qui élimine le décalage occasionné lors de l'utilisation d'un seul sommateur. Pour les petits signaux, les amplificateurs limiteurs fournissent le trajet dominant. À mesure que l'amplitude du signal augmente, le dernier étage commence à procéder à une limitation, ce qui permet à l'amplificateur gain unité de cet étage de devenir l'entrée dominante vers le sommateur. Si le niveau d'entrée continue d'augmenter, les étages précédents procèdent à une limitation de façon successive, ce qui entraîne une réduction générale du gain.

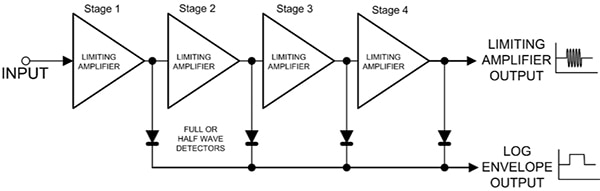

L'amplificateur logarithmique à détections successives (Figure 4) constitue une variante de la topologie d'amplificateurs en série.

Figure 4 : L'amplificateur logarithmique à détections successives ajoute une détection de crête après chaque étage. Ces sorties sont ensuite additionnées pour créer l'enveloppe d'amplitude des signaux de sortie de l'amplificateur logarithmique. (Source de l'image : DigiKey Electronics)

L'amplificateur logarithmique à détections successives utilise la même chaîne d'amplificateurs limiteurs que celle décrite précédemment, mais ajoute une détection de crête après chaque étage. Ces sorties de détecteur sont additionnées pour créer l'enveloppe d'amplitude de la sortie de l'amplificateur logarithmique. Certaines versions produisent également des signaux d'amplificateur logarithmique. Des détecteurs peuvent être implémentés sous forme de demi-onde ou d'onde pleine, en fonction de la conception du circuit. L'enveloppe logarithmique est utile dans les applications qui nécessitent l'extraction du niveau de signal détecté. Ces applications incluent les commandes automatiques de gain et les indicateurs d'intensité du signal de récepteur (RSSI).

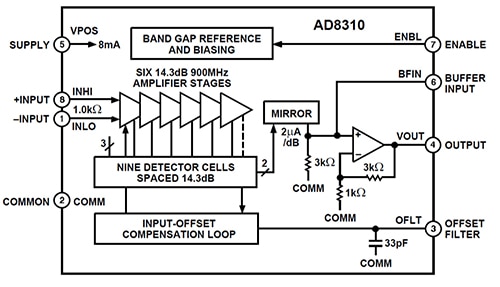

L'AD8310ARMZ-REEL7 d'Analog Devices (Figure 5) est un bon exemple d'amplificateur logarithmique de démodulation à plusieurs étages disponible dans le commerce.

Figure 5 : L'amplificateur logarithmique de démodulation à plusieurs étages AD8310 intègre six amplificateurs en cascade, qui présentent chacun un gain nominal de 14,3 dB (gain de 5,2) et une bande passante de 900 MHz. (Source de l'image : Analog Devices)

L'AD8310 présente une entrée différentielle dotée d'une plage dynamique de 95 dB sur une bande passante de 440 MHz, avec une linéarité logarithmique de ±0,4 dB. Il intègre six amplificateurs en cascade, qui présentent chacun un gain nominal de 14,3 dB (gain de 5,2) et une bande passante de 900 MHz. Chaque amplificateur commande un détecteur présentant une sortie de courant qui est convertie en une tension par un amplificateur séparateur interne, puis en sortie.

Amplificateur logarithmique CC

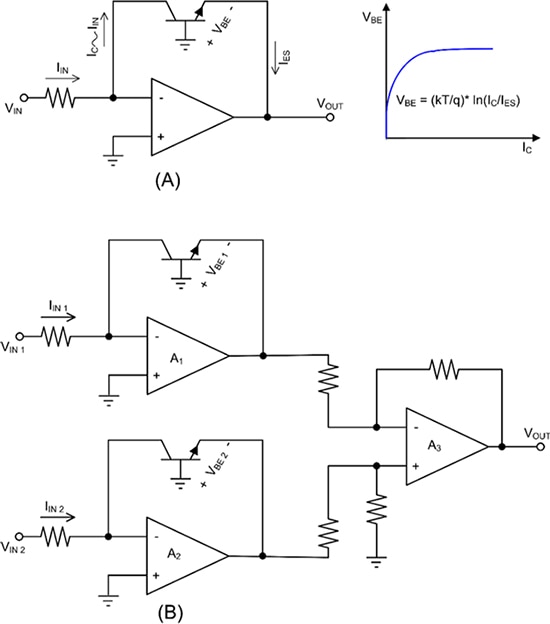

Comme il a été mentionné, il existe une autre topologie d'amplificateur logarithmique, à savoir l'amplificateur logarithmique CC. Cette topologie utilise une diode ou un transistor monté en diode dans le trajet de rétroaction d'un amplificateur opérationnel. Le transistor monté en diode est la configuration la plus couramment utilisée (Figure 6A). La tension au niveau de la jonction base-émetteur du transistor est proportionnelle au logarithme du courant qui le traverse. Lorsque le transistor monté en diode est placé sur le trajet de rétroaction d'un amplificateur opérationnel, cela génère une tension de sortie qui est proportionnelle au logarithme du rapport entre le courant d'entrée et le courant de saturation de l'émetteur (IES).

Figure 6 : Un amplificateur logarithmique peut être créé à l'aide d'un transistor monté en diode sur le trajet de rétroaction d'un amplificateur opérationnel (A). La dépendance à la température de ce type d'amplificateur logarithmique est considérablement réduite en utilisant deux amplificateurs de ce type, connectés de manière différentielle (B). (Source de l'image : DigiKey Electronics)

La configuration simple illustrée à la Figure 6(A) présente une limite du fait que sa sortie dépend de la température, comme l'indique l'équation, où T correspond à la température en kelvin, et du courant de saturation de l'émetteur, IES. En configurant deux amplificateurs de ce type en tant que paire différentielle, comme l'indique la Figure 6(B), cette dépendance peut être considérablement réduite. La version différentielle est un amplificateur d'adaptation d'impédance qui calcule le logarithme du rapport IIN 2/IIN 1 et présente une sortie de tension. La valeur IIN 1 est généralement définie comme un courant de référence fixe.

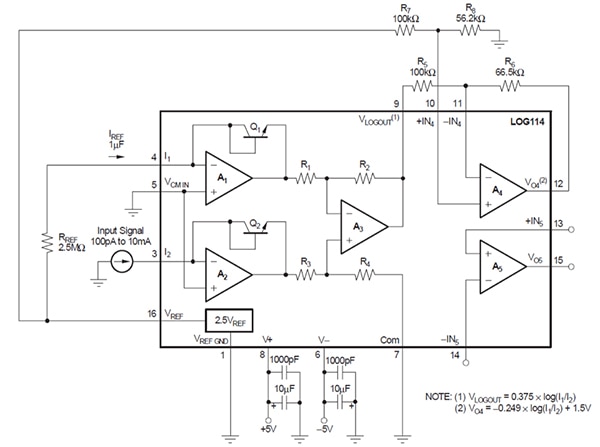

Le LOG114AIRGVT de Texas Instruments est un amplificateur logarithmique CC présentant une plage dynamique jusqu'à 8 décades avec une bande passante de 5 MHz. Il peut être configuré comme un amplificateur logarithmique ou comme un amplificateur de rapport logarithmique. En plus de l'amplificateur logarithmique avec compensation de la température, il inclut deux amplificateurs opérationnels de mise à l'échelle et une source de référence de tension de 2,5 V (Figure 7).

Figure 7 : Schéma fonctionnel et composants externes associés de l'amplificateur logarithmique LOG114. L'amplificateur est basé sur un circuit avec compensation de la température et inclut deux amplificateurs de mise à l'échelle supplémentaires. (Source de l'image : Texas Instruments)

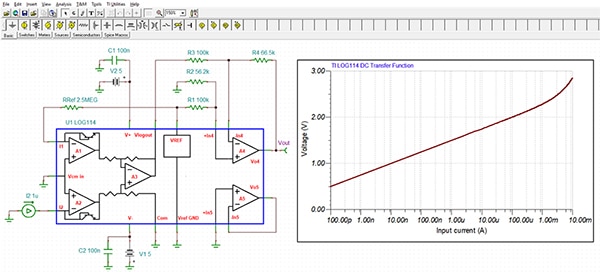

Texas Instruments propose un modèle de circuit pour le LOG114, ce qui permet aux concepteurs de réaliser une simulation de leurs conceptions sur le simulateur de circuit TINA-TI de Texas Instruments (Figure 8).

Figure 8 : La simulation avec TINA-TI du modèle d'amplificateur logarithmique LOG114 montre une excellente linéarité logarithmique sur sept décades de courant d'entrée. (Source de l'image : DigiKey Electronics)

Ce circuit utilise la référence de tension intégrée de 2,5 V pour établir le courant de référence I1 à 1 µA. La fonction de transfert qui l'accompagne montre une réponse linéaire sur 7 décades, de 100 pA à 1 mA, soit une plage de courants de 140 dB. La sortie de l'amplificateur logarithmique est mise à l'échelle à l'aide de l'un des deux amplificateurs opérationnels supplémentaires pour produire une équation de fonction de transfert : VOUT = -0,249 x log (I1/I2) + 1,5 V.

Conclusion

Les amplificateurs logarithmiques offrent au concepteur une technique pour gérer les signaux à vaste plage dynamique, qu'il s'agisse de signaux dans la bande de base ou de signaux RF. Pour ce faire, ils compressent un signal à vaste plage dynamique en une plage de sortie fixe, ce qui permet d'éviter les conditions de dépassement de capacité ou d'écrêtage dans les étages suivants. Il existe différentes solutions d'amplificateurs logarithmiques, souvent prises en charge par des outils de simulation en ligne pour simplifier le processus de conception.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.