Créer rapidement des horloges haute fréquence à faible gigue à l'aide d'un module de boucle de transposition

Avec la contribution de Rédacteurs nord-américains de DigiKey

2021-08-04

Les concepteurs de systèmes d'instrumentation et de mesure ont besoin de signaux à faible gigue et sans parasites afin de fournir les rapports signal/bruit (SNR) ou les vecteurs d'erreur (EVM) requis pour répondre aux exigences de plus en plus élevées des clients. Dans le même temps, ils sont soumis à une forte pression pour réduire l'empreinte carte, ainsi que les coûts de conception et la complexité. Ce dernier point est essentiel pour réduire le temps de développement et respecter les délais de commercialisation de plus en plus courts.

Pour répondre aux nombreux défis posés par les applications, les ingénieurs doivent faire évoluer leurs solutions d'instrumentation et de mesure, de conceptions personnalisées traditionnellement discrètes vers des solutions plus intégrées. Une étape importante dans ce sens consiste à utiliser une boucle à verrouillage de phase (PLL) de transposition intégrée. Cela permet d'élever la fréquence d'un signal d'oscillateur commandé en tension (VCO) traditionnel, tout en maintenant sensiblement la gigue et le bruit de phase d'un oscillateur local (LO) externe fixe.

Cet article traite du rôle des boucles de transposition pour atteindre le plus faible bruit de phase intégré de l'industrie. À titre d'exemple, il présente le système en boîtier de boucle de transposition (TL SiP) ADF4401A d'Analog Devices et montre comment il répond aux exigences de performances via un signal de sortie avec une capacité de gigue intégrée large bande inférieure à 10 femtosecondes (fs) RMS et un isolement amélioré pour atténuer les composants parasites, tout en répondant aux besoins des concepteurs en matière d'intégration, de coût, de complexité et de délai de commercialisation.

Fonctionnement d'une PLL traditionnelle par rapport à une boucle de transposition

L'objectif principal d'une boucle de transposition est de générer un signal de sortie verrouillé vers un signal de référence d'entrée avec un bruit de phase intrabande considérablement réduit par rapport aux PLL traditionnelles.

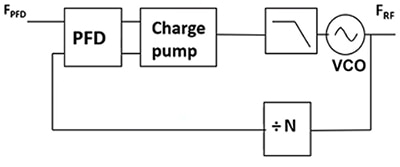

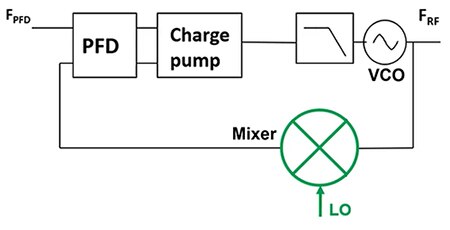

Une PLL standard consiste en un système de rétroaction contenant un détecteur de phase-fréquence (PFD), une pompe à charge, un filtre passe-bas (LPF), un VCO et un diviseur de fréquence de rétroaction N (Figure 1).

Figure 1 : La PLL standard se verrouille sur une référence de fréquence (FPFD) inférieure et génère une fréquence de sortie (FRF). (Source de l'image : Bonnie Baker)

Figure 1 : La PLL standard se verrouille sur une référence de fréquence (FPFD) inférieure et génère une fréquence de sortie (FRF). (Source de l'image : Bonnie Baker)

Le PFD compare la phase de la référence d'entrée et la phase du signal de retour, et génère une série d'impulsions proportionnelles à l'erreur de phase entre elles. La pompe à charge reçoit les impulsions PFD et les convertit en impulsions de source ou d'absorption de courant qui, à leur tour, accordent le VCO en fréquence. Le filtre passe-bas supprime toute l'énergie haute fréquence des impulsions et les convertit en une tension que le VCO peut utiliser. Le signal de sortie du VCO est réinjecté dans le bloc PFD par le biais du diviseur N pour terminer la boucle.

La fonction de transfert de fréquence de la Figure 1 est calculée à l'aide de l'Équation 1 :

![]() Équation 1

Équation 1

Où FRF est la fréquence de sortie

N est le rapport du diviseur de rétroaction (nombre entier ou fractionnaire)

FPFD est la fréquence PFD

Le bruit de fond intrabande de la Figure 1 est calculé à l'aide de l'Équation 2 :

![]() Équation 2

Équation 2

Où FOMPLL est le facteur de mérite (FOM) du bruit de fond de phase intrabande de la PLL

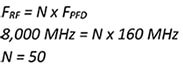

Prenons un exemple avec un facteur de mérite de bruit de fond de phase intrabande de -234 décibels par Hertz (dB/Hz), une fréquence PFD (FPFD) de 160 mégahertz (MHz), et une fréquence de sortie (FRF) de 8 gigahertz (GHz).

Pour ce système, l'Équation 1 est utilisée pour calculer la valeur de N :

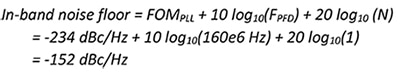

L'Équation 2 est utilisée pour calculer le bruit de fond intrabande :

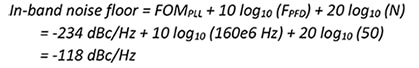

Dans le calcul ci-dessus, le diviseur N contribue fortement au bruit de fond intrabande global, avec 20 log10 (50), soit 34 dB. Une valeur N plus petite permettrait de diminuer le bruit de fond intrabande, mais réduirait également la fréquence de sortie. Alors comment générer une fréquence de sortie élevée et conserver un gain de boucle (N) inférieur ?

Figure 2 : Pour une PLL standard dans cet exemple, le bruit du diviseur de rétroaction (20 log10(N)) présente un bruit intrabande supérieur de 34 dB par rapport au tracé jaune du bas où N = 1. (Source de l'image : Bonnie Baker)

Figure 2 : Pour une PLL standard dans cet exemple, le bruit du diviseur de rétroaction (20 log10(N)) présente un bruit intrabande supérieur de 34 dB par rapport au tracé jaune du bas où N = 1. (Source de l'image : Bonnie Baker)

La solution à ce problème consiste à remplacer le diviseur N par un étage mélangeur abaisseur (Figure 3).

Figure 3 : Une boucle de transposition utilise un mélangeur pour abaisser la fréquence VCO à la fréquence PFD au lieu d'utiliser un diviseur de rétroaction traditionnel. (Source de l'image : Bonnie Baker)

Figure 3 : Une boucle de transposition utilise un mélangeur pour abaisser la fréquence VCO à la fréquence PFD au lieu d'utiliser un diviseur de rétroaction traditionnel. (Source de l'image : Bonnie Baker)

Dans la Figure 3, le mélangeur remplace le diviseur N de rétroaction, résultant en un gain de boucle égal à 1 (N = 1). Cette opération diminue considérablement la contribution de la boucle de rétroaction au bruit de fond intrabande. Pour le calcul du bruit intrabande, la valeur de N est maintenant égale à 1. En utilisant l'Équation 2, le bruit de fond intrabande pour le système modifié est le suivant :

Le nouveau bruit intrabande montre une amélioration de 34 dBc/Hz.

Dans la Figure 3, le mélangeur dépend d'un oscillateur local à bruit extrêmement faible, appelé oscillateur local de décalage. FLO ±FRF doit être égal à FPFD pour atteindre le verrouillage.

Avec l'architecture de boucle de transposition, le bruit de phase de l'oscillateur local de décalage est très important pour obtenir les meilleures performances à la sortie RF. C'est pourquoi les ingénieurs conçoivent généralement un oscillateur local à décalage basé sur des oscillateurs à ondes acoustiques de surface (SAW) commandés en tension (VCSO), des générateurs de spectres en peigne, ou des oscillateurs à résonateur diélectrique (DRO). REMARQUE : Pour obtenir de l'aide pour la conception d'un oscillateur local à décalage, contactez Analog Devices.

Les défis de la boucle de transposition

Traditionnellement, la conception d'une boucle de transposition à faible bruit implique la mise en œuvre de nombreux blocs de circuits, ce qui se traduit par une conception complexe, généralement grande, et à la flexibilité limitée. En outre, l'ensemble du circuit doit être validé et caractérisé pour le fonctionnement cible. Par exemple, l'un des principaux problèmes de conception est la fuite de l'oscillateur local (isolement oscillateur local vers RF) vers le signal de sortie RF. Il s'agit là d'un défi important à relever pour les ingénieurs. Avec les conceptions traditionnelles, les ingénieurs procèdent généralement à de multiples itérations de conception pour obtenir des performances optimales et un isolement approprié.

La Figure 3 montre comment l'ADF4401A intègre les principaux blocs de circuits pour fournir une solution entièrement caractérisée, et élimine les zones traditionnellement difficiles liées aux performances et à l'isolement dans les conceptions de boucles de transposition. Cette solution programmable permet aux ingénieurs d'atteindre des performances optimisées dès le début et de réduire les délais de commercialisation.

Évaluation de l'ADF4401A

L'ADF4401A est conçu pour aider les ingénieurs à réduire le temps de commercialisation d'une instrumentation hautes performances, en utilisant une solution de génération de fréquence avec une bande passante RF de 62,5 MHz à 8 GHz. Grâce à l'utilisation d'un mélangeur à conversion descendante, l'ADF4401A présente un très faible bruit intrabande avec une gigue large bande de ~9 fs intégrée de 100 Hz à 100 MHz. Les techniques de conception et de configuration de l'ADF4401A permettent d'obtenir une plage dynamique sans parasites typique de 90 dBc. La taille du boîtier de 18 millimètres (mm) x 18 mm x 2,018 mm réduit considérablement l'espace sur la carte par rapport à une conception discrète traditionnelle.

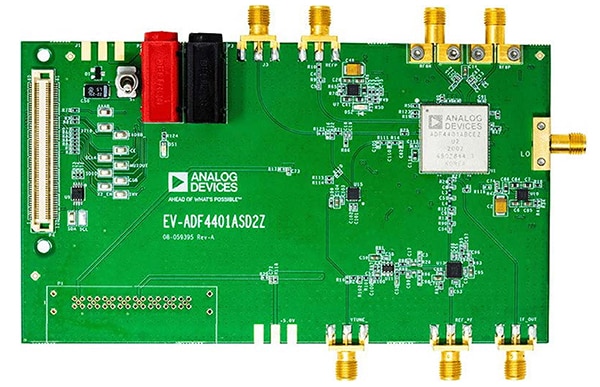

Pour évaluer les performances du dispositif, les concepteurs peuvent utiliser la carte d'évaluation EV-ADF4401ASD2Z (Figure 4). La carte inclut une boucle de transposition complète, incluant un PFD externe (HMC3716), un filtre actif (LT6200) et un multiplexeur (ADG1609).

Figure 4 : La carte d'évaluation EV-ADF4401ASD2Z pour le module de boucle de transposition ADF4401A inclut un PFD externe, une interface USB et des régulateurs de tension. (Source de l'image : Analog Devices)

Figure 4 : La carte d'évaluation EV-ADF4401ASD2Z pour le module de boucle de transposition ADF4401A inclut un PFD externe, une interface USB et des régulateurs de tension. (Source de l'image : Analog Devices)

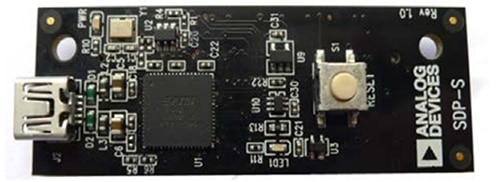

L'EV-ADF4401ASD2Z inclut le TL-SiP ADF4401A avec VCO intégré, un filtre à boucle (5 MHz), un PFD, une interface USB et des régulateurs de tension. De plus, l'EV-ADF4401ASD2Z requiert la carte contrôleur de plateforme de démonstration système (SDP) (série) (SDP-S) EVAL-SDP-CS1Z (Figure 5). La carte fournit une connexion USB entre un PC et l'EV-ADF4401ASD2Z pour sa programmation. La carte contrôleur n'est pas fournie dans le kit EV-ADF4401ASD2Z.

Figure 5 : La carte contrôleur EVAL-SDP-CS1Z (ou SDP-S) est requise pour fournir une connexion USB entre l'EV-ADF4401ASD2Z et un PC pour la programmation. (Source de l'image : Analog Devices)

Figure 5 : La carte contrôleur EVAL-SDP-CS1Z (ou SDP-S) est requise pour fournir une connexion USB entre l'EV-ADF4401ASD2Z et un PC pour la programmation. (Source de l'image : Analog Devices)

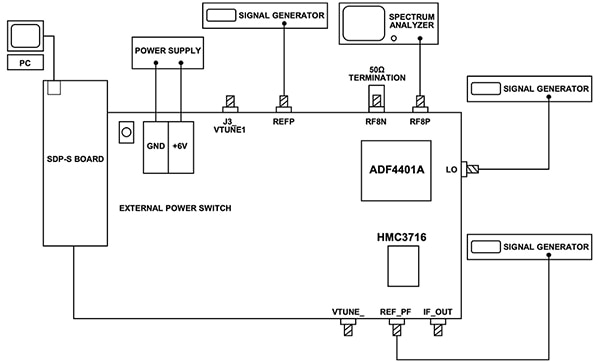

La Figure 6 présente les connexions physiques du système EV-ADF4401ASD2Z. Le logiciel Analysis | Control | Evaluation (ACE) associé contrôle les fonctions TL SiP. L'alimentation est dérivée d'une alimentation externe de 6 volts (V).

Figure 6 : Un schéma de configuration EV-ADF4401ASD2Z montre l'équipement et les connexions nécessaires pour évaluer l'ADF4401A, y compris la carte contrôleur SDP-S, le PC, l'alimentation, les générateurs de signaux et l'analyseur de spectre. (Source de l'image : Analog Devices)

Figure 6 : Un schéma de configuration EV-ADF4401ASD2Z montre l'équipement et les connexions nécessaires pour évaluer l'ADF4401A, y compris la carte contrôleur SDP-S, le PC, l'alimentation, les générateurs de signaux et l'analyseur de spectre. (Source de l'image : Analog Devices)

L'équipement suggéré à utiliser avec cette carte d'évaluation inclut un PC Windows, un analyseur de spectre ou un analyseur de source de signaux, et trois générateurs de signaux.

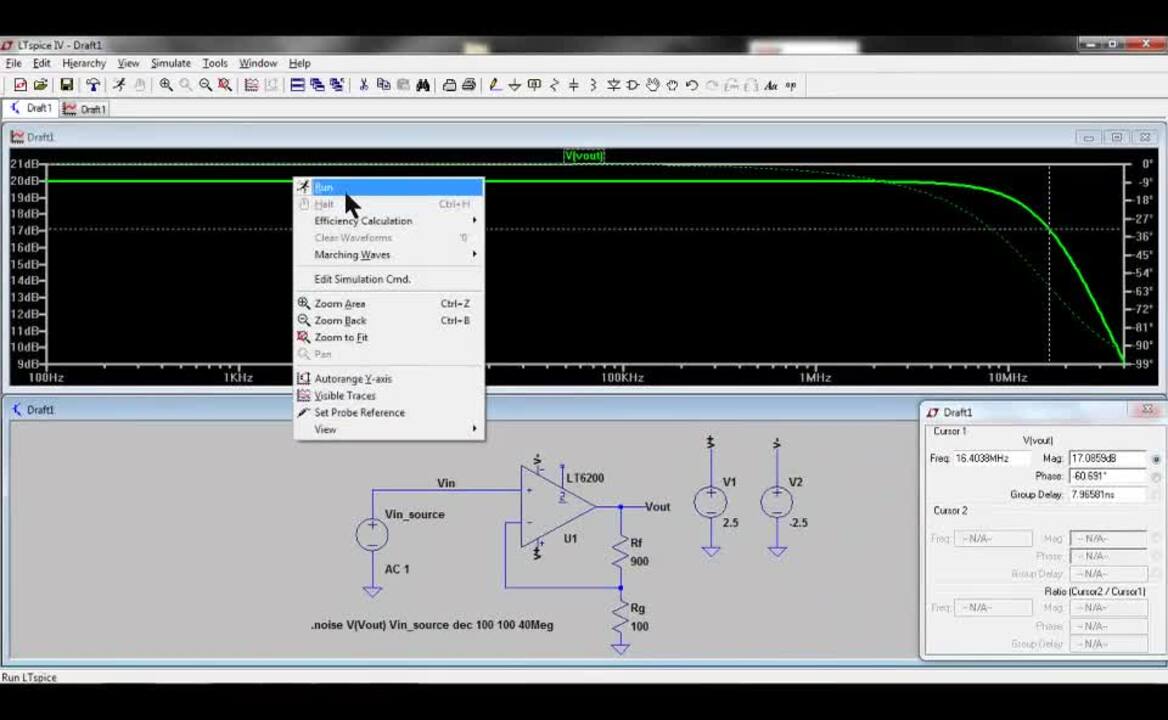

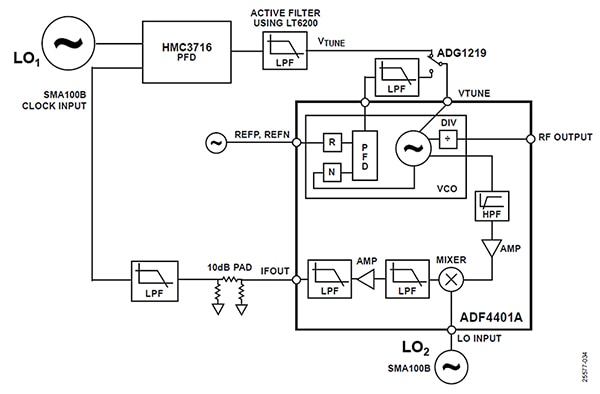

Le schéma fonctionnel de l'EV-ADF4401ASD2Z montre le module ADF4401A, ainsi que le PFD HMC3716, l'amplificateur opérationnel LT6200 et le commutateur SPDT ADG1219 d'Analog Devices (Figure 7).

Figure 7 : Le schéma fonctionnel de la carte d'évaluation EV-ADF4401ASD2Z montre les principaux composants prenant en charge la boucle de transposition ADF4401A. (Source de l'image : Analog Devices)

Figure 7 : Le schéma fonctionnel de la carte d'évaluation EV-ADF4401ASD2Z montre les principaux composants prenant en charge la boucle de transposition ADF4401A. (Source de l'image : Analog Devices)

Il est essentiel d'utiliser un PFD pouvant fonctionner à hautes fréquences, car cela minimise le recours à des diviseurs, qui peuvent dégrader la réponse au bruit intrabande. Grâce à sa tenue en fréquence de comparaison de phase de 1,3 GHz, le HMC3716 d'Analog Devices est idéal pour une utilisation dans la gamme IF de l'ADF4401A. La capacité d'un tel circuit à comparer à la fois la fréquence et la phase élimine le recours à des circuits supplémentaires pour orienter la fréquence vers la fréquence de sortie prévue. Le HMC3716 devient le PFD externe pour terminer la boucle de décalage. La plage de fonctionnement haute fréquence et le bruit de fond de phase ultrafaible du HMC3716 permettent de concevoir des filtres à boucle à large bande passante.

Dans la Figure 7, l'amplificateur opérationnel LT6200 avec une configuration LPF atténue les parasites haute fréquence, tandis que le commutateur ADG1219 complète la boucle de transposition du système.

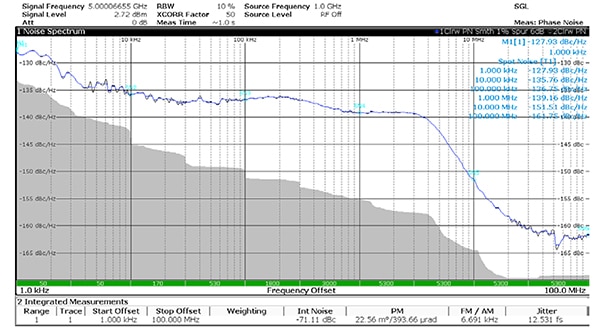

Le dispositif d'évaluation EV-ADF4401ASD2Z crée des tracés de bruit intrabande et des mesures de gigue, comme illustré à la Figure 8.

Figure 8 : Bruit de phase à bande latérale unique à une sortie de 5 GHz, avec une référence HMC3716 externe de 500 MHz et un oscillateur local externe à 4,5 GHz. (Source de l'image : Analog Devices)

Figure 8 : Bruit de phase à bande latérale unique à une sortie de 5 GHz, avec une référence HMC3716 externe de 500 MHz et un oscillateur local externe à 4,5 GHz. (Source de l'image : Analog Devices)

Dans la Figure 8, l'entrée HMC3716 et LO2 est un générateur de signaux hyperfréquences et RF SMA100B. Le bruit intrabande LO2 de la carte d'évaluation est d'environ -135 dBc/Hz, apparent à de faibles décalages jusqu'à 300 kHz. Le filtre à boucle, le PFD HMC3716, le module ADF4401A et LO2 contribuent à un bruit intrabande d'environ -140 dBc/Hz. Le bruit de phase interne apparaît entre 5 MHz et 50 MHz, et le bruit de fond de phase du dispositif est d'environ -160 dBc/Hz. Ensemble, ils donnent une valeur de gigue efficace de 12,53 fs au total.

Conclusion

Les systèmes d'instrumentation haute vitesse exigent des horloges à gigue extrêmement faible pour garantir que les données de sortie ne sont pas compromises. Le défi pour les ingénieurs est de trouver les dispositifs appropriés permettant de créer un système d'horloge gigahertz à haute vitesse. La boucle de transposition ADF4401A simplifie considérablement la sélection des dispositifs pour concevoir le système d'horloge, en fournissant un module compact qui garantit une faible gigue à plus hautes fréquences, tout en réduisant l'espace carte, les coûts et les délais de mise sur le marché.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.