Garantir l'intégrité des données de capteurs grâce à l'auto-interrogation et à l'auto-diagnostic

Avec la contribution de Rédacteurs nord-américains de DigiKey

2019-03-29

Les technologies de capteur et de Internet des objets (IoT) étendent rapidement leur présence dans les environnements industriels, commerciaux et même grand public. Cette expansion s'accompagne d'un besoin croissant de s'assurer de l'intégrité des données provenant des capteurs associés et de leurs circuits d'interface d'entrée.

Le problème potentiel lié à l'intégrité des données devient d'autant plus sérieux lorsqu'un seul circuit intégré d'interface prend en charge plusieurs capteurs, car un problème avec ce circuit intégré peut corrompre de nombreuses mesures. Cela peut alors entraîner une évaluation incorrecte de la situation détectée et engendrer éventuellement des actions inappropriées, voire dangereuses, du système.

Cet article analyse les diverses sources de défaillances permanentes et temporaires (transitoires), et les inexactitudes de mesures dans la chaîne de signaux du capteur vers le processeur. Il présente ensuite un circuit hautement intégré d'Analog Devices et montre comment l'utiliser pour corriger ces problèmes à l'aide de diagnostics au niveau des capteurs, de lui-même et de ses E/S numériques.

Trajet du signal du capteur vers le processeur

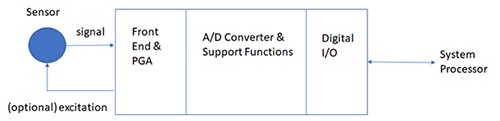

Les facteurs qui affectent au final l'intégrité de la mesure d'un capteur commencent par les trois principaux blocs fonctionnels de la chaîne de signaux illustrée à la Figure 1. Il s'agit des blocs suivants :

- Le capteur et ses sorties

- Le circuit d'entrée analogique dans le circuit intégré de mise en forme des signaux, centré sur le convertisseur analogique-numérique (CAN)

- Les E/S numériques vers le processeur système

Figure 1 : Le trajet de signal de base du capteur vers le processeur est constitué en principe de quelques fonctions de base uniquement, mais un circuit intégré d'interface pratique et utile fournit de nombreuses fonctions et fonctionnalités supplémentaires. (Source de l'image : DigiKey Electronics)

Un système multicanal est souvent constitué d'un mélange de divers types de capteurs, tels que des thermocouples, des capteurs de température à résistance (RTD) et des capteurs de pression. Un capteur peut bien évidemment être défaillant ou présenter des sorties d'interconnexion qui s'ouvrent ou créent un court-circuit avec une sortie adjacente, un rail d'alimentation ou une borne de mise à la terre.

En fonction du type de capteur, une défaillance au niveau de ses fils de sortie peut être visible immédiatement, car la mesure sera « hors échelle ». En revanche, certains modes de défaillance entraînent des signaux inexacts, mais d'apparence normale. En outre, certains capteurs, comme les RTD, ont besoin d'un courant de stimulation externe, qui doit se trouver dans une plage définie pour une mesure valide. Pour ces raisons, il est recommandé de tester non seulement la continuité du trajet du signal entre le capteur et le circuit d'entrée analogique, mais également de vérifier que le signal reste entre les limites minimale et maximale autorisées, de préférence au moyen d'un circuit analogique qui ne risque pas d'être affecté par d'éventuels problèmes de CAN.

Cela permet non seulement d'obtenir des mesures précises, mais également des mesures dans lesquelles les algorithmes de prise de décision du système peuvent être exécutés avec un niveau de confiance très élevé dans les données sources.

Cependant, tous ces contrôles et ces compromis supplémentaires entraînent des composants additionnels, une empreinte plus grande et des délais de conception plus longs.

Un circuit intégré à auto-interrogation assure l'intégrité des données des capteurs

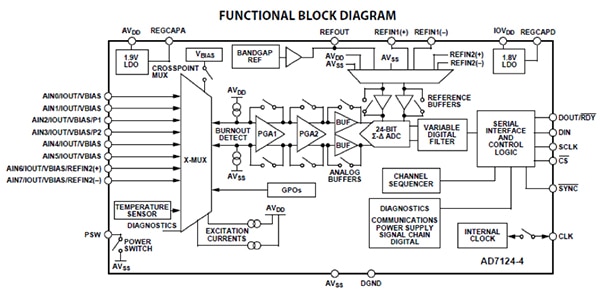

Pour répondre au besoin de données haute intégrité avec un impact minimal sur les délais de conception et l'empreinte, Analog Devices a lancé l'AD7124-8BCPZ-RL7, une solution constituée d'un CAN et d'une interface axés sur le capteur qui va bien au-delà de la mise en forme et de la conversion des signaux de base. Le dispositif inclut plusieurs fonctions de signal et d'autodiagnostic pour assurer l'intégrité des données.

Figure 2 : L'AD7124, qui est constitué d'un CAN et d'une interface axés sur le capteur, va bien au-delà de la mise en forme et de la conversion des signaux de base pour inclure plusieurs fonctions de signal et d'autodiagnostic afin d'assurer l'intégrité des données. (Source de l'image : Analog Devices)

L'AD7124 est un dispositif Sigma-Delta (Σ-Δ) 24 bits à quatre canaux, à faible bruit et basse consommation. Sa fréquence d'échantillonnage varie d'un peu plus de 1 éch./s, ce qui convient à de nombreuses catégories de capteurs et leurs applications, à 19 200 éch./s. À la fréquence d'échantillonnage la plus basse, il consomme 255 microampères (μA). La précision des mesures de ce dispositif est améliorée par l'accent mis sur le faible bruit, avec une valeur efficace inférieure à 25 nanovolts (nV), et par la faible dérive de sa référence de tension interne (10 ppm/°C).

L'AD7124 est disponible dans des boîtiers LFCSP à 32 sorties et TSSOP à 24 sorties. Ses E/S numériques flexibles prennent en charge des interfaces compatibles SPI, QSPI, MICROWIRETM et DSP à 3 et 4 fils.

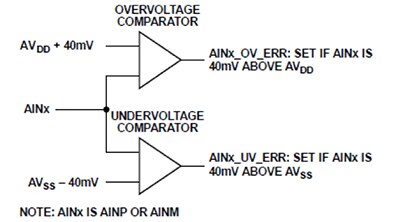

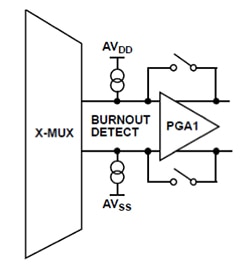

L'AD7124 résout les problèmes de sortie de capteur mentionnés précédemment à l'aide de deux techniques : les alarmes de limite de signal et la détection de courant de claquage. Les alarmes de limite de signal utilisent un moniteur d'alarme de surtension/sous-tension pour vérifier la tension absolue sur chacune des quatre paires de connexions d'entrée analogiques (Figure 3). Cette tension doit se trouver dans une plage définie pour répondre aux spécifications de la fiche technique.

Figure 3 : La vérification de base des sorties d'un capteur à l'aide d'alarmes de limite de signal utilise des comparateurs matériels avec des paramètres minimum/maximum fixes. (Source de l'image : Analog Devices)

La détection du courant de claquage utilise une paire de récepteurs et de sources de courant programmables. En générant et en absorbant une paire de courants prédéfinie au niveau des sorties du capteur, l'AD7124 peut vérifier leur intégrité (Figure 4). Les courants, qui sont entièrement activés ou désactivés, sont commutés vers la paire d'entrées analogiques à tester.

Figure 4 : En générant et en absorbant une paire de courants prédéfinie au niveau des sorties du capteur, l'AD7124 peut vérifier leur intégrité. (Source de l'image : Analog Devices)

Une mesure pleine échelle (ou quasi pleine échelle) peut signifier que le capteur d'entrée est en circuit ouvert. Si la tension mesurée est de 0 V, cela peut indiquer un court-circuit au niveau du transducteur. Un bit indicateur correspondant est défini dans le registre d'erreurs pour indiquer l'occurrence et le type d'erreur.

Enfin, pour les applications où l'utilisateur fournit la référence de manière externe au lieu d'utiliser la référence interne, ce qui est souvent le cas avec les RTD ou les extensomètres, l'AD7124 vérifie que la tension de référence de conversion externe est correcte.

Vérification du circuit d'entrée et du CAN

Bien que les capteurs externes et leurs sorties constituent la principale source de difficultés, il est essentiel de vérifier les performances du circuit intégré d'entrée/de conversion en lui-même. Voici quelques-unes des fonctions qui peuvent être hors spécifications ou entièrement défaillantes :

- La référence de tension interne du CAN

- L'amplificateur à gain programmable (PGA) qui amplifie le signal d'entrée de façon à correspondre avec la portée du CAN pour la résolution la plus élevée

- Le régulateur à faible chute de tension (LDO) qui fournit l'excitation de capteur requise

- Les rails d'alimentation internes du circuit intégré

- Le CAN en lui-même

Pour tester la section analogique de la chaîne de signaux, l'AD7124 fait appel à un test autonome basé sur le matériel et le micrologiciel. Il génère un signal de 20 mV qui peut être connecté en interne à n'importe lequel de ses quatre canaux d'entrée différentiels, puis numérisé. Cette procédure permet de répondre à plusieurs objectifs : cela permet de vérifier le fonctionnement de base du multiplexeur de canal d'entrée et du CAN, mais également d'effectuer une évaluation du PGA en modifiant les paramètres de gain de ce dernier et en vérifiant les mesures de CAN qui en résultent.

Le CAN est également une source de problèmes potentiels. L'AD7124 utilise l'architecture de convertisseur Σ-Δ éprouvée avec son modulateur 1 bit et ses filtres numériques requis. Un test complet des performances du CAN utilise à la fois des techniques analogiques et numériques.

Dans l'AD7124, si la sortie du modulateur contient 20 « 1 » ou 20 « 0 » consécutifs, cela indique que le modulateur présente une saturation sur l'un des rails. Un bit indicateur d'erreur est donc défini. De même, le circuit intégré vérifie que le coefficient de décalage du CAN se trouve entre 0x7FFFF et 0xF80000 après son étalonnage de décalage lancé automatiquement. S'il se trouve en dehors de cette plage, un autre bit indicateur d'erreur est défini. Enfin, pendant un étalonnage pleine échelle, tout dépassement de capacité du filtre numérique définit un autre bit indicateur d'erreur.

Les rails et sources d'alimentation internes et externes constituent également d'éventuelles sources de problèmes. De nombreux capteurs nécessitent une petite quantité de puissance d'excitation, qui est souvent fournie par un petit LDO à faible bruit dans le circuit intégré du circuit d'entrée analogique.

L'AD7124 vérifie les sorties de son LDO de deux façons. Premièrement, la sortie du LDO peut être routée en interne vers le CAN et comparée à sa valeur attendue. Deuxièmement, un comparateur matériel indépendant du CAN surveille en permanence le LDO par rapport à la référence du circuit intégré. Si la valeur passe en dessous d'un seuil prédéfini, un bit indicateur d'erreur est défini. De ce fait, le LDO peut être évalué pendant l'initialisation, mais aussi de façon continue sans utiliser constamment les ressources du processeur.

Pour obtenir un meilleur niveau de confiance, le circuit de test utilisé pour surveiller l'alimentation peut être vérifié (dans une certaine mesure) en connectant son entrée à la terre (tension nominale de 0 V), puis en vérifiant la mesure numérique. L'AD7124 pousse un peu plus loin cette garantie d'intégrité des données en vérifiant que les condensateurs de découplage de 0,1 microfarad (µF) requis sont présents et connectés. Pour ce faire, l'AD7124 déconnecte physiquement le condensateur de découplage via son commutateur interne, puis vérifie la sortie du LDO. Si la tension du LDO chute, cela signifie que le condensateur de découplage est électriquement absent. Cela définit encore une fois un bit indicateur d'erreur.

Chaque circuit intégré présente évidemment une température maximale au-delà de laquelle il devient hors spécifications ou tombe en panne immédiatement. Par conséquent, un capteur est intégré à l'AD7124 pour fournir des mesures de température de la puce à tout moment, avec une précision typique de ±0,5°C.

Qu'en est-il des erreurs numériques ?

Jusque-là, nous avons étudié la manière de veiller aux performances et à la précision du capteur analogique ou des fonctions de conversion. Cependant, dans les environnements industriels aux conditions électriques difficiles où de nombreux capteurs sont déployés, il existe des problèmes liés au bruit, aux interférences électromagnétiques/perturbations radioélectriques et aux transitoires qui affectent les composants électroniques numériques. Par conséquent, il est important de veiller aux performances du circuit numérique interne ainsi qu'à la liaison d'interface vers le processeur du système pour assurer la robustesse des données et de toutes les opérations de lecture/écriture.

Pour ce faire, l'AD7124 adopte une approche multibroche commençant par les opérations et fonctionnalités suivantes :

- Les performances de l'horloge centrale sont vérifiées. L'horloge centrale est requise pour définir le débit de données de sortie, le temps de stabilisation du filtre et les fréquences de rejet du filtre. Ces valeurs sont vérifiées par un registre de comptage indépendant qui peut être lu et relu à tout moment.

- Le nombre d'impulsions SCLK utilisées dans chaque opération de lecture ou d'écriture SPI est vérifié par rapport à un compteur d'horloge spécial. Ce nombre doit être un multiple de huit (toutes les opérations SPI utilisent 8, 16, 32, 40 ou 48 impulsions d'horloge).

- L'AD7124 vérifie que les opérations de lecture et d'écriture concernent uniquement des adresses de registre valides.

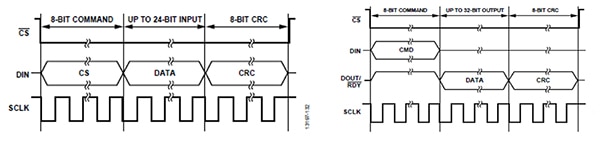

Ces étapes concernent les opérations internes, mais n'assurent pas l'intégrité de l'interface du processeur ni de ses données. Pour fournir un niveau de confiance extrêmement élevé dans les données, l'utilisateur peut indiquer à l'AD7124 d'implémenter un algorithme de somme de contrôle polynomial avec contrôle par redondance cyclique (CRC). La somme de contrôle permet de s'assurer que seules les données valides sont inscrites dans un registre et autorise la lecture des données à partir d'un registre pour être validées (Figure 5). Notez que la somme de contrôle est une technique pour un niveau élevé de confiance qui permet de détecter même des erreurs à un seul bit, mais qui ne peut pas les corriger.

Figure 5 : Une somme de contrôle polynomiale avec contrôle par redondance cyclique (CRC) est ajoutée aux transactions d'écriture SPI (gauche) et aux transactions de lecture SPI (droite) pour la détection d'erreurs à un seul bit. (Source de l'image : Analog Devices)

Lorsque cette opération est réalisée, elle calcule une somme de contrôle sur le bloc de données et l'ajoute à la fin de chaque transaction de lecture et d'écriture. Pour s'assurer que l'écriture dans le registre a bien été effectuée, le registre doit être relu pour comparer la somme de contrôle stockée à celle calculée à partir des données.

Dans un environnement électrique difficile, même la mémoire peut subir des erreurs de bits. Pour fournir une vérification de haut niveau pour ces erreurs dans les registres intégrés, l'AD7124 calcule la somme de contrôle pour une plage d'opérations à chaque fois que l'un des cas de figure suivants se présente :

- Il existe un cycle d'écriture de registre

- Il existe un étalonnage de décalage/pleine échelle

- Le dispositif effectue un seul cycle de conversion et le CAN passe en mode veille après l'exécution de la conversion

- Il sort du mode lecture en continu

Pour obtenir un meilleur niveau de robustesse, la mémoire ROM (lecture seule) interne est également évaluée. Lors de la mise sous tension, tous les registres sont initialisés avec les valeurs par défaut, qui sont stockées dans la mémoire ROM. Un calcul CRC est effectué sur le contenu de la mémoire ROM lors de la mise sous tension. Si la valeur est différente du résultat CRC stocké, cela indique la présence d'au moins une erreur à un seul bit.

L'AD7124 fournit également une excitation pour de nombreux types de capteurs, ainsi que la mise en forme des signaux et la mise à l'échelle du signal de sortie de capteur via des amplificateurs et un PGA. Pour fournir le niveau extrême de robustesse dont il est capable, il possède de nombreux registres internes pour l'initialisation, l'établissement des modes et des paramètres de fonctionnement souhaités, et le signalement de diverses erreurs et défaillances.

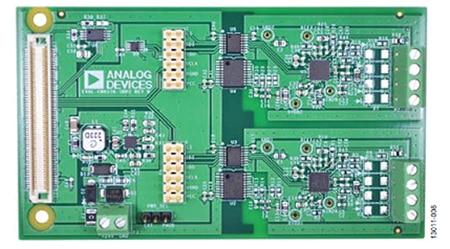

Utilisation de la carte d'évaluation AD7124 pour accélérer les conceptions AD7124

L'AD7124 est un système complexe présentant de nombreuses possibilités de conception et capacités de performances. Il ne s'agit pas d'un simple circuit intégré d'interface de capteur prêt à l'emploi. Pour faciliter l'apprentissage et permettre aux concepteurs de se familiariser rapidement avec ses capacités potentielles, Analog Devices fournit également la carte d'évaluation EVAL-CN0376-SDPZ (Figure 6).

Figure 6 : La carte d'évaluation EVAL-CN0376-SDPZ permet d'accélérer la conception et d'utiliser pleinement les nombreuses fonctionnalités de l'AD7124. (Source de l'image : Analog Devices)

La carte d'évaluation contient l'alimentation et les composants externes nécessaires pour connecter l'AD7124 à divers capteurs réels ainsi qu'à un processeur. Elle est prise en charge par le logiciel d'évaluation CN-0376 basé Windows qui communique via un port USB pour configurer et capturer les données de la carte d'évaluation.

Conclusion

De nombreuses décisions critiques sont prises par des algorithmes avancés, embarqués dans des processeurs système, qui sont maintenant améliorés par l'intelligence artificielle (IA) dans de nombreux cas. Il est plus important que jamais que les données brutes sur lesquelles ces algorithmes se basent pour tirer des conclusions et prendre des mesures présentent un niveau élevé d'intégrité. Les circuits intégrés comme l'AD7124 renforcent la confiance dans les données afin de s'assurer que chaque liaison dans la chaîne de signaux, des sorties et de l'interface du capteur à ses propres performances et fonctions, fonctionne comme prévu et n'est pas corrompue.

Avertissement : les opinions, convictions et points de vue exprimés par les divers auteurs et/ou participants au forum sur ce site Web ne reflètent pas nécessairement ceux de DigiKey ni les politiques officielles de la société.